五、 rom table

在一个soc中,有多个coresight组件,但是软件怎么去识别这些coresight组件,去获取这些coresight组件的信息了?这个时候,就需要靠coresight组件中,一个重要的组件,这个组件就是rom table。

ARM规定,在一个soc中,必须要实现至少1个rom table,该rom table,保存了soc中各个coresight组件的信息,包括组件格式以及组件的基地址。

rom table只会占用一个4K空间大小,也就是PIDR4寄存器的SIZE为0。

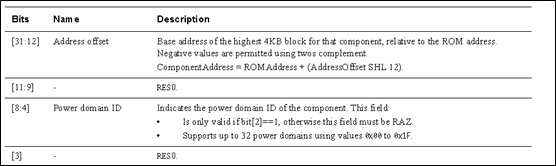

1. entry寄存器

对于rom table,从0x000-0xefc,是entry寄存器。每个entry保存了一个coresight组件的信息。

[31:12]是coresight组件,基于ROM table基地址的偏移地址。例如ROM table的基地址为0x2000_0000,而[31:12]为1, 那么这个coresight组件的基地址就是0x2000_1000。

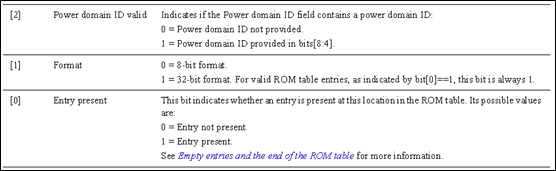

[8:4]和[2]是用来说明该coresight组件所处的power domain。因为一个soc中,有多个power domain,而每个组件可能会处于不同的power domain中。就依靠这两个位域说明。

[1],表示coresight的寄存器的数据有效是8bit,还是32bit。

[0],表示这个entry代表的组件是否有有效的。

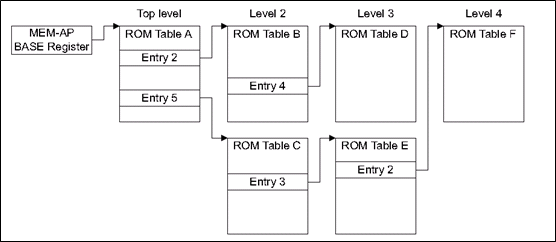

一个rom table中,最多有960个entry,也就是一个rom table中,可以最多保存960个coresight组件的信息,但是在一个entry中,可以指向下一个rom table,这样,就扩展了保存coresight组件信息的个数。

如果rom table的entry没有用完,那最后一个有效的entry后的下一个entry,entry值为全0。

rom table的基地址,保存在DAP的AP的base addr寄存器中,这样debugger通过访问DAP的AP,就可以获取到rom table的基地址,然后在访问rom table,从而获取到整个soc中所有的coresight组件的信息。

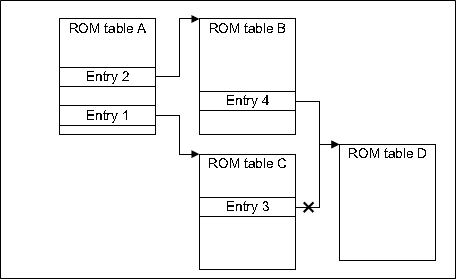

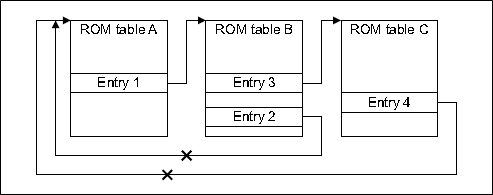

rom table的entry指向,可以理解是一个链表,但是链表中,不能有环。如以下的entry指向是错误的。

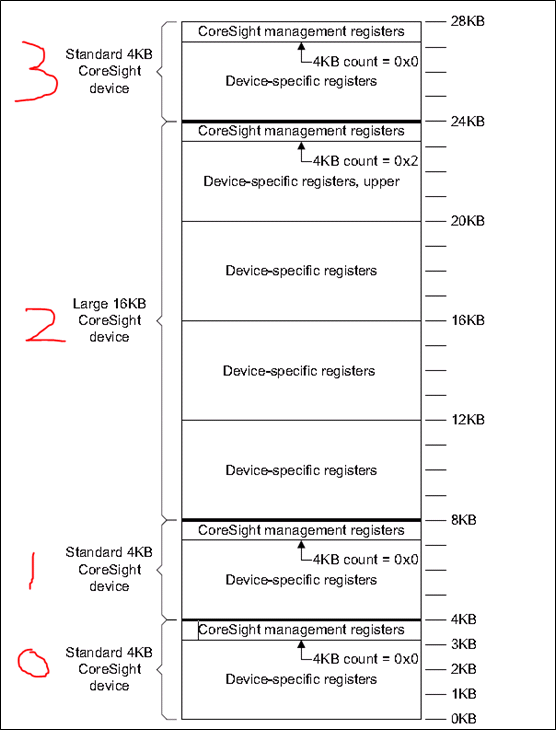

如果一个coresight组件,占用的空间,超过了4K,但coresight有规定,coresight的寄存器,要实现在最后一个4K的最后1K位置,因此rom table中的该coresight组件的基地址,为最后一个4K空间的基地址。

2. 例子

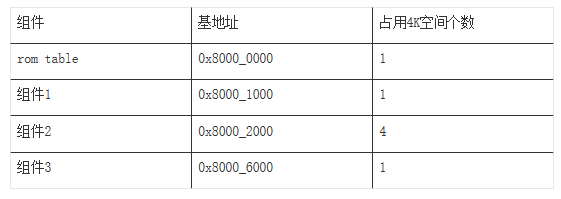

例如如下的coresight系统,共4个组件,假设第一个组件是rom table。假设rom table的基地址是0x8000_0000。

那么:

rom table的基地址,存在DAP的AP的base addr寄存器中,外部通过访问DAP的这个寄存器,获取到rom table的基地址,然后就可以访问rom table各个entry 寄存器的值。

组件1,组件2,组件3的基地址信息,存放在rom table的entry0,entry1,entry2中。

对于组件1,entry0的[31:12]为1,表示组件1的基地址是0x8000_1000,外部根据这个地址,就可以访问这个组件的coresight寄存器,从而获取到这个组件的信息。

对于组件2,因为这个组件,占用了4个4K空间大小,rom table中存放占用最后1个4K空间的基地址,因此entry0的[31:12]为5,表示组件1的基地址是0x8000_5000,外部根据这个地址,就可以访问这个组件的coresight寄存器,从而获取到这个组件的信息。通过读取PIDR4寄存器的SIZE信息,获取到该组件占用4个4K空间,从而反推,可以得到该组件的基地址是0x8000_2000。

对于组件3,entry0的[31:12]为6,表示组件1的基地址是0x8000_6000,外部根据这个地址,就可以访问这个组件的coresight寄存器,从而获取到这个组件的信息。

这样,外部就通过rom table,就可以获取到soc中,所有coresight组件的基地址。有了基地址,就可以对其进行访问。

系列其他篇

原文首发于骏的世界博客

作者:卢骏.

更多Arm技术相关的文章请关注Arm技术博客极术专栏,每日更新。