2017年5月10日,NVIDIA(英伟达)推出Volta架构及对应的Tesla V100数据中心GPU。一年之后,IBM为美国能源部(DOE)建造的超级计算机Summit就在近3万个Tesla V100 GPU的加持下登上TOP500榜单的首位。在这500套(当时)全球最快的高性能计算(High Performance Computing,HPC)系统中,使用加速器的有110套,其中NVIDIA GPU多达98套,接近九成,在前10名中也占据了半壁江山。

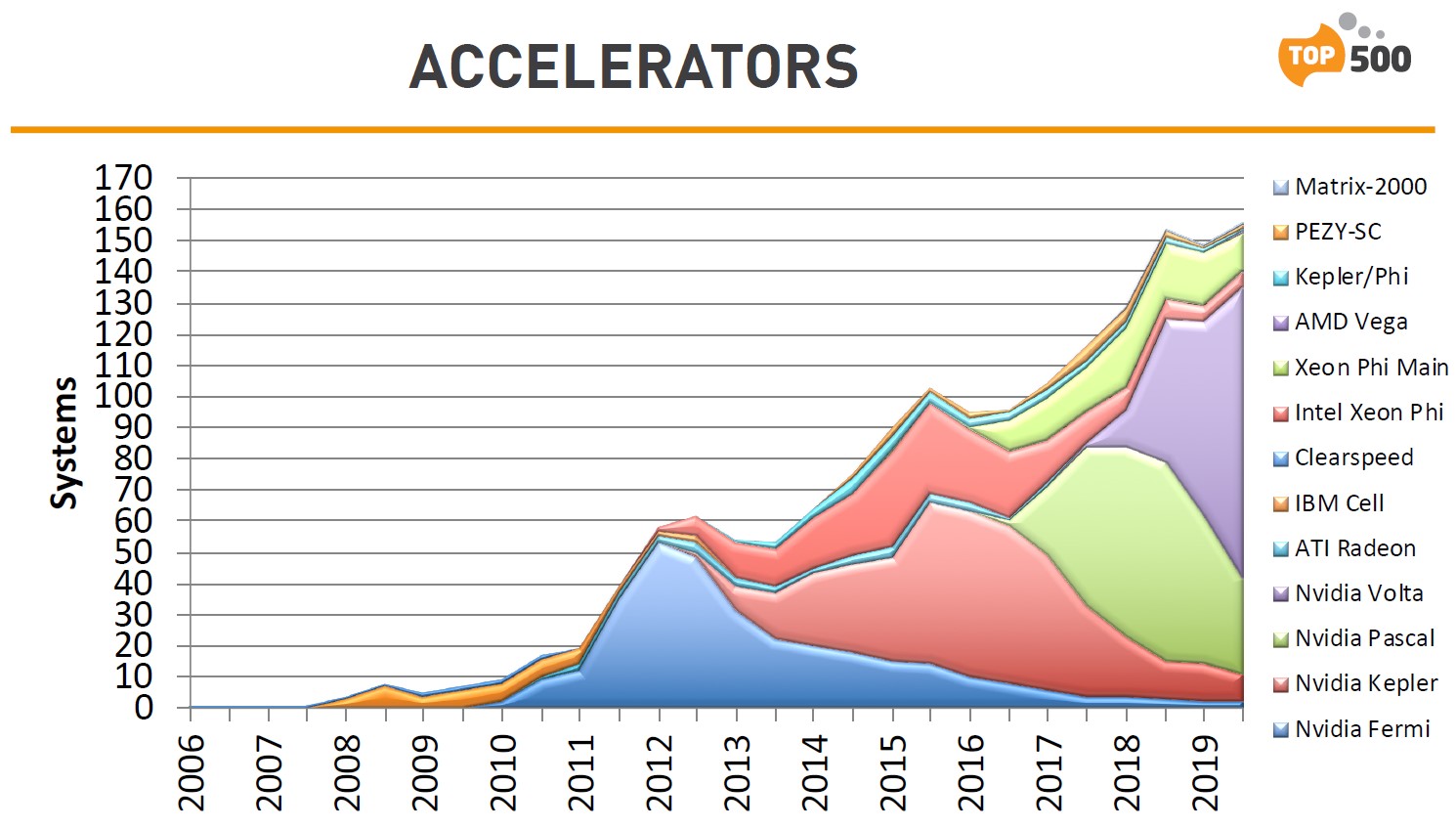

2019年11月,TOP500榜单中使用加速器的系统数量,Volta架构傲视同侪

TOP500榜单每年更新两次,时隔一年半之后,榜单的头名和NVIDIA GPU在前10名中的占比都没变,但是使用加速器或协处理器技术的系统增加到145套:其中基于Volta的多达94套,接近三分之二;使用NVIDIA GPU的系统数量比前一期榜单的加速器方案总和(134套)都多……而在强调单位能效的Green500榜单中,前10名中有8个采用NVIDIA GPU——7个是V100。

如果我们把目光放在TOP500榜单的后100名(401~500),会发现另一个有趣的现象:2018年6月,采用NVIDIA GPU的系统只有15个;2019年11月,仅采用V100的系统就有18套,其中排名第422和494位的两套系统,其节点和互连方案与榜单前两名(美国能源部的Summit和Sierra)如出一辙。

快速占据TOP500榜单的近20%,既“上得厅堂”又“下得厨房”,V100可以说是有史以来最为成功的数据中心GPU。又是在5月,又是在TOP500榜单更新之前,三年后在老黄的厨房“面世”的A100 GPU能否取得更高的成就?

Ampere(安培)架构推出当天,即宣布获得美国和德国的6家超算中心采用,包括DGX A100系统组成的集群,共使用近1.3万个A100 GPU,总算力为:使用64位浮点运算的仿真,峰值性能超过250 PFlops(petaflops);使用混合精度运算的AI推理工作,利用A100 GPU对稀疏性的支持,可以提供惊人的8.07 EFlops(exaflops)。

美国阿贡国家实验室部署首批DGX-A100系统

在(北京时间)昨天夜里公布的第55版TOP500榜单中,酝酿多年的ARM超算系统Fugaku(富岳)终于登上榜首,“仓促上阵”的A100则凭借基于DGX A100 SuperPOD快速搭建起来的Selene斩获第7,而前10名中的另外两个新面孔都基于V100,使得NVIDIA GPU在第一集团中的占比进一步升至六成。

A100的能效表现更为亮眼:Selene在Green500榜单上坐二望一,两者的单位功耗非常接近,但是第一名的规模至少小一个数量级,在TOP500榜单中的排名低至394位。V100也保持了相当高的竞争力——TOP500前10中,采用V100的系统,仅有1套没进入Green500前10。

可以期待,即将到来的E级(Exa-scale)超算时代,前排一定不乏A100的身影。不过,基于Ampere架构的数据中心产品,目光绝不仅限于超算中心,面对蓬勃发展的人工智能、数据分析和云计算市场,NVIDIA给它们赋予的使命是“我全都要!”

平民化:从HPC到ABC

高性能计算可谓计算机界“皇冠上的明珠”,也为合称“ABC”的人工智能(Artificial Intelligence,AI)、大数据(Big Data)、云计算(Cloud Computing)提供了理论依据和实践基础。但是,ABC在应用场景和使用模式上都演化出了自己的特色,HPC也有不同的场景细分,在HPC市场上取得的成功并不能自然复制到那三大市场上。举个比较极端的例子:x86处理器在Top500榜单中占比高达95%,却越来越不被认为是AI基础架构的主角。

A、B、C各有侧重又互有交叉,对基础架构提出的要求时有冲突,譬如:

精度:HPC和AI对计算能力的需求都非常高,但是侧重的方向有较大的区别。典型的科学计算应用对计算精度有很高的要求;AI应用则通常为了更快的得到结果,在满足准确度的前提下选择更低的计算精度,其中训练和推理过程对计算精度的容忍度又有不同。

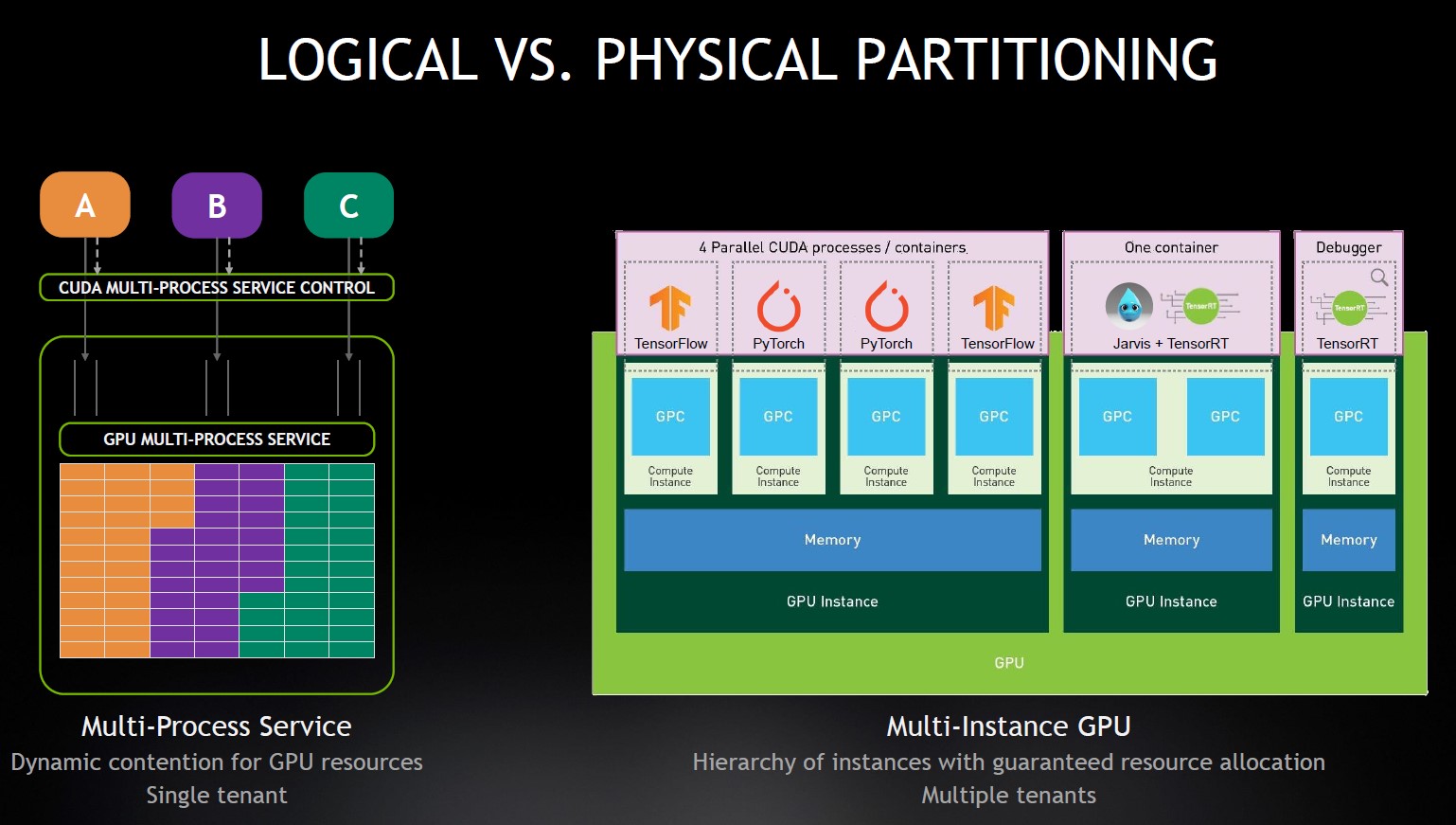

粒度:传统上高性能计算主要致力于将集群作为一个整体来处理一个或几个大型任务,每个物理节点只承担任务的一(小)部分;云计算的商业模式则追求将集群资源灵活的分配给不同用户,一个物理节点切分给多个用户或不同应用是常态。

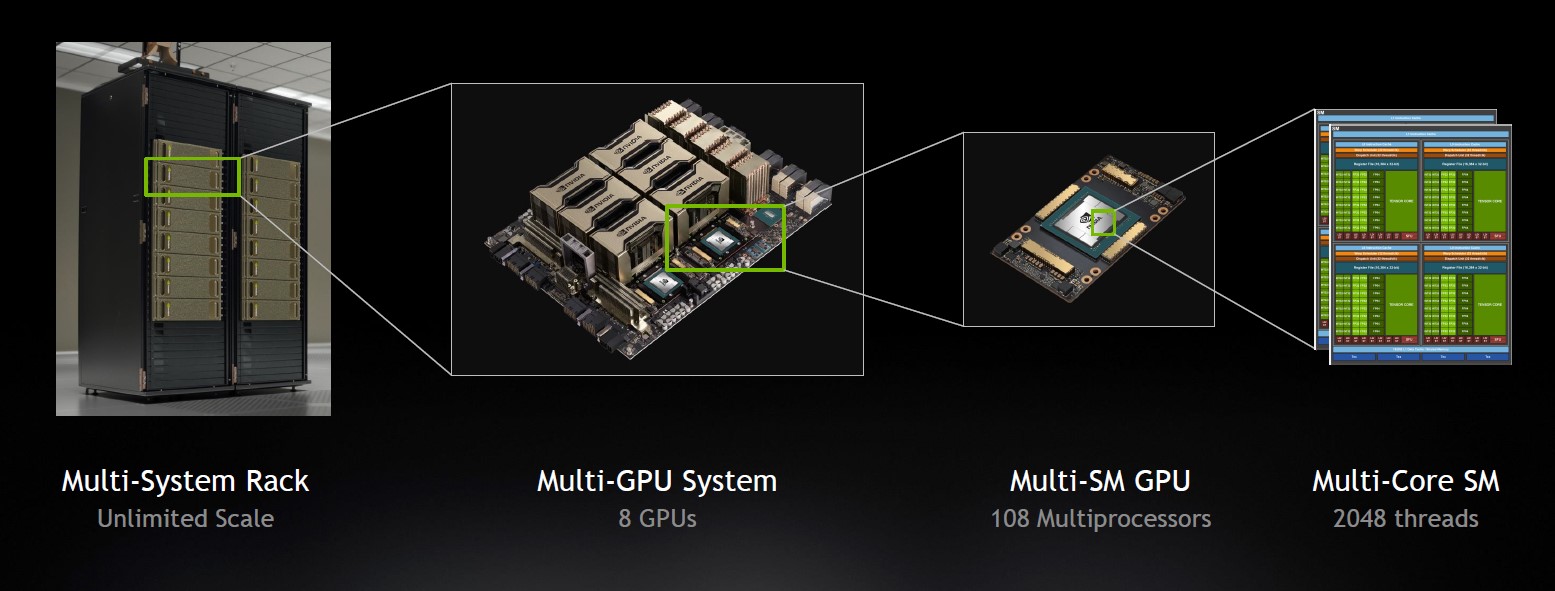

规模的层级和分配的颗粒度

当然,如果基础架构能提供足够的灵活性,鱼与熊掌并非不可兼得。譬如,日本国立先进工业科学技术研究所(AIST)号称世界上第一个大规模开放AI计算基础设施的ABCI(AI Bridging Cloud Infrastructure,人工智能连接云基础设施),在适用于AI的半精度运算中可提供550 PFlops的性能,双精度计算的性能也有37 PFlops,在2018年6月的Top500榜单中高居第5(这期榜单中的第1、3、5名都采用V100 GPU),当年8月起开始提供云服务。

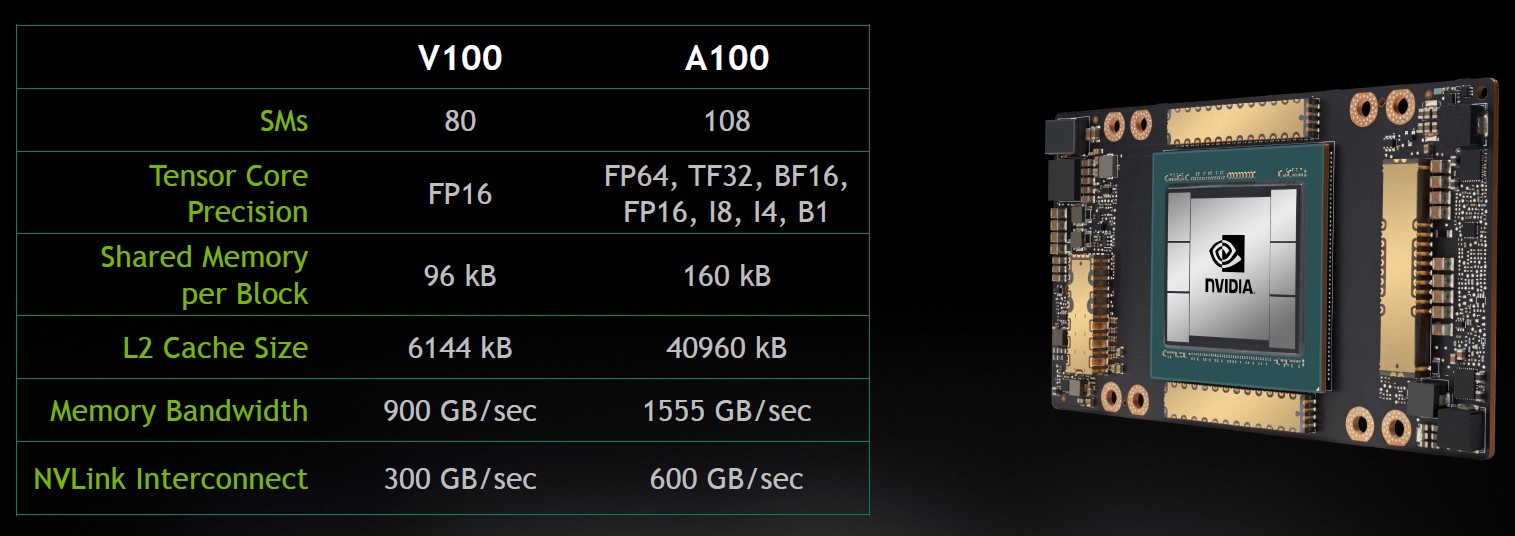

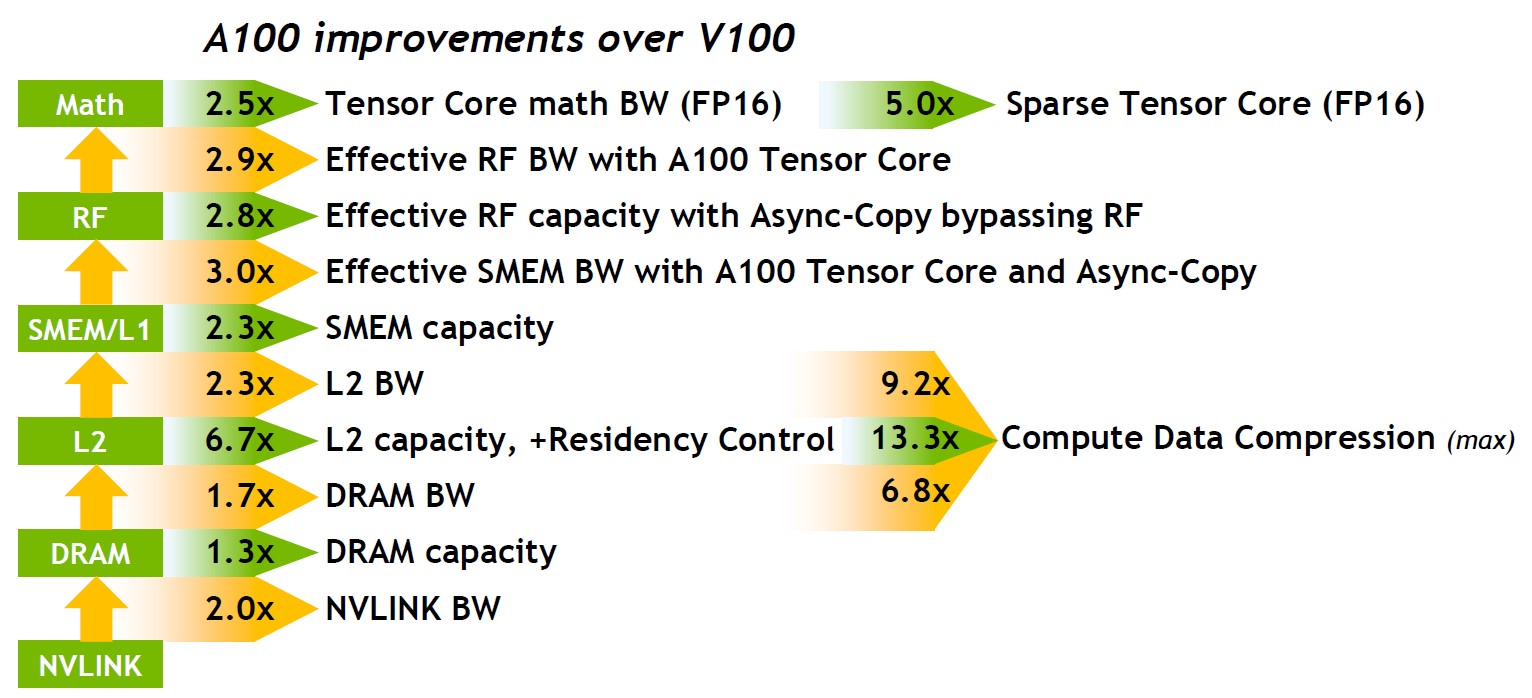

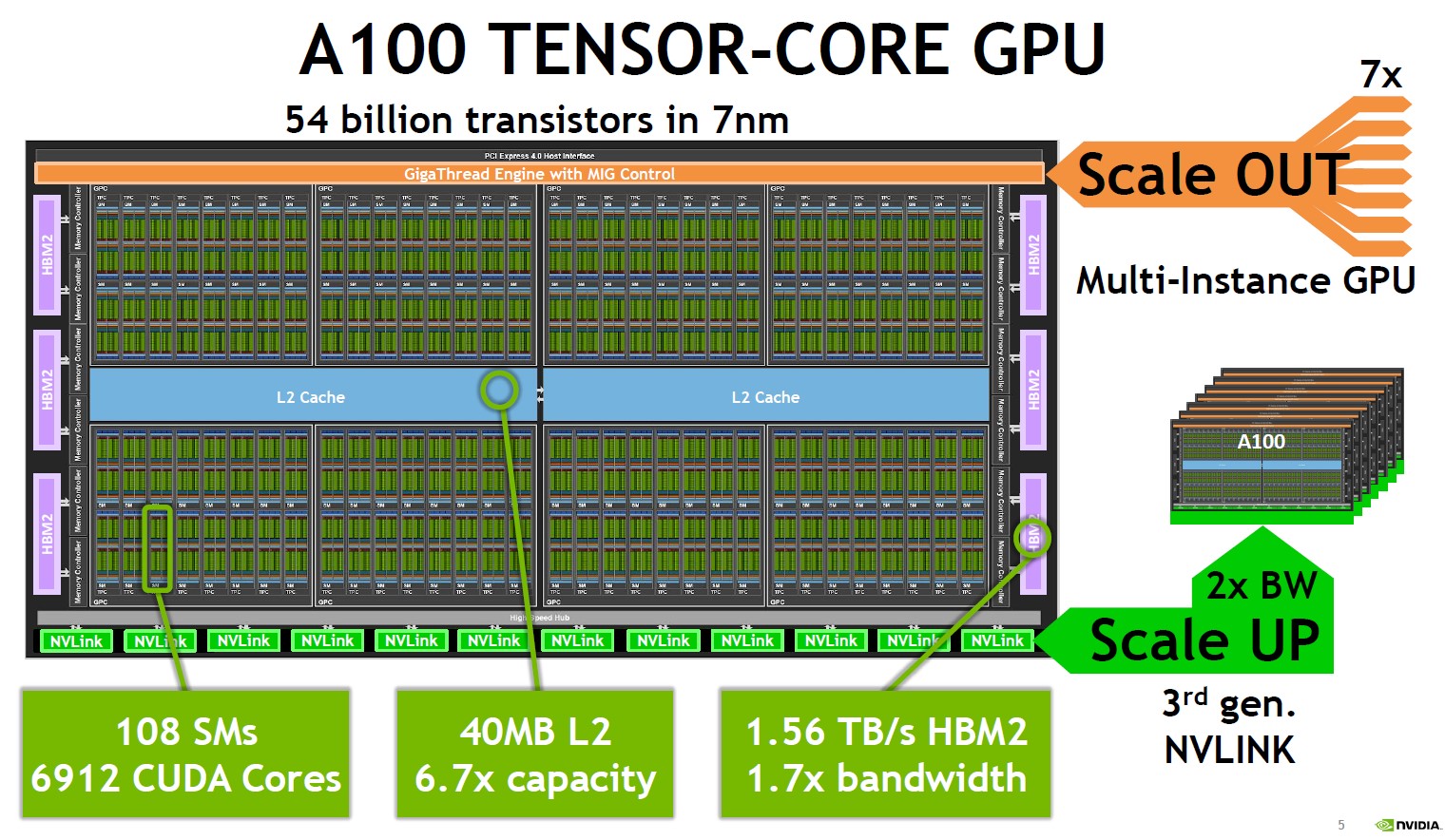

A100相对V100的全面提升

在V100的基础上,A100在对AI、云计算方面的支持又有了明显的提升,还运用了多项(大)数据方面的技术。接下来我们就结合对A100系列产品的分析,来看看安培架构是如何集ABC之大成的。

从8到1:A100的若干硬指标

A100是NVIDIA的第八代数据中心GPU,DGX/HGX A100支持8个A100 GPU;

全面转向7nm制程,MIG支持7个GPU实例;

6.7倍的L2 Cache容量;

目前的A100是完全态的5/6;

DGX A100全面支持PCIe 4.0;

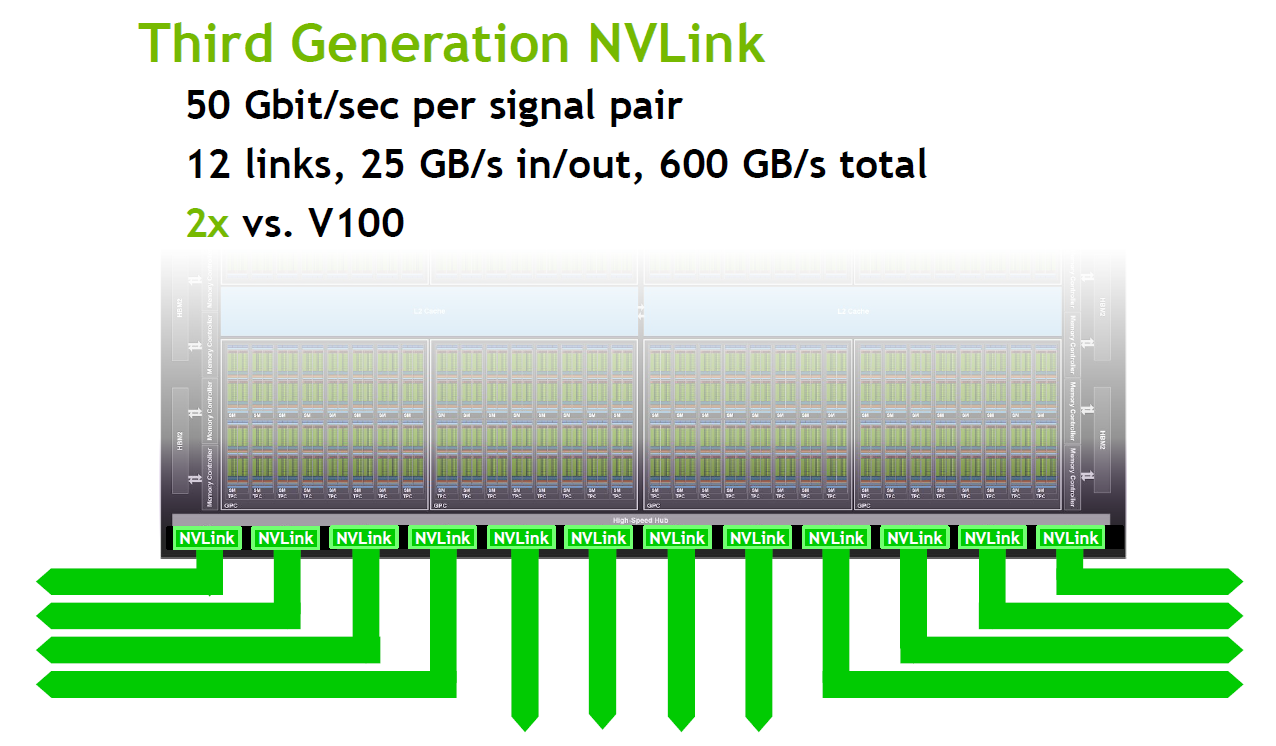

第三代Tensor Core,第三代NVLink;

第二代NVSwitch,2倍结构化稀疏性能,计算数据压缩2~4倍无损压缩,200Gb/s网卡;

1款GPU满足多种使用场景(ABC),不同使用模式(Scale-out和Scale-up)。

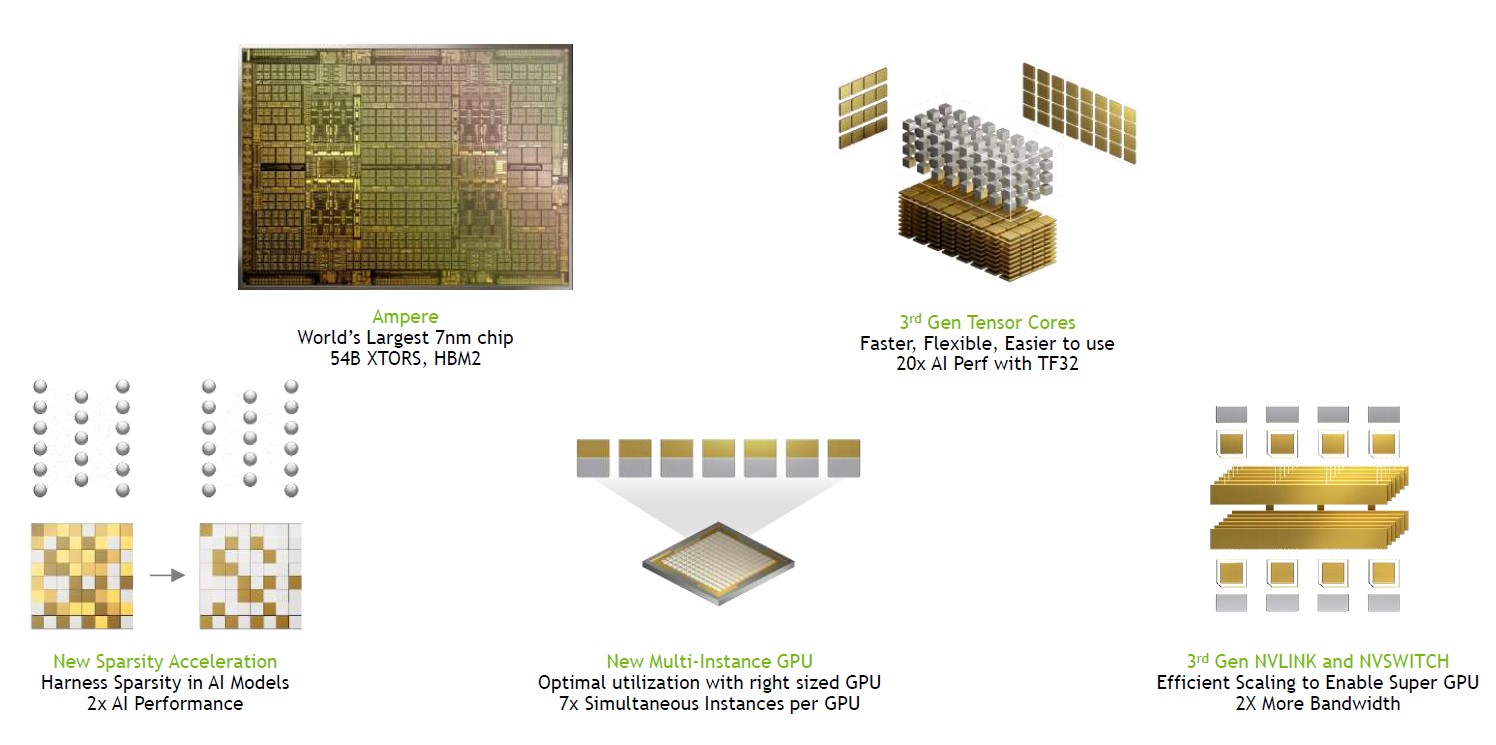

与V100相比,A100晶体管数量增加1.5倍多(542亿÷211亿=2.56),芯片面积(die size)却几乎没有变大(826mm² vs. 815mm²),体现了制程从12nm升级到7nm的威力,为各项性能的巨大提升打下了坚实的基础。

A100的5大法宝

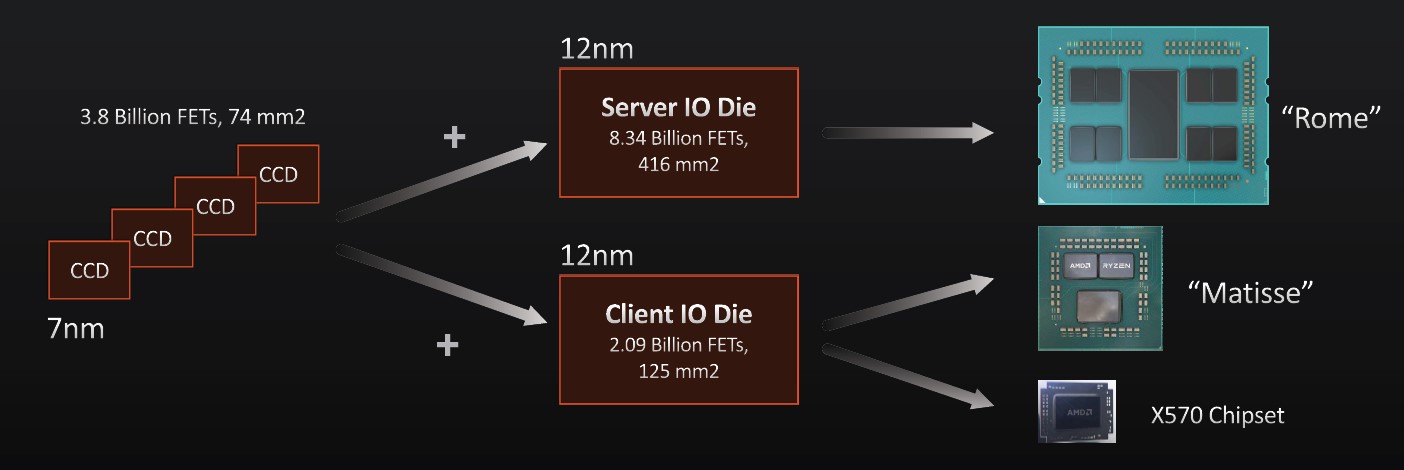

可能有人对542亿晶体管和826mm²(平方毫米)没太多概念,那就拿A100的好基友、先采用台积电7nm制程的AMD第二代EPYC(代号Rome)处理器来做个对比。第二代EPYC采用所谓的Chiplet(小芯片)技术,最多由8个38亿晶体管、74mm²的CCD和1个83.4亿晶体管、416mm²的IOD组成,简单相加起来是387.4亿晶体管和1008mm²,也就是刚过七成的晶体管数量换来了更大的(总)芯片面积。

AMD第二代EPYC处理器的芯片构成,IO Die的制程应为14nm

当然,这样比对EPYC不够公平,因为晶体管数量最多的IO Die仍采用14nm(也有说12nm,以前者为准)制程,芯片面积肯定吃亏。AMD这样做有很多理由,包括I/O器件从领先制程中获益较少,沿用成熟工艺更为划算……反过来也进一步证明,采用7nm制程的(小)芯片每个不到40亿晶体管、80多亿晶体管就要考虑7nm制程的投入产出比,看起来还是NVIDIA更为大胆。

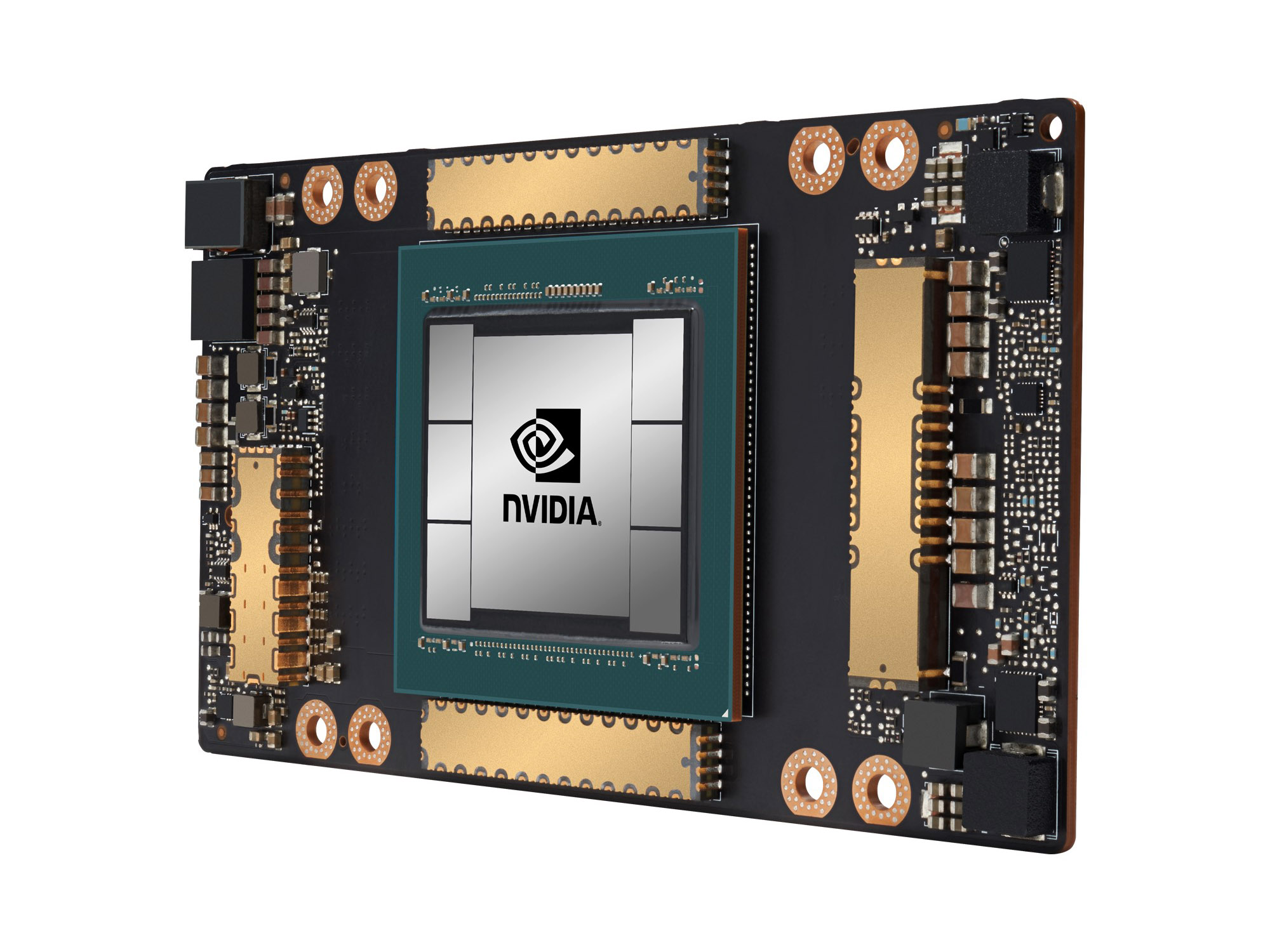

GPU芯片两边的6个HBM2芯片是A100外观上最容易与V100(4个)区分的特征之一。这两代GPU也都采用多芯片立体封装的工艺,但作为核心的GPU芯片仍是一个整体,所以制造难度越来越大

Chiplet的一大诉求就是避免制造单个巨大的芯片(Monolithic),以保证良率,而要读懂A100的核心特性,也必须了解良率带来的挑战。

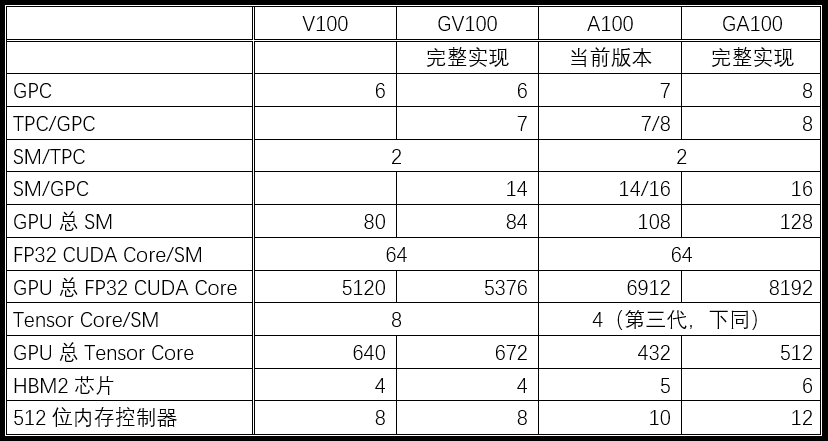

A100与V100的关键硬件参数对比

注:相对于各自的完整实现,A100的器件损失比例明显高于V100,也体现了新制程的难度

从上表中可以看到,当前版本的A100 GPU,离理想状态——也就是完整实现的GA100 GPU——还有一定的距离。判断的关键是计算单元(SM)与存储单元(HBM2芯片和内存控制器)的数量,A100与GA100在这三个参数上都是5:6的关系(而V100与GV100的SM数量之比是相当接近的20:21)。也就是说,随着制造工艺的完善,A100的性能指标还有接近五分之一的提升空间。

个人认为,这个看似不算很大的提升空间对于云计算服务提供商颇有价值,因为它关系到A100的一个重要特性——MIG。

AI:少即是多 | 第三代Tensor Core

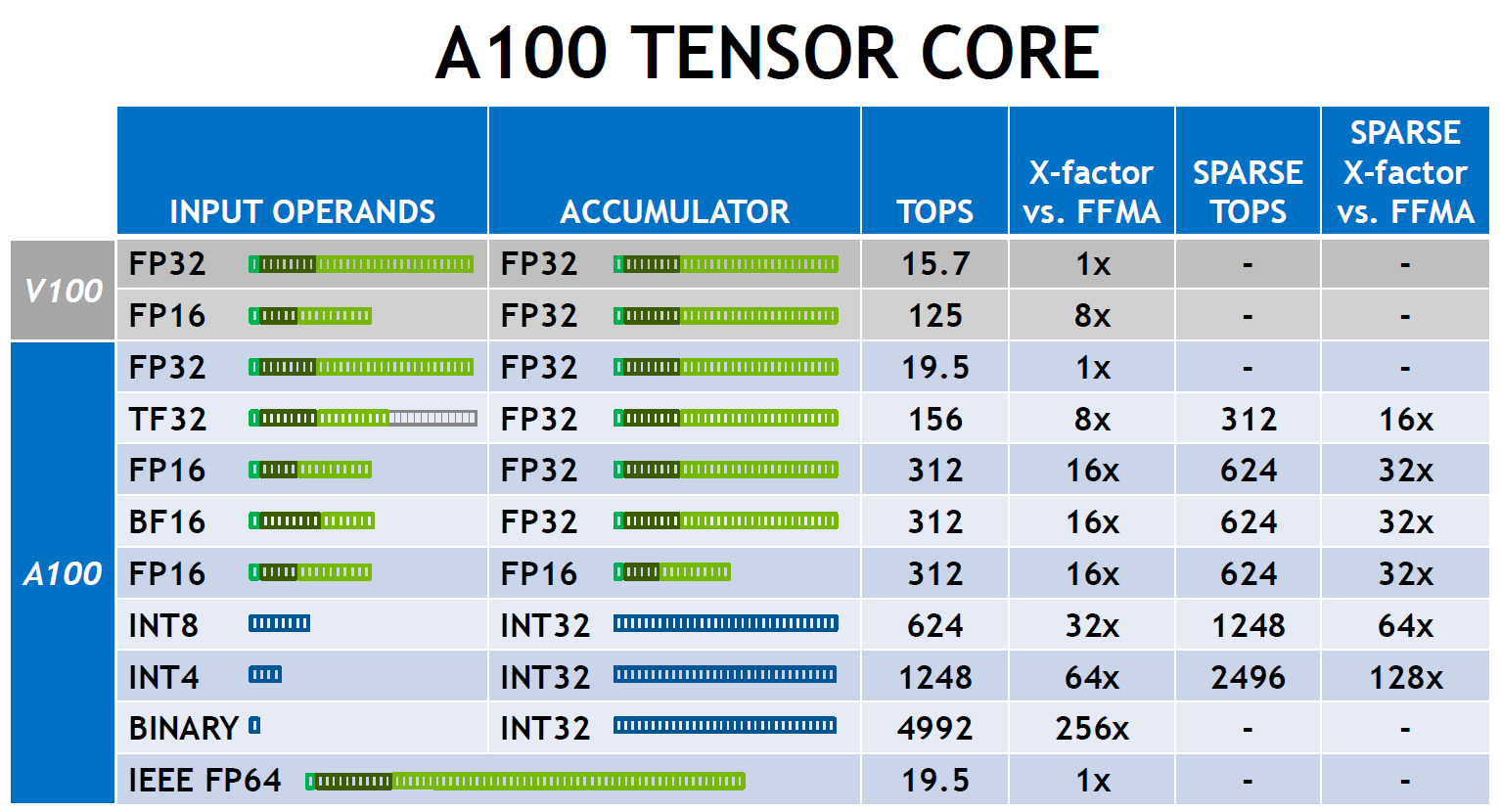

单从计算和存储单元的的数量来看,A100相对V100的优势,似乎还赶不上晶体管数量的增加;Tensor Core的数量甚至有明显下降,但这已经是第三代Tensor Core,单体战斗力不可同日而语,总体输出反而全方位提升。

根据NVIDIA公布的数据,FP16/FP32混合精度下,V100每个SM的TOPS是A100的两倍,结合SM数量的增长,总TOPS达到2.5倍,看起来与晶体管数量的增加相匹配。

A100支持bfloat16和TensorFloat-32两种新的数据类型

然而“硬”指标只是一方面,A100的Tensor Core在数据预处理上下了更大的功夫,通过减少实际参与运算的数据量来强化中低精度的性能。这主要体现在两方面:

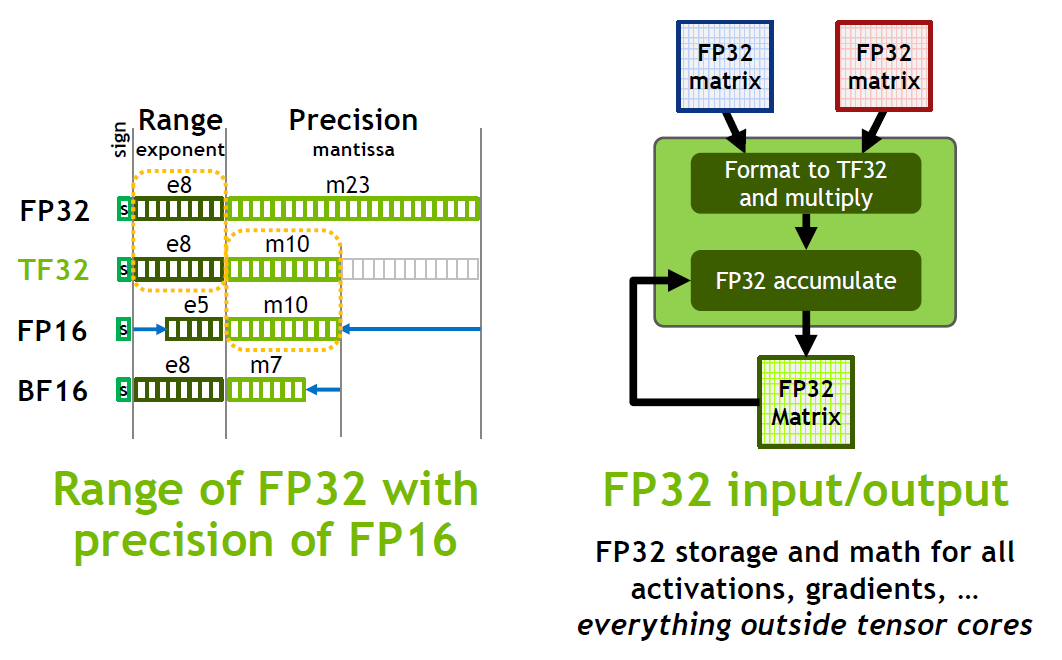

首先是支持更多的数据类型。A100的Tensor Core支持Google在TensorFlow中引入的bfloat16(BF16)数据类型,它相当于直接截取了FP32的前16位,所以在存储和运算开销与FP16相当的情况下,具有更大的动态范围,代价是牺牲了精度。A100 Tensor Core的创新之处是引入了TensorFloat-32(TF32)来加速FP32运算,TF32结合了FP32(等同BF16)的动态范围和FP16的精度(高于BF16),数据位宽仅略大于FP16,FP32矩阵相乘之前先转换为TF32格式以加快处理速度,据称在HPC的线性动力学场景中可以获得4倍的性能提升,并在单精度训练中达到5倍的性能。

进入Tensor Core的FP32数据被转换为TF32以加速运算,外部的存储和运算仍保持FP32格式

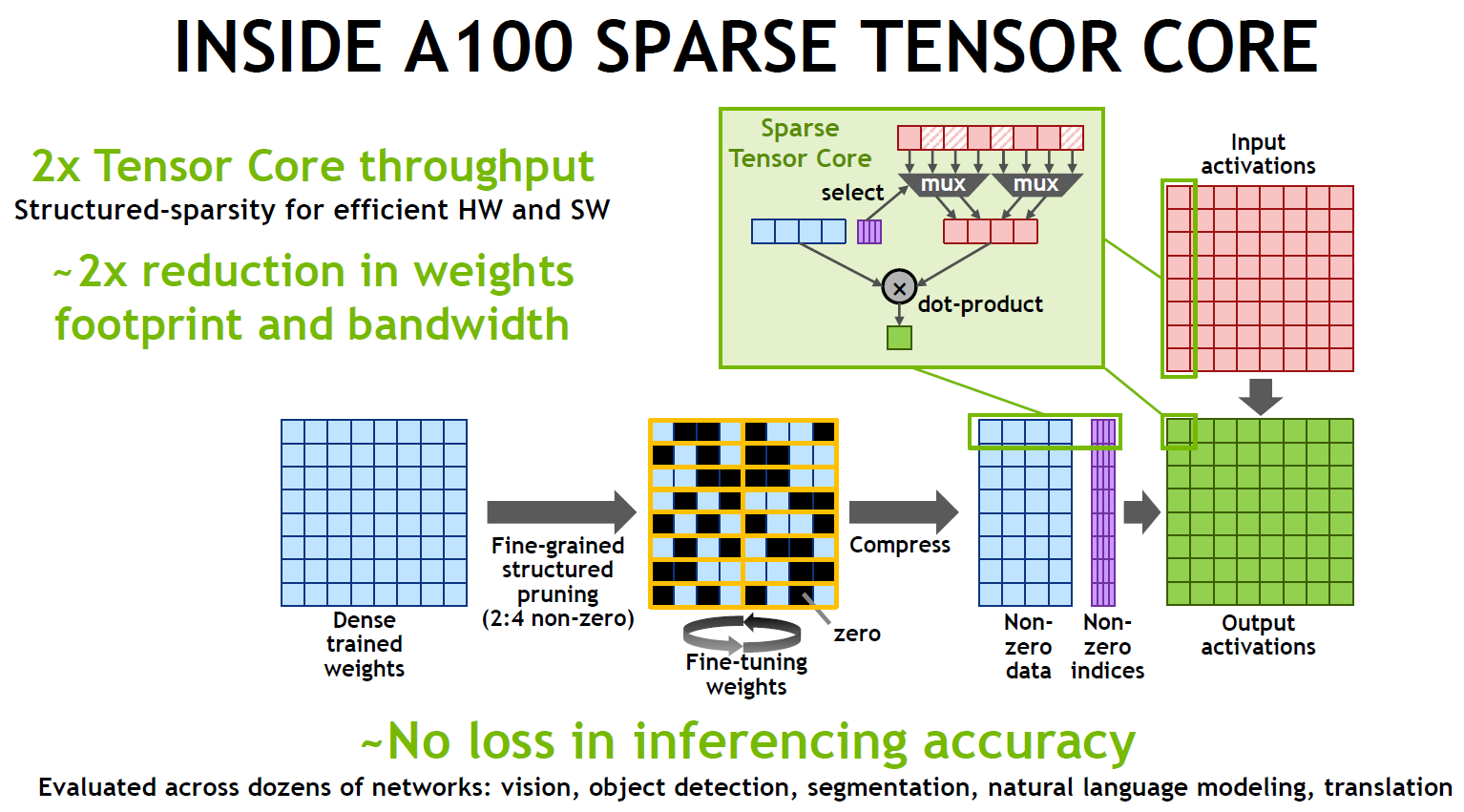

再往上到了数据结构层面,即支持(细粒度)结构化稀疏,适用于加速卷积和矩阵乘操作,优化推理性能。对细粒度权重稀疏的研究由来已久,NVIDIA表示A100是第一次将这方面的研究成果转化为生产。这个细粒度的结构化稀疏比较规整,稀疏度是50%、在连续4个数据元素中按规则选取2个值置0而不存储,相当于把矩阵的数据量压缩一半,不过元数据索引还有一定比例的开销。安培架构Tensor Core通过把稀疏计算转变为稠密计算,理论上能够将TOPS再提高一倍,NVIDIA出示的数据表明:矩阵乘和卷积性能提升大约为1.5~1.85倍,端到端推理可以获得30~50%的加速。

推理性能从结构化稀疏中获益颇多,而精度基本没有损失

追求AI性能的同时,A100 Tensor Core也没有忽略HPC需要的高精度运算,支持IEEE FP64双精度加速。新的双精度矩阵乘加指令替代了V100的8条DFMA指令,降低了指令预取、调度开销、寄存器读、数据路径功耗和共享内存读带宽。使用Tensor Core,A100的每个SM每个时钟周期可以完成64个FP64 FMA(Fused Multiply-Add,融合乘加)操作或128个FP64操作,是Tesla V100的两倍。结合SM数量的增长,A100的峰值FP64性能达到V100的2.5倍(19.5 TFLOPS vs. 7.8 TFLOPS)。

Big Data:大效之道 | 存储和传输

硬件升级提供更强的能力,软件算法和数据结构改进提供更高的效率,可谓基础设施换代的左右手,不可偏废。不仅第三代Tensor Core代表计算单元(SM)起到很好的示范作用,A100的存储和传输单元也不遑多让,在容量全面扩充的同时,增加了大量新特性——简单的说,就是不仅更大、更快,还更聪明。

让我们从A100的SM开始,一层层向外延展讨论。

首先,每个SM的L1数据(L1D)Cache和共享内存(L1/SMEM)容量,A100比V100增长了50%,来到192KB;结合SM数量的增加,整个GPU的L1/SMEM容量增长近一倍,约为20MB——个人认为,这点很重要,马上会用到。

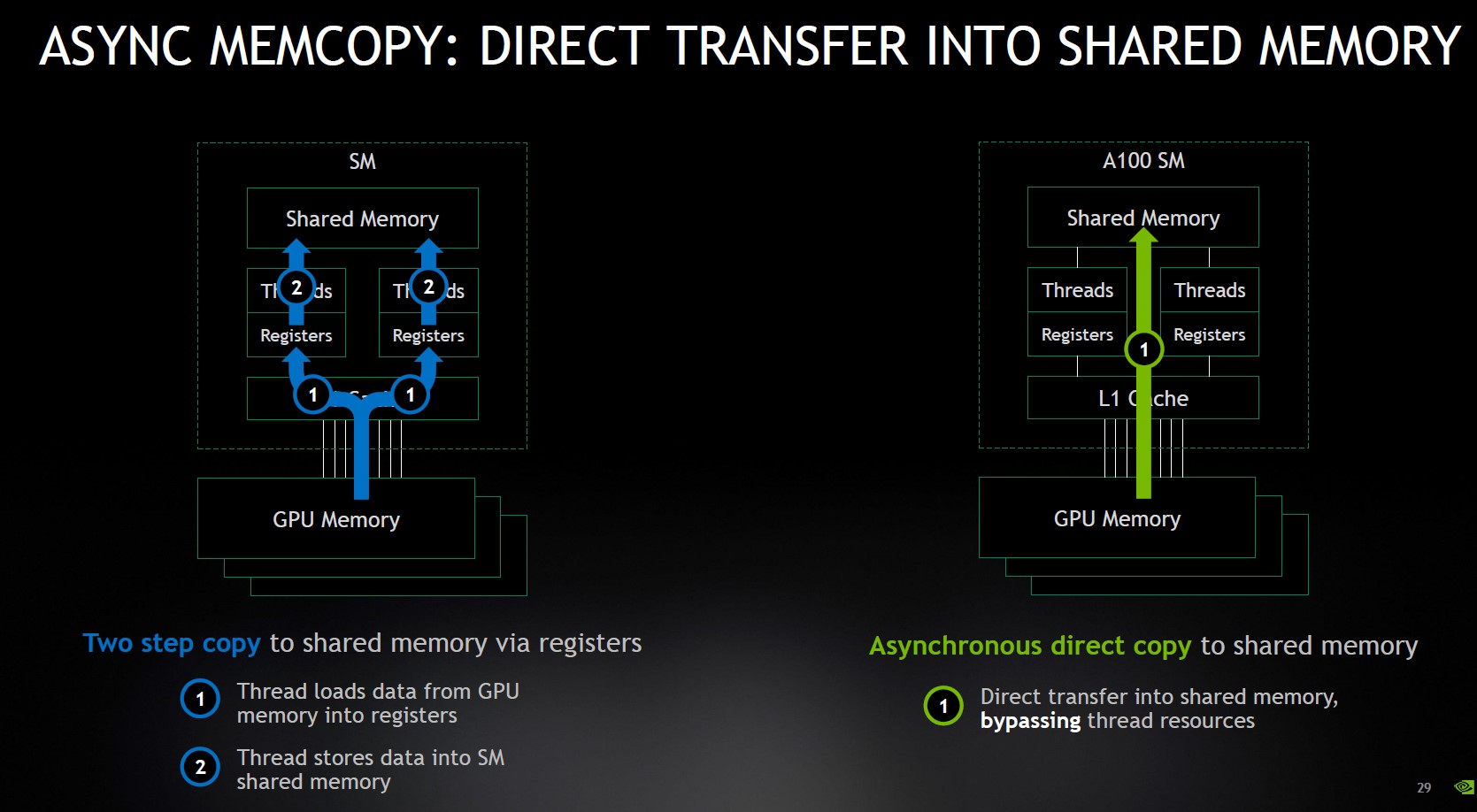

同时,增加了异步复制(Async-Copy)指令,即从全局内存(GMEM)向共享内存的数据拷贝不经过计算单元的寄存器,直接进入L1或SMEM。不仅缩短了传输路径,有助于隐藏延迟;还可以充分利用L1/SMEM的带宽,减少对寄存器的浪费。

异步复制:步骤精简,路径直接

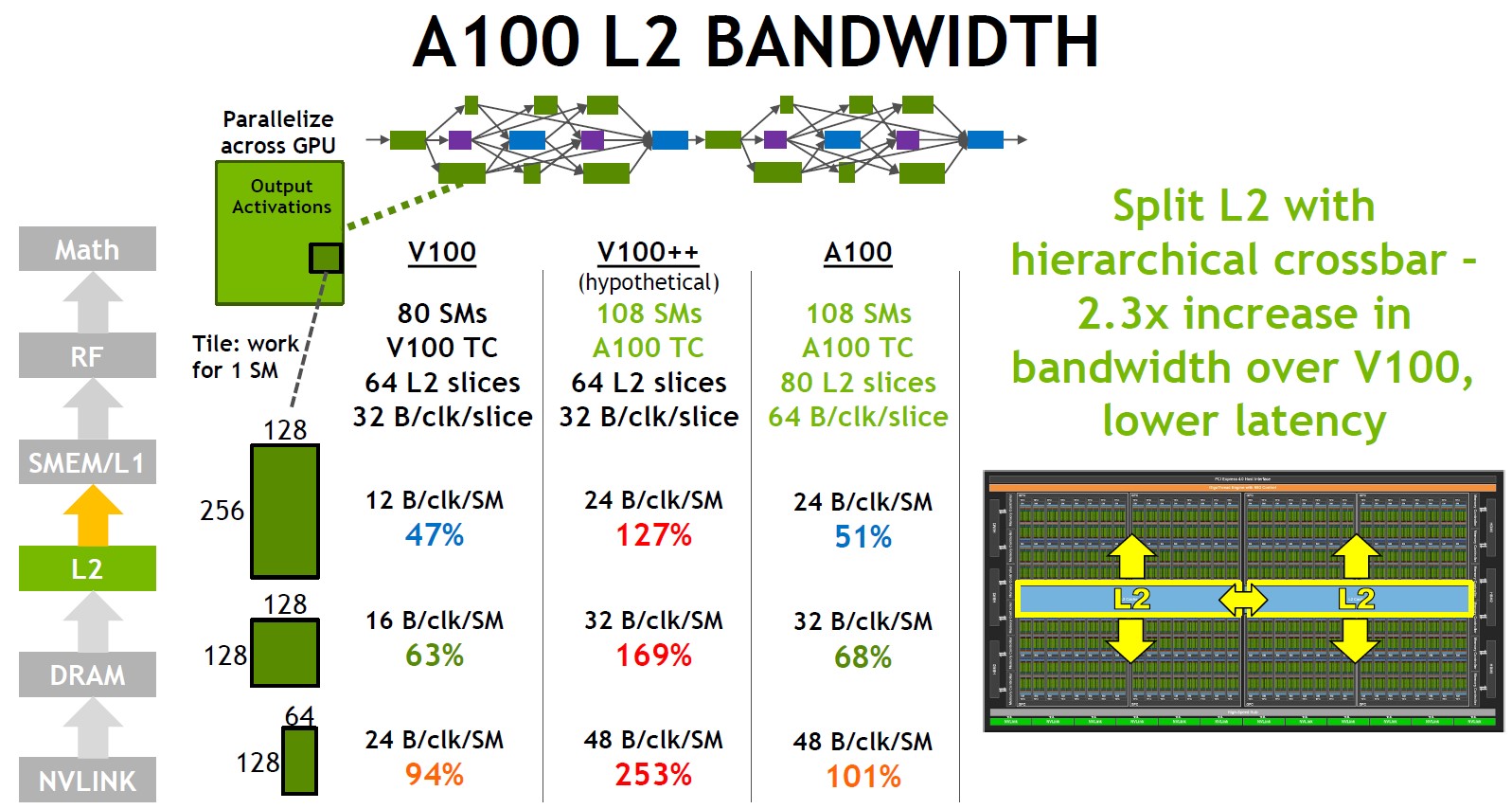

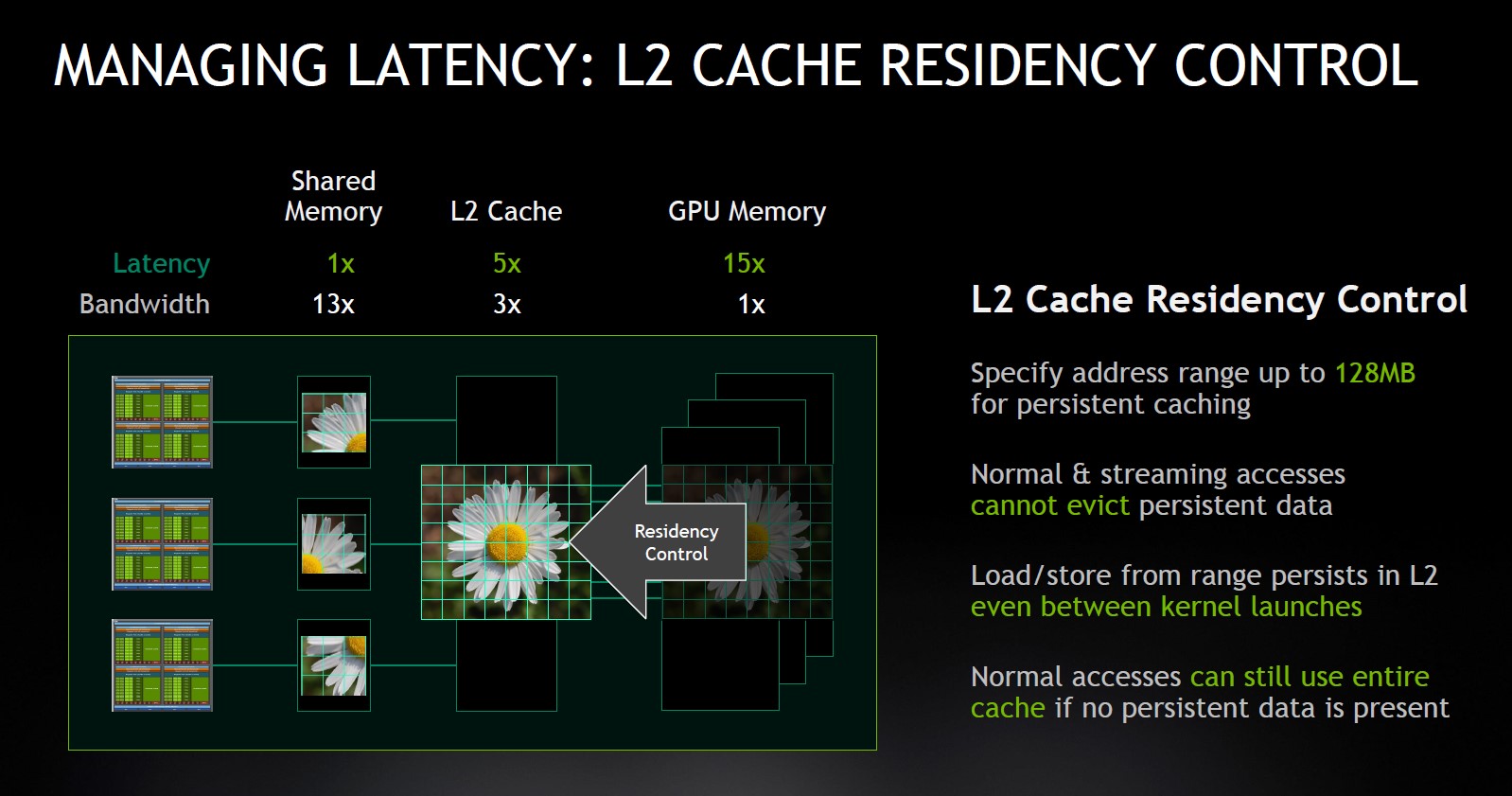

其次,A100的L2 Cache容量达到40MB,是V100的6.7倍,带宽也有2.3倍。存储性能的提升通常比容量更难,A100的做法是通过分层的Crossbar(XBAR)将L2 Cache分成两个分区,就近的SM们可以直接访问,所以延迟也得以降低。

假设V100的SM数量增加到A100的水平……

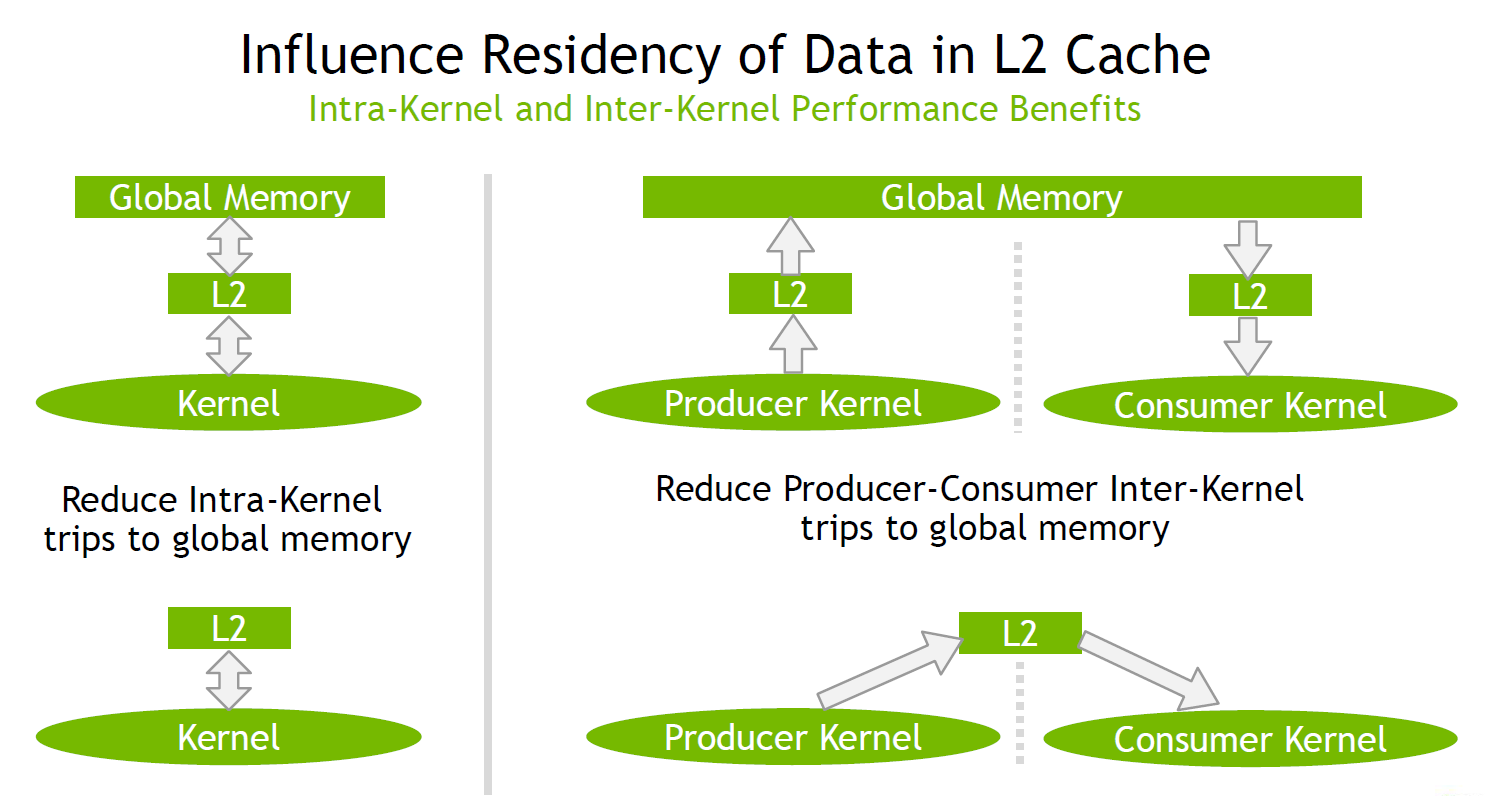

当然,容量增加本身就有助于性能提升。经过这番暴涨,A100的L2 Cache容量不仅超过了L1/SMEM,甚至达到了两倍的水平(40MB vs. 约20MB),这就激发了另一个新功能——L2驻留控制(Residency Control)。

如果说前面的L2 Cache分区访问是物理分区,那么L2驻留控制可以算一种逻辑分区:拿出一部分容量——譬如一半(20MB)——留给持久性数据访问,持久访问在L2缓存中比其他数据访问具有更高的驻留优先级;另外的区域留给正常访问。

数据驻留L2 Cache的好处是内核内部和内核之间的数据访问不用再绕经全局内存,通过L2 Cache便可完成,避免非必要的传输,既可以缩短访问延迟,减小对内存带宽的需求;也有显著的节能效果,因为访问外部存储器所消耗的能量通常会增加一个数量级。

随着内存/Cache层级的增加,访问数据的带宽明显降低,延迟和功耗成倍提高

说到外部存储器,A100的HBM2容量也扩充至40GB,HBM2堆栈和内存控制器的数量相对V100的增长幅度同为25%,所以性能增长主要来自单组HBM2堆栈与内存控制器的能力提升。凭借更高的运行频率,A100的内存带宽达到1555GB/s,比V100高出73%,如果后期A100的良率改善到可以完整的提供12个512位内存控制器和6个HBM2堆栈,理论上其内存带宽就可以达到V100的2倍以上,而不仅仅是HBM2内存容量增长到48GB。

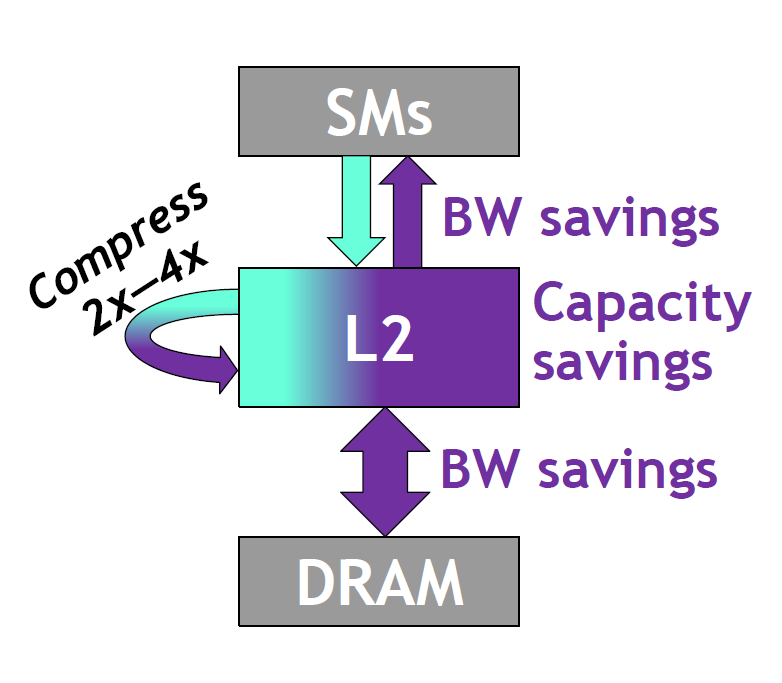

A100还通过引入计算数据压缩的功能,进一步提高有效带宽和容量。当数据中有足够多的0或相似字节,2个连续的缓存行(8个扇区)可以被压缩2倍(4个扇区)或4倍(2个扇区),在处理细粒度的非结构化稀疏数据时,可以获得最高4倍的内存和L2带宽节省,L2容量也有2倍的节省。计算数据压缩功能是无损压缩,适用的数据类型也没有结构化稀疏那么严格,可以在更大范围内发挥作用。

Cloud:生而为云,做七望八 | MIG

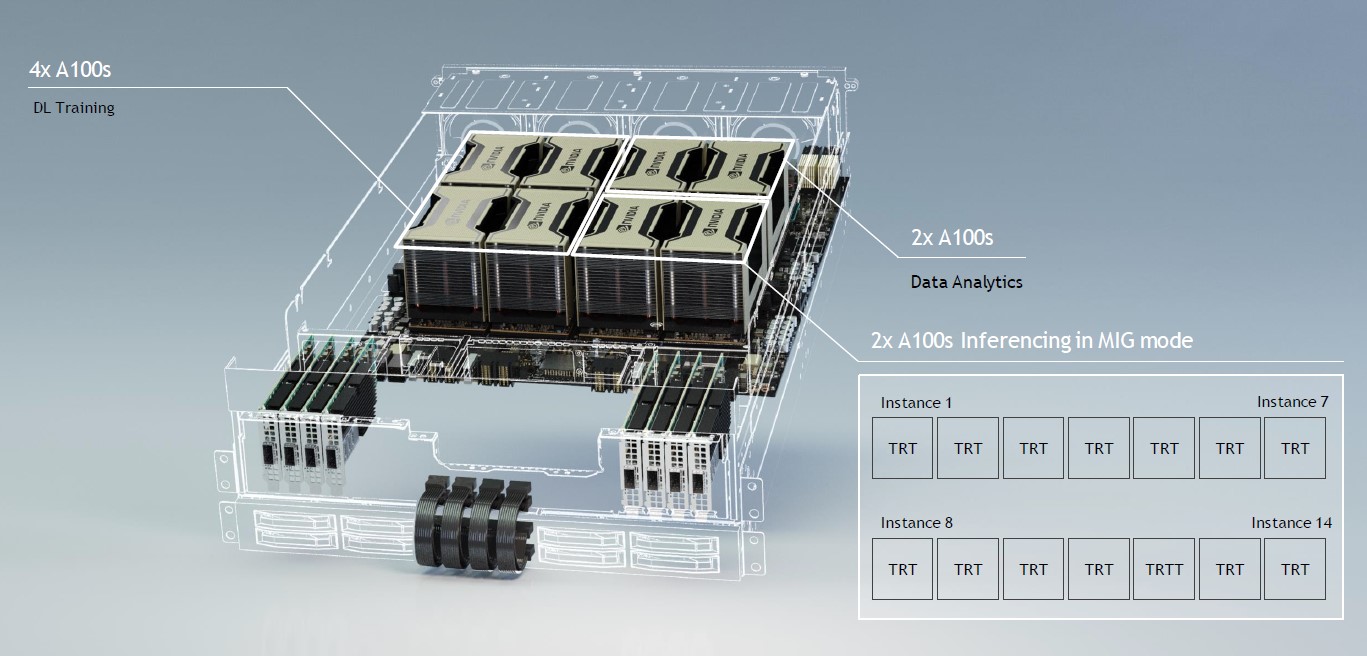

经过硬件升级和软件优化的双管齐下,A100的性能比V100有了成倍的提升:AI训练达到3倍(FP16)乃至6倍(FP32),推理更高达7倍——以此为参照,HPC场景1.5~2.1倍的性能简直可以说是“平平无奇”了。

不过,这也带来了一个现实的问题。不像HPC,AI的场景与云的模式更为契合,因为有些计算任务(特别是推理)并不需要超强的处理能力,用不到一个GPU的全部资源,能够将一个GPU上的资源分配给多个用户或应用更为重要。随着A100的性能达到一个新的水平,这种“一分为多”的需求也就愈发迫切起来。

V100通过引入硬件加速的MPS(Multi Process Service,多进程服务)将一个GPU分配给多个进程,但是在内存系统资源的隔离上不够彻底,对DRAM带宽或L2 Cache需求过高的应用(即虚拟化领域常说的“吵闹的邻居”)会干扰到其他应用,也就是QoS(Quality of Service,服务质量)无法保证。由于没有提供足够的硬件资源隔离,云服务提供商不能通过MPS把GPU分享给多个用户使用。

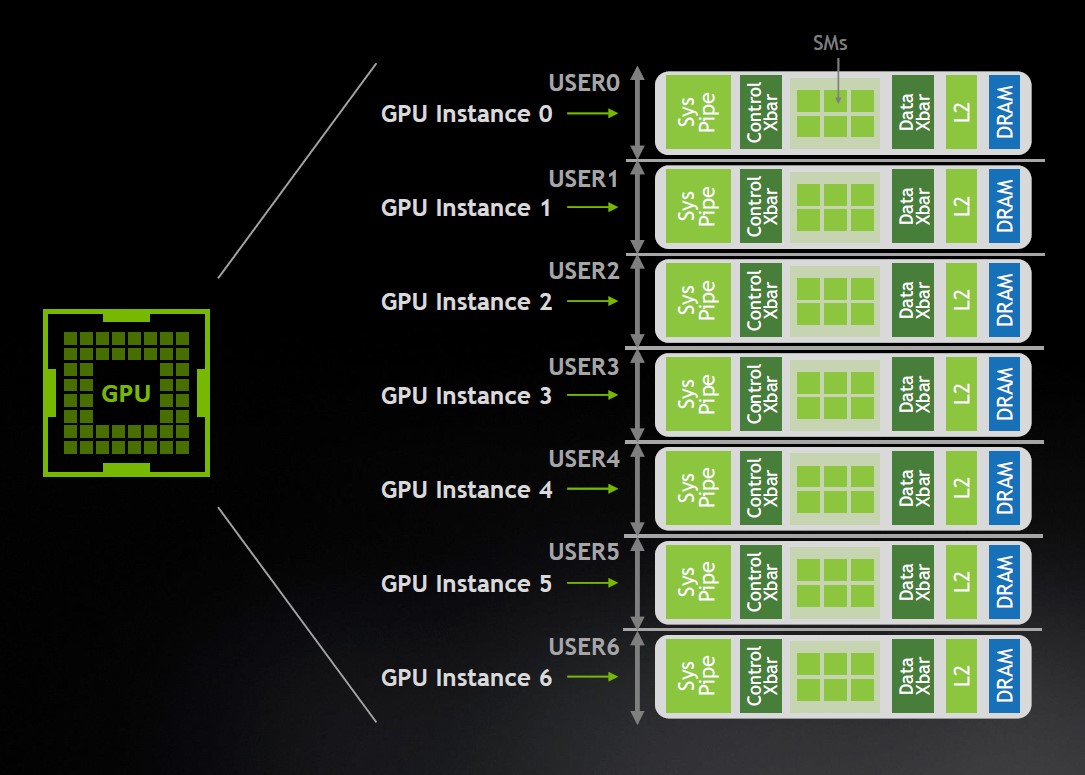

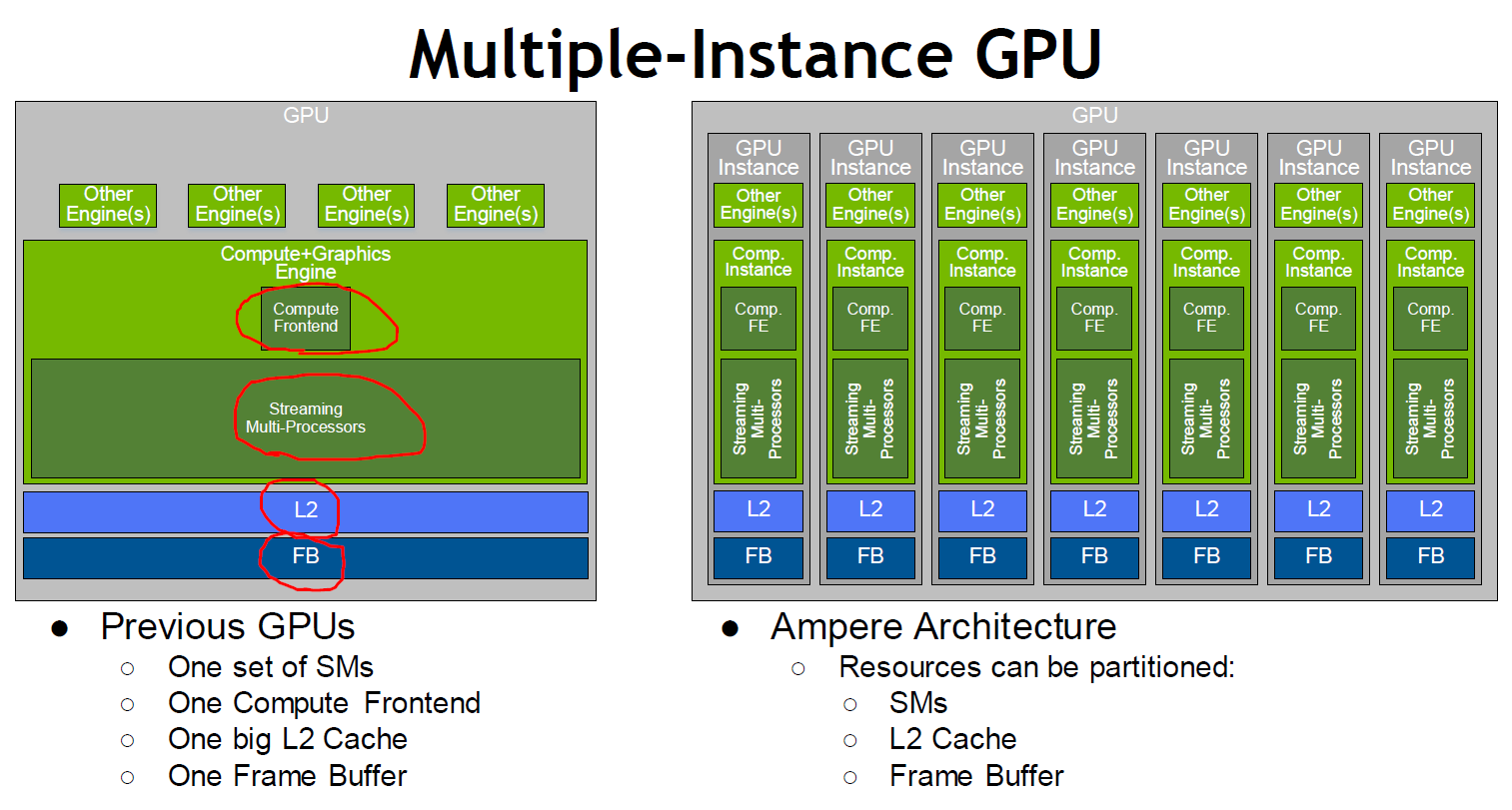

又一个逻辑分区对物理分区

前面提到的MIG(Multi-Instance GPU,多实例GPU)是A100针对MPS的不足而引入的新功能,一个A100最多可以被切分为7个GPU实例,每个都有自己的计算单元(SM)和存储单元(L2 Cache、DRAM和带宽)以保证硬件QoS和隔离,从而能分配给多个用户或租户使用。

SM已经按照GPC分区了,所以L2 Cache加入“物理分区”功能就很重要

全部的MIG实例能够以可预测的吞吐量和延迟并行运行,从这个角度来看,可以把MIG实例当成独立的GPU单元,不同数量(如1/2/4个,上面MPS对比图右侧)的MIG实例可以灵活组合起来,分配给不同的用户和应用,也就是NVIDIA所宣称的Scale-out(横向扩展)——不过,如果站在(A100)GPU的角度,用相对小众的Scale-in来称呼似乎更为严谨一些。

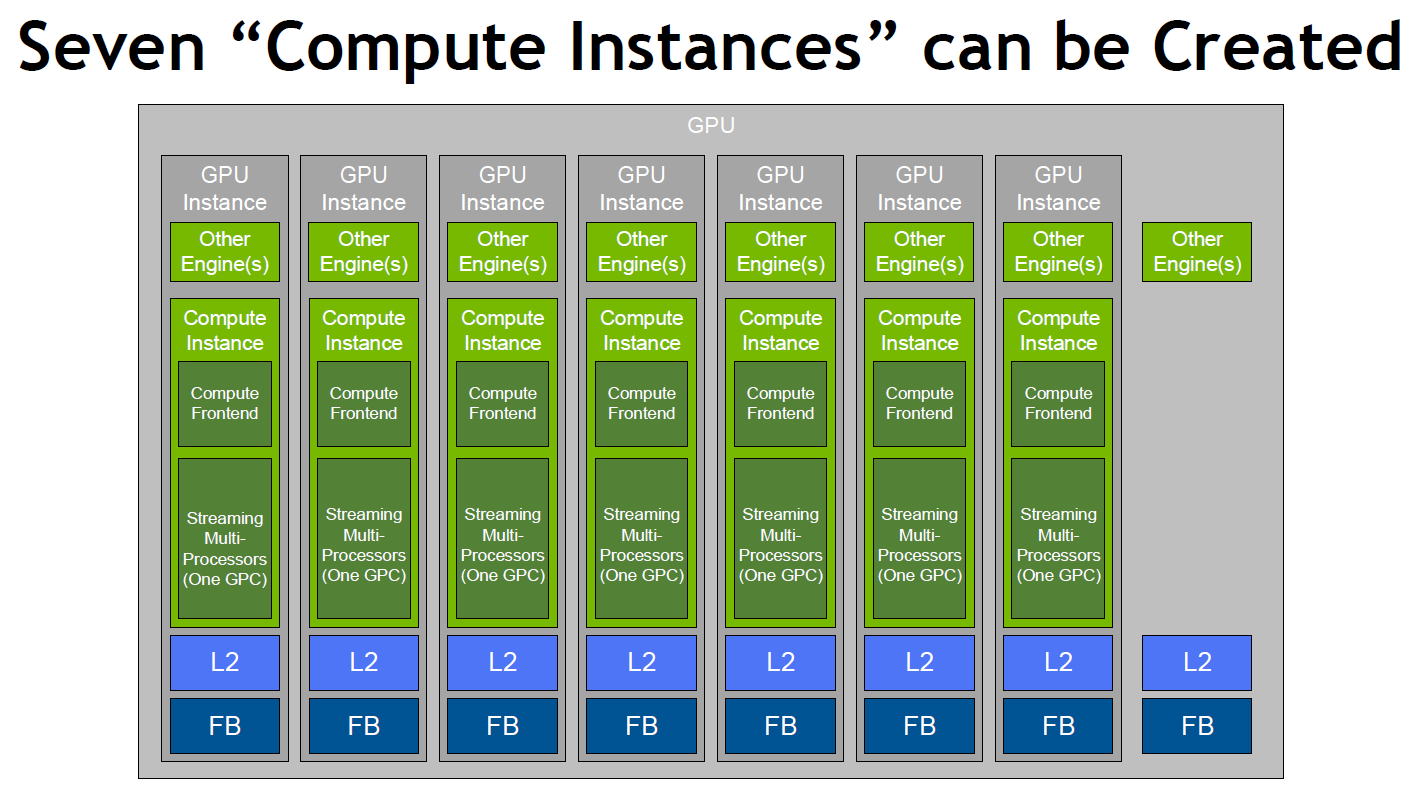

至于MIG功能为什么可以将A100切分为7份,当然不是因为其(推理)性能7倍于V100,每一份都可以当V100用。

虚位以待第8个GPC

MIG的切分是以GPC为单位的,依次划拨相应的存储资源,所以它充分考虑到A100的现状,只要求每个GPC有7个TPC、14个SM,而当前A100的所拥有的GPC也是7个,可以切分出来的GPU实例自然是7个。考虑到有些GPC能达到8个TPC、16个SM的“完全态”,在某些关于MIG的示意图里,我们可以看到有少数多出来的硬件资源,不在7个GPU实例之内。

个人认为,A100对MIG的支持有望达到8个,因为现在的7个MIG,涉及到的计算资源是7个GPC、49个TPC、98个SM,而随着制造工艺的完善,未来A100 GPU要实现8个GPC和112个SM的“近完全态”,并非没有可能。

DGX & HGX:化繁为简,更小更强

如果说,在把GPU做“小”,或曰Scale-out的方向上,MIG是一项创新;那么,在把GPU做“大”,或曰Scale-up的方向上,A100也把传统曲目唱出了新意思。

可大可小,Scale-up与Scale-out通吃,训练、推理、数据分析都能干的单一平台

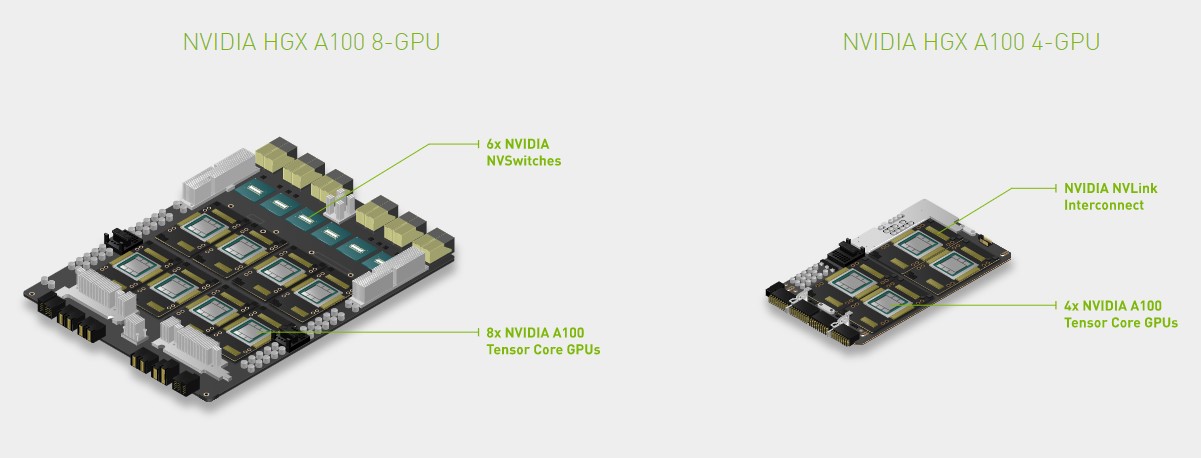

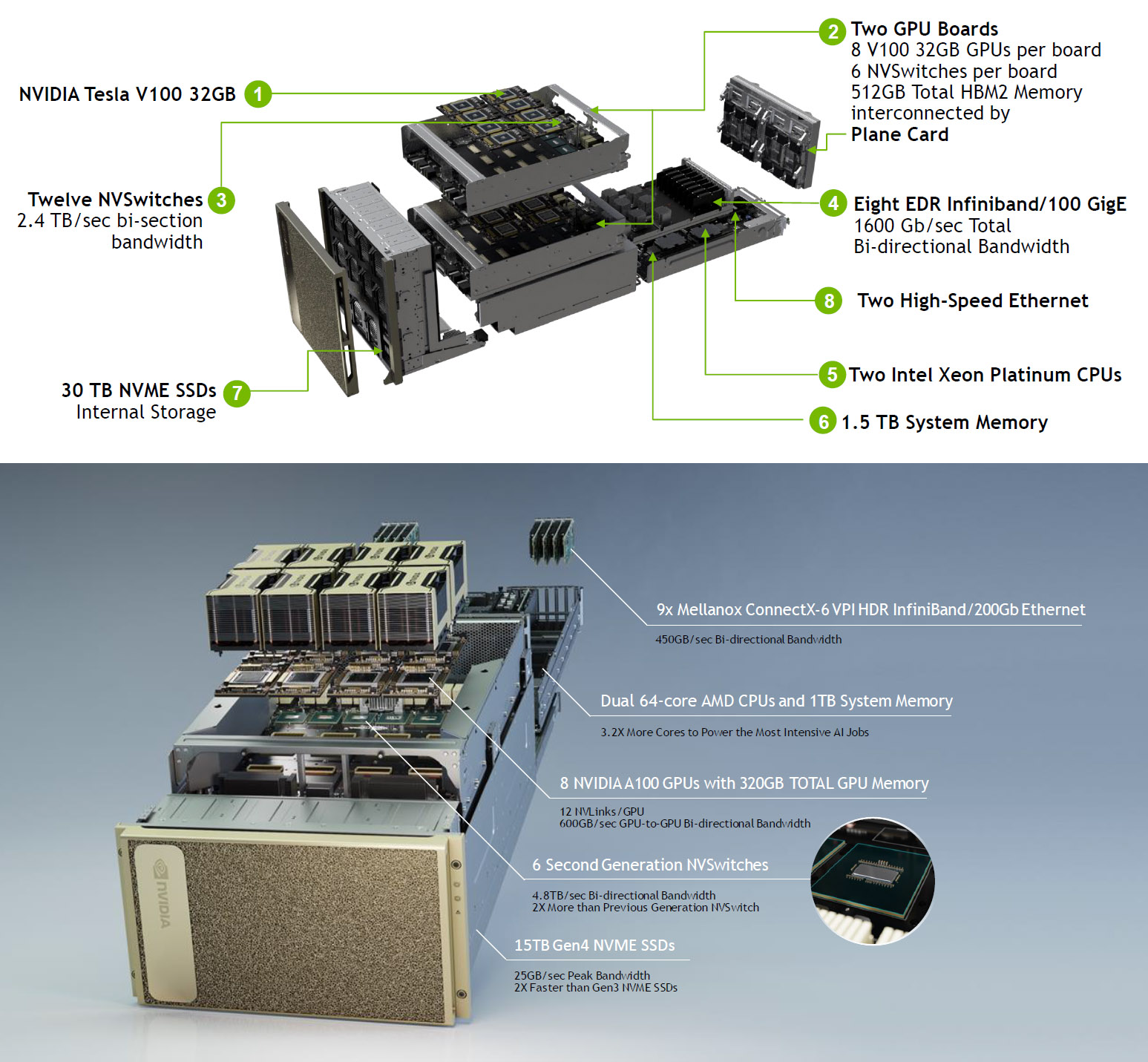

从衡量系统规模的几个重要参数上,与前一代基于Tesla V100的DGX-2相比,DGX A100的GPU数量从16个打对折到8个,GPU总内存容量从512GB下降至320GB,系统内存容量从1.5TB下降至1TB。总之,看起来Scale非但没有up,反而down了?

Up还是down,性能说了算。从NVIDIA公布的性能指标来看,DGX-2是2 PFLOPS,DGX A100是5 PFLOPS AI,可以认为是2.5倍;从NVIDIA公布的测试数据来看,拉出来做对比的是8个V100的DGX-1@FP32,在训练场景下DGX A100@TF32可以获得6倍的性能。

构成DGX A100核心的三大类芯片都采用7nm制程,A100 GPU和CPU——AMD第二代EPYC处理器——前面都说过了,现在要说的是新一代NVSwitch,同样基于台积电7nm制程,具有多达60亿晶体管。NVSwitch是以I/O为主的芯片,与第二代EPYC的IOD更具可比性,晶体管数量也相差不是太多,再一次体现了NVIDIA全面切换到7nm制程的“激进”态度。

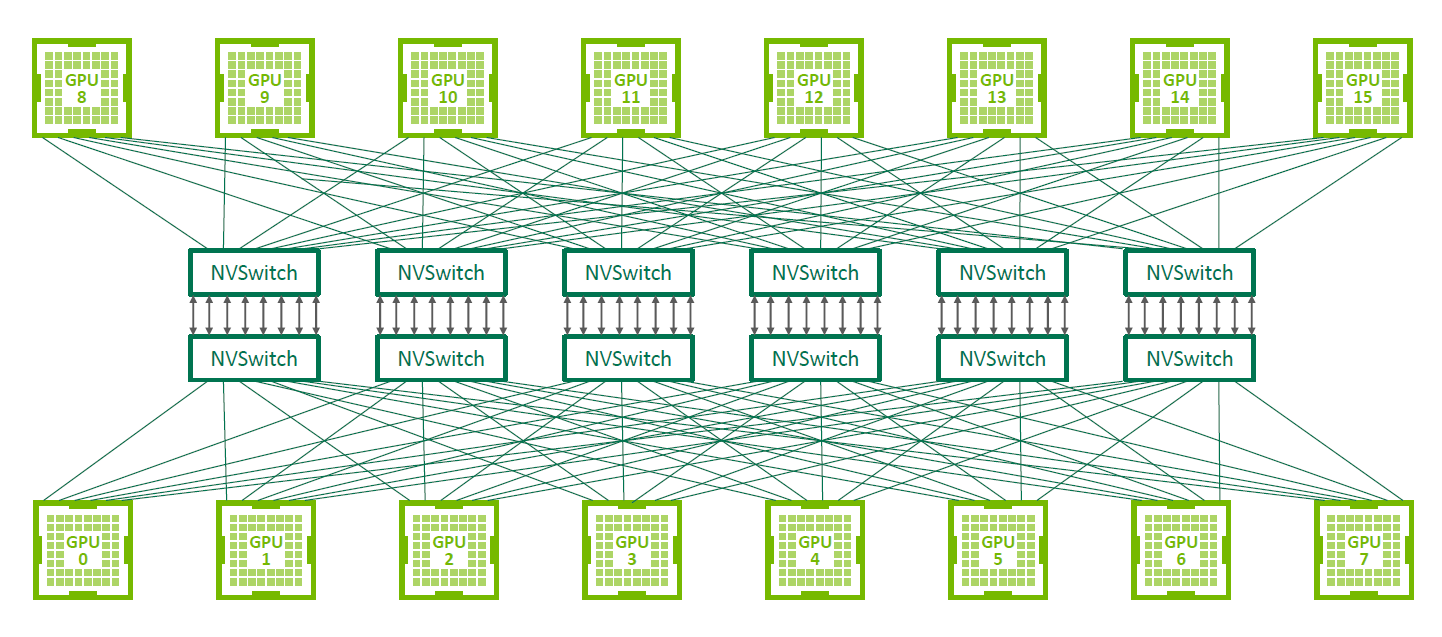

DGX-2开始将NVSwitch用于GPU的互连,初代NVSwitch有18个NVLink端口,V100上有6个NVLink,形成了6个NVSwitch把8个GPU连在一起的架构。NVSwitch上多出的NVLink可以用于彼此间的互连,DGX-2一共用了12个NVSwitch芯片,将16个V100 GPU连为一体。

部分得益于7nm制程,新一代NVSwitch的NVLink端口数量达到36个,A100 GPU也有12个第三代NVLink,总带宽600GB/s,DGX A100核心器件的这三项指标均为DGX-2的两倍。不过,DGX A100和(采用NVSwitch的)HGX A100并没有借机扩大GPU的互连规模,反而退回到DGX-1的8个,致力于保证GPU之间的互连带宽。

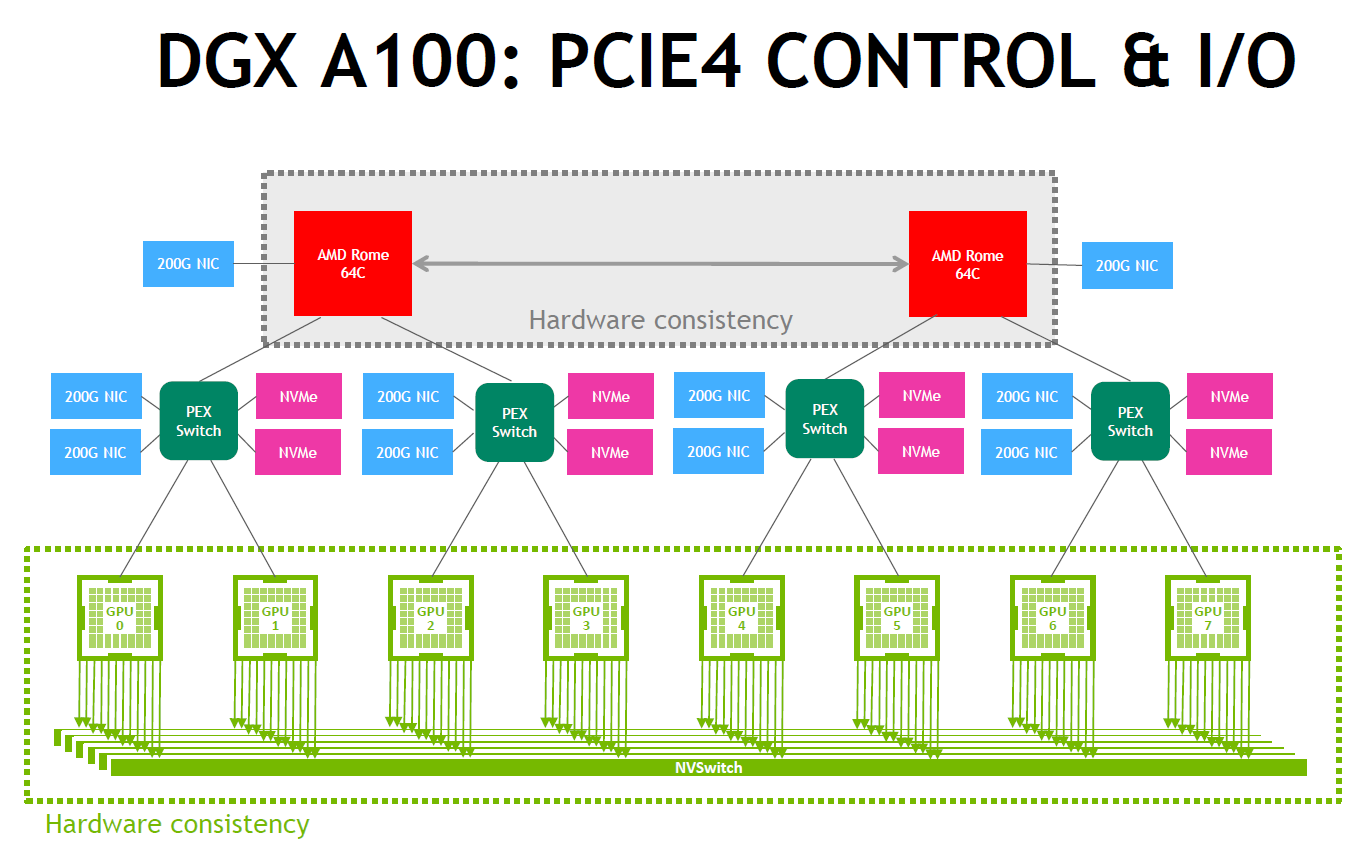

GPU的出口带宽增长了,对CPU及外部I/O的要求也随之提高。DGX-2配备双路24核处理器,DGX A100则升级为双路64核处理器,CPU核芯数量达到两倍以上,内存容量的减少可能与GPU数量的减半有关。第二代EPYC处理器的另一个杀手锏是支持PCIe 4.0,带宽两倍于PCIe 3.0,对存储和网络等I/O设备意义重大。

众所周知,NVIDIA已经完成了对Mellanox的收购。DGX A100配置了9个Mellanox ConnectX-6 200Gb/s网卡,这是什么概念呢?如果仍然使用PCIe 3.0,那么200Gb/s网卡就需要2个x16插槽支持才能充分发挥作用,而PCIe 4.0就只需要一个x16插槽, 保证系统的复杂度不会增加。

Mellanox ConnectX-6 200Gb/s InfiniBand/以太网卡:PCIe 3.0版本(上)需要占用2个x16插槽,以获得足够的带宽支持;而PCIe 4.0版本(下)因为单个插槽的带宽倍增,所以只需要占用1个……复杂与简洁一望便知

系统配备的固态盘(SSD)同样支持PCIe 4.0,虽然容量也减半,至少存储性能可以保持。

由于系统中占比很大的核心组件如GPU、NVSwitch、GPU基板的数量都减少了一半,DGX A100的整体复杂性大为下降,高度也只有6U,介于DGX-1(3U)和DGX-2(10U)之间。对于数据中心而言,更重要的是系统的供电需求,从DGX-2的10kW(千瓦),下降到6.5kW——仍高于DGX-1的3.5kW,已经大幅降低了对机柜供电能力的要求,国内的很多数据中心不需要过多的调整即可满足。

与GPU直接相关的组件数量都只有DGX-2(上)的一半,所以DGX A100(下)的构成可以从偏正面的角度来呈现

尽管采用7nm制程,奈何A100 GPU的晶体管数量增长更为迅猛,TDP已经来到400W(瓦),比Tesla V100高出三分之一。个人认为,如果简单套用DGX-2的架构,整体的供电需求有可能突破12kW,机箱高度又不增加的话,传统的风冷方案恐怕难以为继。相比之下,现在的方案把每U的功率密度维持在与DGX-1/2相当的水平,可以说是相当的克制了。

总体而言,虽然在Scale-up方向所达到的绝对能力上,DGX A100超越了DGX-2,但是在构建更大系统的路线选择上,DGX A100更倾向于Scale-out。以DGX SuperPOD为例,4名操作人员仅需不到1个小时,就能组装起一套由20台系统组成的DGX A100集群,2 PFlops的性能足以被列入TOP500榜单。

通过添加NVIDIA Mellanox InfiniBand交换机层,工程师将14套分别配置有20台DGX A100系统的集群相连接,创造出了具有:

- 280台DGX A100系统

- 2240个NVIDIA A100 GPU

- 494台NVIDIA Mellanox Quantum 200Gb/s InfiniBand交换机

- 56 TB/s网络架构

- 7PB高性能全闪存

的Selene系统,可以提供超过1 EFlops的AI性能,而搭建时间还不到一个月。

正如NVIDIA所言,“此类系统能够在标准数据中心的功率和散热能力承担范围内轻松运行”。对专业的超算系统而言,10kW的供电能力也好,某种形式的液冷也罢,都不算个事儿。但是,当定位放宽到相对大众化的ABC市场,不能不考虑用户环境的承受力,期待DGX/HGX A100在AI和云计算领域的表现。