本文讨论如何在Verilog中的实现不同的赋值,以及它们在逻辑综合中会推断出什么样的电路。

1、当对同一个net,使用多个assign语句,会综合出什么样的逻辑?

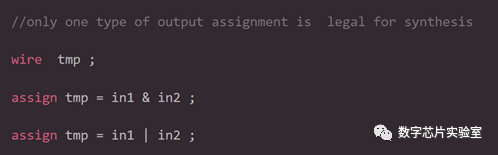

在可综合的verilog代码中,为同一个net使用多个assign语句是错误的。综合工具会报出语法错误,即“net is being driven by more than one source”。 例如,以下是错误的:

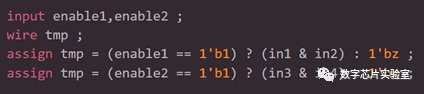

但是,使用多个assign来驱动三态net 是合法的语句,如下示例所示:

2、条件赋值在逻辑综合时会推断出什么电路?

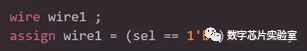

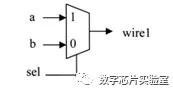

条件赋值通过“?:”实现。 条件赋值在逻辑综合时被推断为MUX。 例如,以下示例是一个简单的MUX:

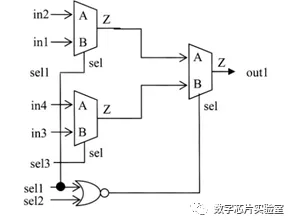

3、条件赋值嵌套会综合出什么样的电路?

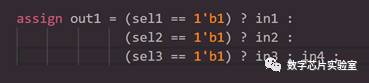

如下例所示,条件赋值嵌套会被综合成MUX “tree ”:

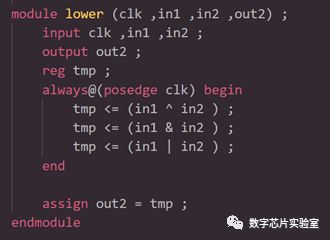

4、 在同一个always语句块中,对同一个reg变量多次赋值会综合出什么电路 ?

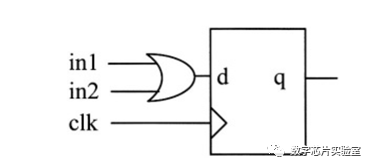

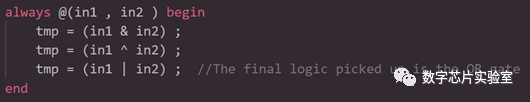

在同一个always语句块中,对同一个reg变量进行多次非阻塞赋值时,逻辑综合时会选择最后一个赋值。 例如:

在刚刚的示例中,OR逻辑是最后一个赋值。因此,综合出来的逻辑是OR门。 如果最后一个赋值是“&”运算符,它会综合成一个AND逻辑。

对于组合逻辑中always语句块中的阻塞赋值来说,情况也是如此。

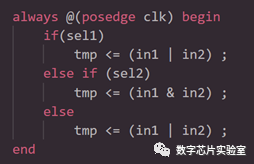

如果多次赋值通常存在于if-else或case语句中。 例如:

在这种情况下,在每个时钟周期仅执行一个唯一的赋值。

在上面的例子中,没有关于哪个语句会被执行赋值的歧义,因为分支控制是明确定义的。

5、为什么时序逻辑应该用非阻塞赋值,如果用阻塞赋值会发生什么?并且与组合逻辑进行比较。

阻塞赋值和非阻塞赋值之间的主要区别是阻塞赋值中的RHS会被立即赋值到LHS,而非阻塞赋值,LHS的赋值是发生在RHS值被计算之后。

以下说明了在时序逻辑中使用阻塞赋值和非阻塞赋值的不同场景:

5.1、 在时序逻辑中使用阻塞赋值

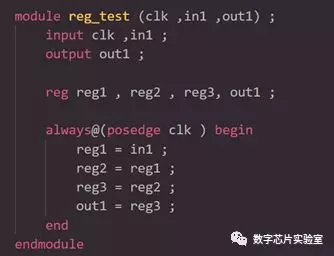

以下是时序逻辑中使用阻塞赋值的Verilog模块示例:

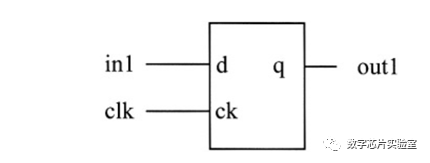

在上面的例子中,reg1,reg2,reg3,out1都是阻塞赋值。 综合结果是单个FF触发器,输入为in1,q输出为out1,如下图所示:

这是因为in1和out1之间的中间结果是以阻塞赋值形式存储在reg1,reg2和reg3中。 结果,对out1的RHS最终计算会被立即赋值到out1, reg1,reg2和reg3已经通过综合进行了优化。

5.2 、 在时序逻辑中使用非阻塞赋值

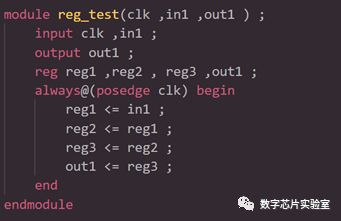

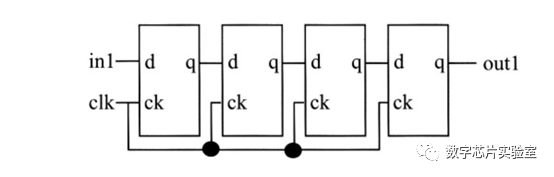

以下代码示例了时序逻辑中使用非阻塞赋值:

在上面的例子中,reg1,reg2,reg3,out1为非阻塞赋值。 综合结果为4个触发器。

这是因为in1和out1之间的中间结果是以非阻塞赋值存储在reg1,reg2和reg3中。在这种情况下,输出是由clk事件控制的移位寄存器。

5.3 、在组合逻辑中使用阻塞赋值

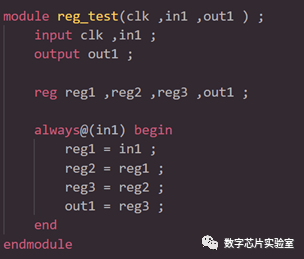

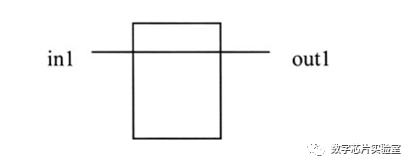

以下示例说明了组合逻辑中的阻塞赋值的用法:

在上面的使用阻塞赋值的组合逻辑语句中,没有posedge,并且“<=”被“=”替换。 由此综合的逻辑很简单,是in1到out1之间的连线。

这是因为所有的赋值都是立即执行的,没有需要等待的事件。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s?\_\_biz=MzU4ODY5MzkzOA==&mid=2247484283&idx=1&sn=2e935c69067f1864d6edd826cc17c1b8&chksm=fdd9aba6caae22b0a6a1286c58849f6e1c516d7f1a76e6ad42ba1a7b217bcda379edabf23a3f&scene=21#wechat\_redirect

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏