1、function中的逻辑被综合成了什么?

由于function中没有任何时序结构,function只能综合出组合逻辑。

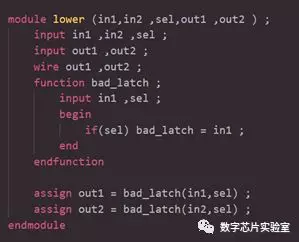

例如,以下function有2个输入信号和一个控制信号,输出算术运算结果。

2、Verilog function有哪些重要的注意事项?

2.1 每次调用function时,局部变量和返回值都被赋值,否则将导致形成锁存器。 例如,以下示例中,if条件语句没有else语句。也就是说,如果sel是false,该function将返回其先前调用的值,就好像结果被锁存住了。

2.2 fucntion只用于综合成组合逻辑。但是,fucntion的最终结果可以用作D触发器的输入。

2.3 fucntion不应包括延迟(#)或事件控制(@,wait)语句。

2.4 fucntion可以调用其他fucntion,但不能调用task。

2.5 fucntion在调用时会返回一个值。

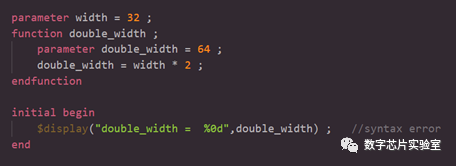

2.6 fucntion内声明的parameters,作用范围仅在本地,并且不能在fucntion之外使用。 在以下示例中,width参数在函数之外声明,double\_width参数在函数内声明。

3、task中的逻辑被综合成了什么?

虽然在task中可以有@等时序控制结构中,它仅适用于仿真。综合工具会忽略所有task中的时序结构。因此,如果task中存在时序控制结构,可能会存在仿真和综合不匹配的现象。

因此,在可综合verilog中一般只会使用task综合基本的组合逻辑,在testbench中调用带有时序控制结构的task具有较好的通用性。

以下是组合逻辑task的示例,即comb\_task,执行输入in1的位或(OR)。 注意int\_out1和int\_out2的声明是reg型,因为task的输出只能通过reg而不是wire接收。

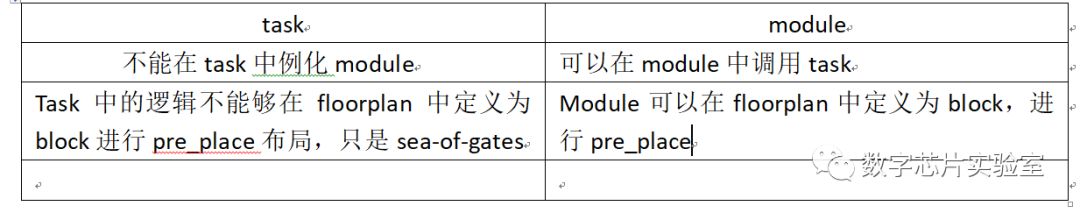

4、使用task和module实现可重用逻辑有什么区别?

下表总结了两种方法之间的差异:

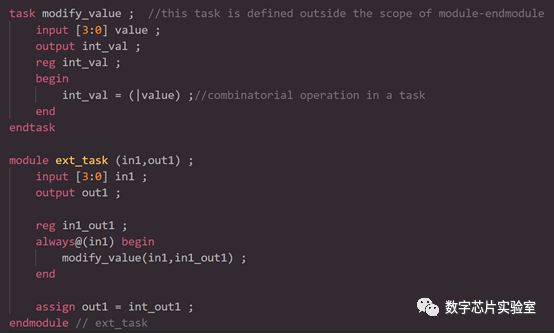

5、task和fucntion是否可以在module-endmodule之外声明么?

可以。 在SystemVerilog中,可以在module-endmodule外声明task和function。在Verilog-1995或Verilog-2001中是不可以的,会产生编译错误。例如,以下代码中,在module-endmodule范围之外声明了task modify\_value。

同样,在使用SystemVerilog中,function-endfunction也可以在同一文件中的module-endmodule范围之外声明。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s?\_\_biz=MzU4ODY5MzkzOA==&mid=2247484293&idx=1&sn=92cf938f4b78a3bebbf647e43cab13d9&chksm=fdd9ab58caae224efa7deebcc083b0b68411ac11f0237d1a6daf763339a88dcdeb016d13af79&scene=21#wechat\_redirect

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏