作者:王超

首发:电子电路开发学习

实现思路

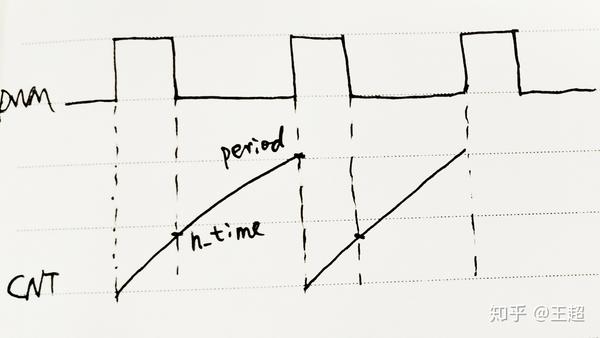

实现方法很简单,使用一个计数器一直计数,然后和两个值进行比较,一个值是高电平时间h\_time,一个值是周期period,在小于h\_time期间,输出高电平;大于h\_time期间,输出低电平,到达周期period时,计数器清零。

端口说明

- clk:时钟信号

- nreset:复位信号,低电平复位,输出为0

- en:使能信号,高电平使能输出,低电平输出为0,

- period:PWM的周期,如主时钟96M,产生4MHz的波形,则period = 96/4 = 24

- h\_time:高电平的时间,如主时钟96M,产生4MHz,占空比25%的波形,则h\_time = 24 * 0.25 = 6

- pwm:PWM波输出

源程序

pwm\_gen.v

module pwm_gen(

input nreset,

input clk,

input en,

input [15:0] period,

input [15:0] h_time,

output reg pwm

);

reg [31:0] CNT;

always @ (posedge clk)

begin

if(!nreset)

CNT <= 0;

else if(CNT >= period - 1 )

CNT <= 0;

else

CNT <= CNT + 1;

end

always @ (posedge clk)

begin

if(!nreset)

pwm <= 0;

else //nreset = 1

begin

if(en == 0)

pwm <= 0;

else //en = 1

begin

if(CNT <= h_time - 1)

pwm <= 1;

else

pwm <= 0;

end

end

end

endmodule实际应用

可产生任意占空的PWM波,若主时钟为96MHz。

- 产生4MHz,50%占空比:period = 24,h\_time = 12;

- 产生3KHz,50%占空比:period = 32000,h\_time = 16000;

- 产生宽度10us,间隔100us的脉冲信号:period = 10560,h\_time = 960;

推荐阅读

- 全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程

- Keil开发环境下添加AStyle插件对C代码进行格式化处理

- 除了ZYNQ还有哪些内嵌ARM硬核的FPGA?

- 【踩坑】STM32外部8M不起振会有什么现象?

欢迎关注公众号:电子电路开发学习,id:mcu149。

更多电子电路、单片机、嵌入式、物联网等技术文章欢迎关注电子电路开发学习专栏。