Google在近期搞了个芯片业的大新闻,也就是和工艺代工厂SKYWATER合作,开源了后者的Sky130 Hybrid 180nm/130nm 的PDK(Process Design Kit)来免费给任何人使用。不仅如此,Google还打算首批征集最多40个设计来'免费'帮助大家流片。

在这里简单介绍一下PDK是什么。一般来说芯片在设计之初就需要从代工厂获取相关的工艺信息,包括但不限于:设计规则文档和文件、晶体管spice仿真库、各种EDA工具所需要的tech文件、standard cell以及IP的各类库文件(verilog, gds, cdl, lef, lib, spice)等。其中部分可能由第三方IP公司提供,但是绝大部分都可以从代工厂获得。这些东西的获取一般都不是无偿的,会花费相当大的费用,即使是很老的工艺也可能至少需要几千刀,对很多小公司、研究机构和个人研究者相当不友好。流片费用更不用说,比PDK的费用只多不少,因此整体上的芯片设计和流片门槛比较高。

本次开源的PDK工艺虽然不先进,但是个人认为对整个行业来说意义不小,尤其是对研究机构和个人来说,能够拿到真正可以流片的PDK可以使大家可以把自己的很多想法付诸实践,更重要的是此PDK支持开源layout工具,进一步减轻了开发者的负担。

那么这次的PDK包含了哪些内容呢?首先本工艺的基本信息如下:

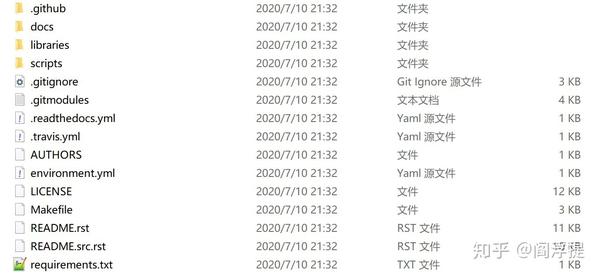

我这边已经开始尝试获取它。不过由于本次PDK不仅包含工艺文件和文档,还包含不同类standard cell的各种库文件,目测文件量不小于20G,目前还没有完全下载完,不过已经可以尝尝鲜看看里面有什么东西了。该PDK放在github上托管,任何人都可以下载,其git下来的顶层目录结构如下:

不过由于库文件太大,没法放在一个repository中,因此要获取全部的文件还要再多花几步。进入到libraries下面,可以看到次级目录中standard cell库文件的目录:

drwxr-xr-x 1 yanfuti 197121 0 7月 10 21:32 libraries/sky130_fd_sc_hd/latest

drwxr-xr-x 1 yanfuti 197121 0 7月 10 21:32 libraries/sky130_fd_sc_hdll/latest

drwxr-xr-x 1 yanfuti 197121 0 7月 10 21:32 libraries/sky130_fd_sc_hs/latest

drwxr-xr-x 1 yanfuti 197121 0 7月 10 21:32 libraries/sky130_fd_sc_ls/latest

drwxr-xr-x 1 yanfuti 197121 0 7月 10 21:32 libraries/sky130_fd_sc_ms/latest进入到每个目录下的latest后,分别下载下来有以下几种文件:

cd sky130_fd_sc_hd/latest

ll

drwxr-xr-x 1 yanfuti 197121 0 7月 10 22:09 cells

-rw-r--r-- 1 yanfuti 197121 11560 7月 10 22:09 LICENSE

drwxr-xr-x 1 yanfuti 197121 0 7月 10 22:09 models

-rw-r--r-- 1 yanfuti 197121 221 7月 10 22:09 README.rst

drwxr-xr-x 1 yanfuti 197121 0 7月 10 22:09 tech

drwxr-xr-x 1 yanfuti 197121 0 7月 10 22:09 timing其中cells包含每个standard cell的各种格式的库文件,如verilog, lef, gds, cdl, test\_model。models目录下包含了几种类型的DFF所需要的verilog/system verilog model。tech目录下面包含的是tech lef。timing目录下则是各种PVT条件下的.lib.json,至于.lib文件在哪里,这个我还在下载,由于文件过大,需要额外的步骤才能获取。

除了工艺库,还有对开源layout工具'Magic'的setup文件和tech文件。这个工具我个人没听过也没用过,不作详述。除此之外,还有一些IP的库文件也包含其中。

magic/ magic techfiles, startup file, PDK script, and key binding script.

netgen/ netgen setup file

qflow/ qflow scripts and graywolf setup files.

klayout/ setup files for klayout

openlane/ setup files for openlane

sky130_fd_io/ Standard I/O

sky130_fd_pr_base/ Primitive devices w/fixed layout

sky130_fd_pr_rf/ RF primitive devices w/fixed layout

sky130_fd_pr_rf2/ Additional RF primitive devices w/fixed layout本来以为rf*类的文件是register file类的memory,但是细看应该是混合信号用到的RF。不过本次PDK的目标设计主要是入门级数字和混合信号设计,因此有这些IP也不奇怪。

尽管如此,我翻了一遍没有在里面发现memory compiler,PLL等SoC设计需要的IP,而且也没有商业APR工具所需的工艺文件如ICC/ICC2的.tf和.tluplus或者itf, StarRC用的.nxtgrd, QRC用的.qrcTechFile或者ict/cap table等,更没有IR-Drop和EM分析所需的工艺文件和DRC/LVS/Antenna/ESD分析验证的rule deck,略微有点失望。整体看下来数字设计的话暂时只能跑跑DC综合,如果带memory的话只能用register搭,芯片规模比较受限。

后面我会继续深挖PDK的内容给大家带来更多信息,同时我也会持续关注它的官方更新和后续消息,毕竟这个只是试试水,如果反应好的话Google表示还有可能继续开源更多东西。这个PDK完全下载好之后如果大家也有兴趣我会想办法分享给大家,敬请期待。

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。