今天想和大家聊聊一种比较特别的功耗控制方法:Body Bias。由于它会涉及一些半导体器件的相关知识,我们尽量详细地从基础上向大家介绍它的原理。

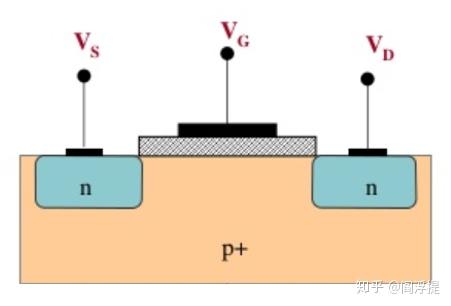

一般我们认为一个CMOS晶体管有三个常用端口,分别为源极(Source)、漏极(Drain)以及栅极(Gate),也就是下面这张我们经常看到的截面图:

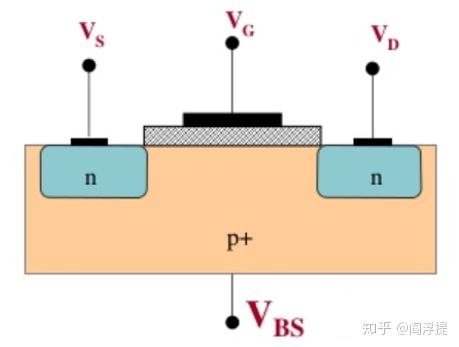

然而实际上CMOS晶体管还有一个不太常提到的端口,称为衬底连接,也就是连接到p-substrate或者n-well上的端口。因此一个真正的CMOS晶体管其实是一个四端器件:

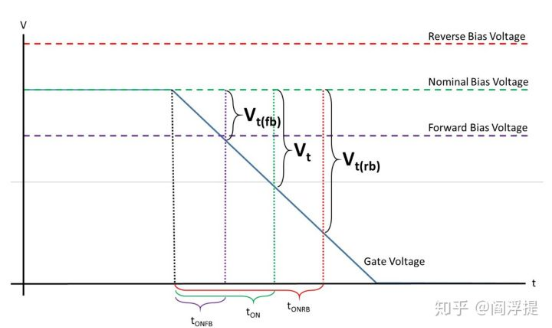

上图中加在p-substrate或者n-well上的这个电压 ,被称为衬底偏置电压,其中B代表Body,也就是n-well或者p-substrate。在大多数情况下,这个电压根据晶体管的类型接到VDD或者VSS上,这种情况就是无衬底偏置;而在某些情况下可能会加一个正向或者反向的偏置电压,分别称为Forward Body Bias和Reverse Body Bias,简称FBB和RBB。

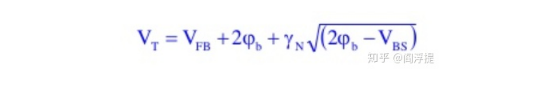

那么加偏置电压的目的是什么呢?这就要涉及CMOS器件中的一种特殊现象:体效应,或称衬底偏置效应。虽然它的原理比较复杂,但是其表现形式却非常简单明了:衬底的偏置电压会影响晶体管的阈值电压。阈值电压 的公式如下所示:

从公式中我们可以看出,阈值电压 可以随着偏置电压 的变化而变化,简单来说加适当的偏置电压可以使 变小,反之也可以使 变大,具体的影响如下图所示:

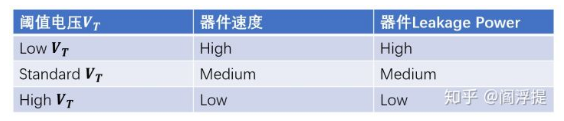

而 的大小对于功耗的影响我们在之前的文章中提到过,没有印象的同学可以再温习一下这篇文章【低功耗设计基础:Multi-Vth】,简单可以总结如下:

至此,Body Bias的功耗控制原理应该也就比较清晰了:芯片设计者可以通过控制偏置电压来动态调整大量standard cell的阈值电压,假如芯片整体或者部分功能模块在某些时候对性能要求不高,则可以提高 的电压值来降低leakage;反之在性能要求高的时候可以通过偏置电压降低 的值来使standard cell实现更小的延迟和更快的速度。

尽管Body Bias在理论上是很有效的,然而在实际设计中,如果要真的要实现Body Bias,则至少有几个方面需要特殊关注:

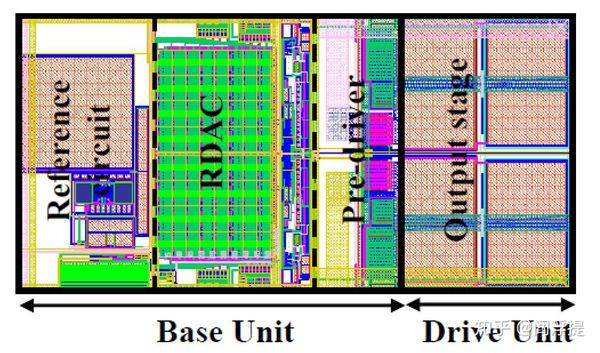

1) 偏置电压的产生和控制模块的设计

这个控制模块一般称为Body Bias Generator,简称BBG或者BBGen。由于偏置电压的调整是动态且随着系统的工作模式而不断变化的,那么这个电压的调整模块最好放在芯片内部从而能够方便地监控系统负载并快速响应和调整。但是这样做的代价是会增加芯片的面积而带来额外的成本和功耗,因此设计者需要根据实际需要权衡加入BBGen的代价是否值得。除此之外,一个输出电压信号范围较广且质量较好的BBGen需要花费额外的设计时间或者可能需要额外的成本来购买IP,都会给芯片设计本身增加难度和成本。由于BBGen的设计本身比较偏模拟而非我们研究的方向,在此不做过多说明(其实我也不懂...),有兴趣的同学可以自行查阅相关的设计资料。

BBGen Layout设计实例

2) 衬底偏置的连接

从CMOS晶体管的结构我们可以看出,偏置电压需要加到每一个需要偏置的晶体管上。而反映在后端设计上就是所有需要偏置的standard cell都需要连接衬底偏置。如果在少量cell上加偏置显然不值得我们花费这么大的代价,但如果芯片的大部分模块甚至全部都需要连接偏置,那么就需要设计特殊的电源网络将大量standard cell的n-well和p-substrate连接到偏置电源,不仅增加设计周期,还会占用很多额外的绕线资源。

3) 时序分析和signoff的复杂度增加

为了准确分析每一个cell在不同偏置状态下的delay变化,就需要cell的时序库文件中包含不同偏置电压下的delay信息,或者需要知道不同的偏置电压cell的delay变化数据,从而能够在PnR的时序优化和STA中准确地加以模拟和分析;为了保证在不同的偏置下系统仍然能够正常工作,STA的signoff条件也会相应的增加,从而保证所有状态下的setup/hold等条件都能够得到满足。

基于上述问题,在实际设计中,为了降低设计和signoff的复杂度,通常只会选取FBB和RBB中的一种,并且偏置电压只会是一个固定数值。换句话说,在同一个设计中很少会出现既有正向偏置又有反向偏置的情况,而且偏置电压也不会出现在某个范围内波动的情况。在这样的取舍下,可以有效降低从前端到后端和signoff的复杂度,并且能够在功耗上实现比较理想的控制。

至此,关于Body Bias技术的基本原理就讲完了。而它本身的提出和应用其实和另外两项技术息息相关,分别是DVFS和FD-SOI,我们将会在接下来的文章中陆续介绍它们,敬请期待。

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。