IC Designer可以在设计的不同阶段采用基于Architectural或者Process的方法来降低功耗,设计者需要根据功耗、性能、成本和可靠性等因素折衷选择低功耗策略。

1、基于Architectural的低功耗设计技术

1.1. Clock Gating :

该技术是非常流行的动态功耗降低技术,由于动态功耗与Cell的信号切换直接相关。

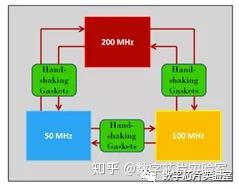

1.2.Variable Frequency/Frequency Islands :

在芯片中,并非所有模块都需要在非常高的频率工作,(例如I2C,UART等慢速通信模块)。因此,通过向不同的模块提供不同频率的时钟,可以减少整体的动态功耗。

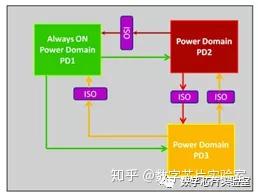

1.3. Power Gating :

在某些低功耗应用中,芯片中的某些模块处于睡眠模式,只需要一部分模块进行工作。在这种情况下,可以关闭不需要工作的模块,从而降低动态功耗和静态功耗。

但是,在应用Power Gating技术时,designer必须确保功能模块不受影响。为此,需要放置isolation cell,如下图所示。

2、基于Process的低功耗设计技术

2.1 Multi Threshold Voltage CMOS Cells :

许多MOS管的特性受阈值电压影响。

当阈值电压VT增加时,泄露功耗降低。但是, VT的增加对工作频率有负面影响。因此,designer可以混合使用低VT和高VT的Cell,在保持所需工作频率的同时减少泄露功耗。

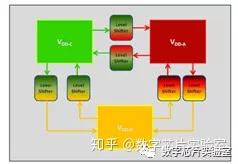

2.2 Mutli VDD Technique :

动态功耗和电源电压成二次方关系,但是当电源电压降低时对工作频率也有负面影响。

所以, designer也需要折衷考虑电源电压对工作频率和动态功耗的影响,在保持所需工作频率的同时减少动态功耗。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/gsNDIxfEYcsLNxW-yegtLg

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏