有5个uvm component class:A, B, C, D, E,需要把一个transaction从A通过B, C, D传到E,怎么传输?

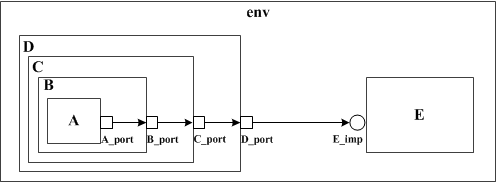

方法一:使用TLM通信传输,利用多层PORT端口级联实现,如图1所示。

图1 多层PORT连接

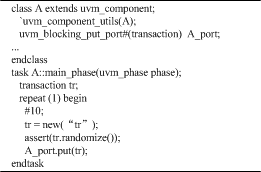

A component的代码为:图2 A component代码

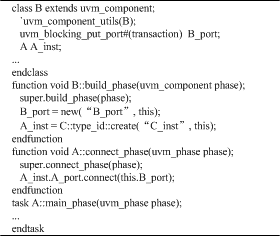

B component的代码为:

图3 B component的代码

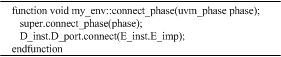

C component和D component的代码类似于B component。在每个component中定义一个uvm_blocking_put_port端口(PORT)和次内层component的句柄,然后再build_phase中实例化,最后在connect_phase中连接起来。

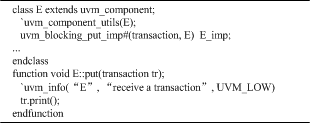

E component的代码为:图4 E component的代码

env的代码为:图5 env的代码

TLM是Transaction Level Modeling(事务级建模)的缩写,它起源于SystemC的一种通信标准。TLM通信中有三个常用的术语:put操作、get操作和transport操作。有三种端口PORT、EXPORT和IMP。在UVM中,只有IMP才能作为连接关系的终点,如果PORT或者EXPORT作为终点,则会报错。

除了以上三种端口外,UVM中还有两种特殊的端口:analysis_port和analysis_export,用于传递transaction。analysis_port和analysis_export如果直接相连会出错,只有在analysis_export后面再连接一级uvm_analysis_imp才不会出错。

在此基础上,可以引入FIFO来进行通信,FIFO的本质是一块缓存加两个IMP。FIFO中的analysis_export和blocking_get_export虽然名字中有关键字export,但是其类型却是IMP(uvm_analysis_imp)。

不过无论使用FIFO还是使用IMP,都能实现同样的目标,两者各有其优势与劣势,在实际应用中,读者可以根据自己的习惯来选择合适的连接方式。

更多相关阅读

UVM中Virtual sequence的作用

UVM如何debug objection

作者:谷公子

首发博客:https://blog.csdn.net/W1Z1Q/article/details/104358385

更多IC设计相关的文章请关注IC设计极术专栏,每日更新。