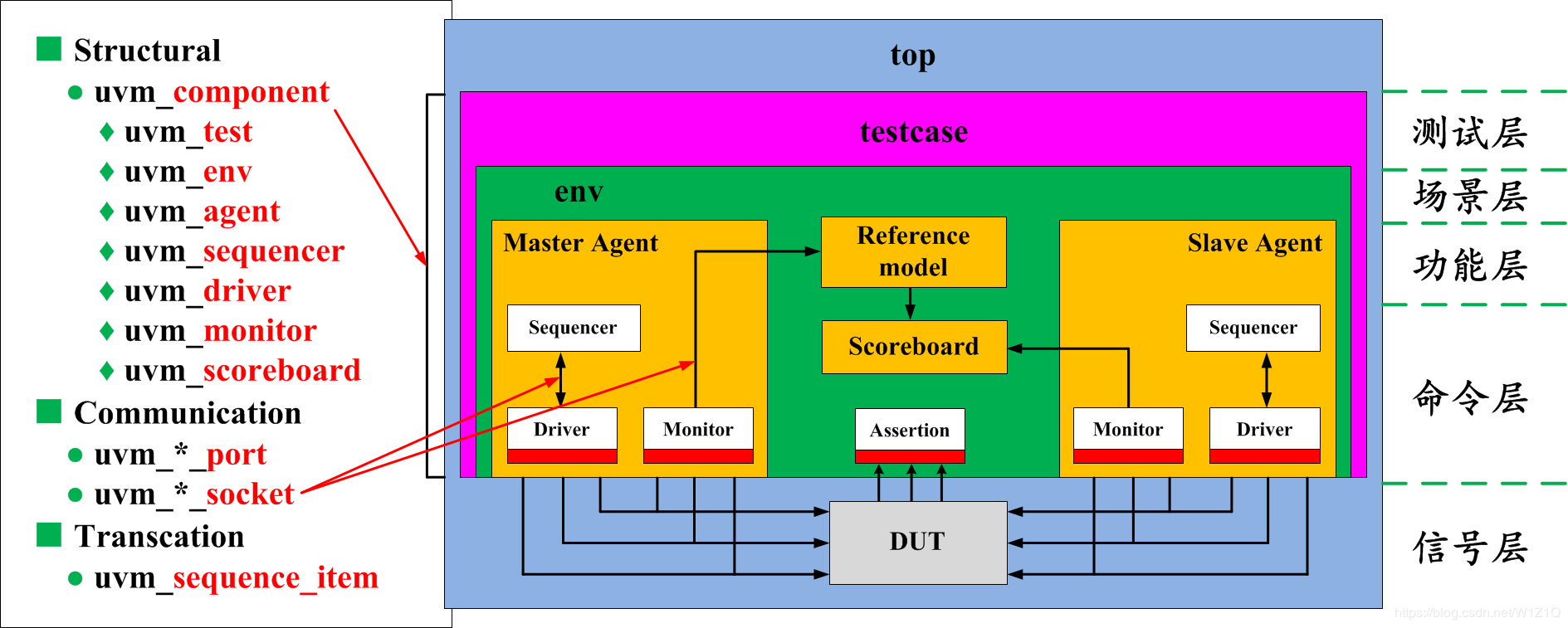

对于验证方法学来说,分层的测试平台是一个关键的概念。虽然分层似乎会使测试平台变得更复杂,但它能够把代码分而治之,有助于减轻工作负担,而且重复利用效率提升。验证平台可以类似分为五个层次:信号层、命令层、功能层、场景层和测试层。

图 UVM验证平台

UVM的基本元素(建模方法)有:uvm object, uvm component, uvm factory, uvm TLM, Message service, configuration mechanism, RAL。

UVM组件(uvm component)包含有:uvm_driver, uvm_monitor, uvm_sequencer, uvm_agent, uvm_scoreboard, uvm_env, uvm_test。每个组件的作用如下:

uvm_driver: 所有的driver都要派生自uvm_driver。driver的功能主要就是向sequencer索要sequence_item(transaction),并且将sequence_item里的信息驱动到DUT的端口上,这相当于完成了从transaction级别到DUT能够接受的端口级别信息的转换。

uvm_monitor: 所有的的monitor都要派生自uvm_monitor。Monitor做的事情与driver相反,driver向DUT的端口上发送数据,而monitor则是从DUT的端口上接收数据,并且把接收到的数据转换成transaction级别的sequence_item,再把转换后的数据发送给scoreboard,供其比较。

uvm_sequencer: 所有的sequencer都要派生自uvm_sequencer。sequencer的功能就是组织管理sequence,当driver要求数据时,它就把sequence生成的sequence_item转发给driver。

uvm_agent: 所有的agent要派生自uvm_agent。agent只是把driver和monitor封装在一起,根据参数值来决定是只实例化monitor还是要同时实例化driver和monitor。agent的作用主要是从可重用性的角度考虑的。如果在做验证平台时不考虑可重用性,那么agent其实是可有可无的。

uvm_scoreboard: 一般的scoreboard都要派生自uvm_scoreboard。scoreboard的功能就是比较reference model和monitor分别发送来的数据,根据比较结果判断DUT是否正确工作。

uvm_env: 所有的env要派生自uvm_env。env将验证平台上用到的固定不变的component都封装在一起。这样,当要运行不同测试用例时,只要在测试用例中实例化此env即可。

uvm_test: 所有的测试用例要派生自uvm_test或其派生类,不同的测试用例之间差异很大,所以从uvm_test派生出来的类各不相同。任何一个派生出的测试用例中,都要实例化env,只有这样,当测试用例在运行的时候,才能把数据正常地发给DUT,并正常地接收DUT的数据。

另:还有一个component比较重要reference model,UVM中并没有针对reference model定义一个类。所以通常来说,reference model都是直接派生自uvm_component。reference model的作用就是模仿DUT,完成与DUT相同的功能。DUT是用Verilog写成的时序电路,而reference model则可以直接使用SystemVerilog高级语言的特性,同时还可以通过DPI等接口调用其他语言来完成与DUT相同的功能。

UVM中还有一个比较常用的元素uvm_sequence_item,它不构成UVM树,但在UVM中,所有的transaction都要从uvm_sequence_item派生,只有从uvm_sequence_item派生的transaction才可以使用UVM中强大的sequence机制。而且transaction是有生命周期的,必须使用uvm_object_utils注册,不能使用uvm_component_utils注册。还有uvm_sequence也不属于UVM树,但是它和sequencer之间有密切联系。只有在sequencer的帮助下,sequence产生出的transaction才能最终送给driver;同样sequencer只有在sequence出现的情况下才能体现出价值。sequence就像是一个弹夹,里面的子弹是transaction,而sequencer是一把枪。弹夹只有放入枪中才有意义,枪只有在防腐弹夹后才能发挥威力。uvm_sequence_item和uvm_sequence均属于uvm_object,不构成UVM树节点。

断言(Assertion):断言穿过命令层和信号层,它们负责监视独立的信号以寻找穿越整个命令的信号变化。可以使用SystemVerilog断言(SVA)在你的设计中创建时序断言。断言的例化跟其它设计块的例化相似,而且在整个仿真过程中都是有效的。仿真器会跟踪哪些断言被激活,这样就可以在此基础上收集功能覆盖率的数据。

更多相关阅读

UVM中的PHASE类别及PHASE同步

UVM中启动sequence的方法

作者:谷公子

首发博客:https://blog.csdn.net/W1Z1Q/article/details/100863836

更多IC设计相关的文章请关注IC设计极术专栏,每日更新。