本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

转载自:知乎

欢迎来到深入 AXI4 总线的实战篇,在第一篇文章中,我们将搭建起我们的 AXI 仿真系统,帮助我们更好、更快地理解与运用 AXI 总线。

目前,仿真平台基于 Xilinx Vivado 中的 AXI Verification IP 的 EXAMPLE 工程,如何建立工程可以参阅下方的 Xilinx 论坛的相关文章[1]。

AXI 基础第 2 讲--使用 AXI Verification IP (AXI VIP) 对 AXI 接口进行仿真xilinx.eetrend.com

此外还可以参考 PG267 AXI VIP 文档[2]

后续,考虑寻找一些开源的 IP 来更新我们的仿真平台,毕竟大部分 ICer 和使用 I 家平台的 FPGAer 应该没有兴趣下载一个炒鸡大的 Vivado 。此外笔者看到新思也有 AXI VIP ,后续了解下,关于仿真平台欢迎读者提出你的想法。

搭建平台

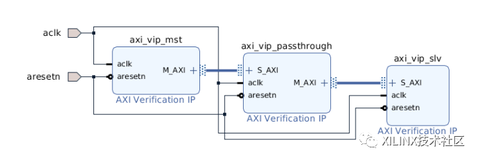

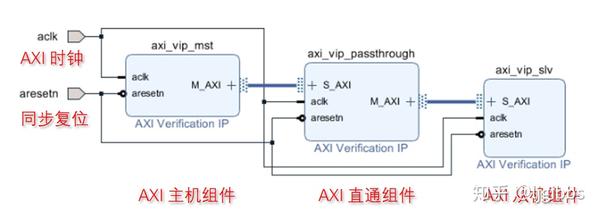

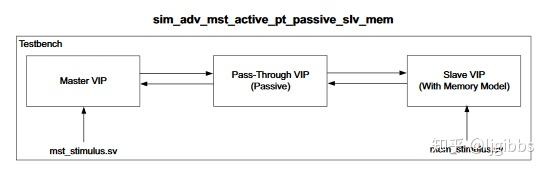

根据参考文献[1]中的教程,我们很方便地基于 AXI VIP 示例工程完成了基础平台搭建,结构如下图所示

由参考文档[1]可知 :AXI VIP 具有以下功能:

- 生成 Master AXI 指令和写内容

- 生成 Slave AXI 读内容和写响应

- 检查 AXI 传输是否符合协议标准

它支持 5 种不同配置:

- AXI Master VIP

- AXI Pass-through VIP(有/无内存模型)

- AXI Slave VIP(有/无内存模型)

参考工程中的基础平台包括了三个 AXI VIP,分别配置为主机、直通以及从机模式,工作模式在 IP 配置界面设定。

可以看到平台的外部信号仅包括时钟以及复位信号,总线事务激励都在内部发起。

值得注意的是 Xilinx AXI VIP 的源文件以及 testbench 均基于 SV 以及 UVM 开发,可能需要相关知识。(不过没事,笔者也只懂一点点,用到再学嘛)

Example TB

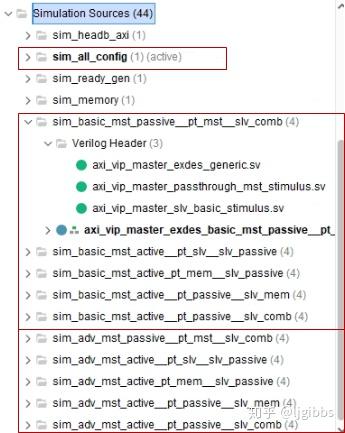

接下来我们参观下示例工程提供的 testbench。洋洋洒洒提供 13 个 TB 文件,下图中第一个 tb 是笔者自己新建的,我们后续在其中创建我们自己的测试逻辑。

这些 tb 防置在不同的 set (就是文件夹)中,右键选择 active ,即可激活所要运行的 set。

我们首先来看第一个红框中的 set :sim\_all\_config,对应 tb 中演示了一系列 VIP 特性的使用,并且使用了不同的调用方法。简单来说有新旧两版 API,旧版类似于 VIP 的前身 BFM 的使用方法。我们不管这些,一般使用新的 API,后续会详细讨论。

接下来看下方两个红框,分别有 5 个 sets,总共有 10 个。这些 tb 分为 basic 和 advanced 两类,用于演示不同通信场景下的基础或进阶特性。可以从他们 set 的名字来区分所属的场景,并按需使用:

sim_<basic or adv>mst<mode>\_\_pt_<mode>\_slv<mode>

其中 mst、pt、slv 分别表示平台中的三个 VIP,其后跟有不同的 <mode> 表示其在该场景下的工作模式。

简单来说,active 代表该场景下该 VIP 正在工作,passive 表示不工作。

对于从机使用 mem/combo 均表示从机正在工作,区别为有/无内存模型。

对于 pass-through(简称 pt),mst、slv 表示其工作于主机/从机模式,从机模式下无内存模型。mem 则表示其工作于有内存模式的从机模式。

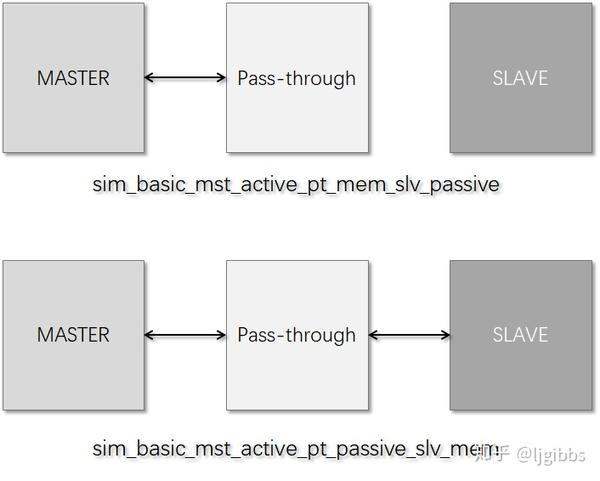

好了,我们来举个例子:sim\_basic\_mst\_active\_pt\_mem\_slv\_passive 表示的场景中:

主机正常工作,从机不在工作。此时只有主机与 pt 通信,pt 工作于有存储模型的从机模式。换句话说该场景简化为主机与 pt 的双机通信,没从机什么事。

而在 sim\_basic\_mst\_active\_pt\_passive\_slv\_mem 场景中,实际上是主机与从机通信,pt 只是做一下传递工作。两者场景如图所示

在这些场景 tb 中,实际起作用的分别是应用的 3 项模块,在 Verilog Header 下拉可以看到。所有场景都使用了 generic\_tb.sv 模块,该模块对双方的通信进行检查。

另外两项模块分别驱动通信中的 master 与 slave,按照场景有所不同,我们以 sim\_basic\_mst\_active\_pt\_passive\_slv\_mem 为例:

mst\_stimulus.sv 与 mem\_stimulus.sv 作为激励分别驱动主机与从机,其中从机具有存储模型。其他场景可以以此类推。

波形仿真工具

接下来,我们运行一个 tb 来观察下具体的波形,并熟悉我们的波形工具,比如我们运行 sim\_all\_config :

这里我们使用 vivado 内置的仿真器 vivado simulator 进行仿真。为什么不用更常用、速度更快的 Modelsim,后文有惊喜。

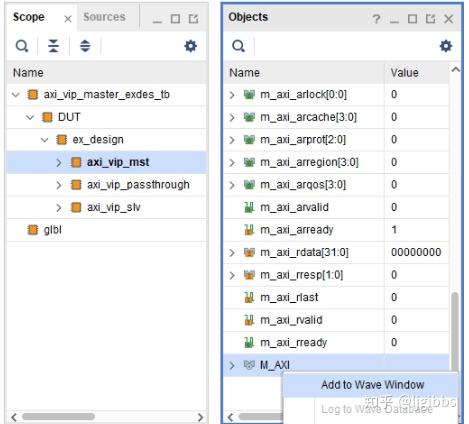

active sim\_all\_config ,run simulation,然后按照下图将总线添加到波形窗口中,注意是总线而不是单独的信号,不然就没有惊喜了。

诶,然后惊喜来了,花里胡哨!什么玩意?!但我们仔细瞧瞧,会发现这个 AXI 波形仿真非常好用。

我们仔细来看看,最上方显示的是当前的传输事务状态:读写事务同时进行、单独的读或者写事务以及空闲状态。

下方框内标识了当前 outstanding 的,“在途”,或者说进行中的传输事务数量。

最下方分别列出了 5 个通道,默认状态下不会显示具体的信号。其中的小方块表示当前通道上存在有效的数据,可以通过最左端的箭头展开查看。

当你将鼠标放在小方块上时,会显示该数据所属 burst 的序号、地址、突发传输信息以及其他属性。当你选中小方块后,会高亮显示这个 burst 的一系列信号。以下图为例,高亮显示了 burst 的写地址、写数据以及写回复信息,并通过带有箭头的直线相连。这样一来,无论多复杂的信号都可以一目了然了~

总结

本文基于 Xilinx AXI VIP 的示例工程搭建了仿真平台,并初步了解仿真平台的 testbench 以及工具的使用。后续的实战篇中我们一方面继续通过示例工程学习 AXI VIP 的 API 调用。另一方面,也将结合理论篇的文章,对 AXI 总线进行一番实战。

如果大家对仿真平台的搭建有问题,可以参见文献 [1],那里的步骤更详细。

如果想要进一步了解 AXI VIP 的示例工程以及提前自学 API,可以参见文献 [2],这是 IP 的产品手册,上面详细阐述了示例工程的组成以及调用的方法与 API。

推荐阅读

- 可重构计算:基于FPGA可重构计算的理论与实践 1.器件架构 译文(三)

- 可重构计算:基于FPGA可重构计算的理论与实践 1.器件架构 译文(二)

- 可重构计算:基于FPGA可重构计算的理论与实践 1.器件架构 译文(一)

关注此系列,请关注专栏FPGA的逻辑