转载自:知乎

首先附上传送门:

https://hdlbits.01xz.net/wiki/Exams/m2014\_q4e

Problem 45 NOR

实现如下电路:

解析: 一个或非门

module top_module (

input in1,

input in2,

output out);

assign out = ~(in1 | in2);

endmodule

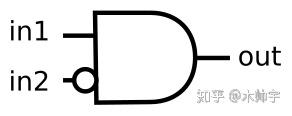

Problem 46 Another gate

实现如下电路:

解析:一个与门,但输入in2需要取反。

module top_module (

input in1,

input in2,

output out);

assign out = in1 & (~in2);

endmodule

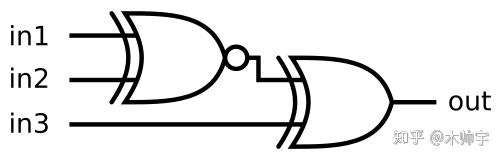

Problem 47 Two gates

实现如下电路:

解析: 如上图所示, 一个异或门,一个同或门,我声明一个wire型的temp来存放同或门的输出。

module top_module (

input in1,

input in2,

input in3,

output out);

wire temp;

assign temp = in1 ^~ in2;

assign out = temp ^ in3;

endmodule

Problem 48 More logic gates

本题希望我们用两输入的组合电路来实现如下功能,该电路共用于7个输出,具体情况如下:

- out\_and: a and b

- out\_or: a or b

- out\_xor: a xor b

- out\_nand: a nand b

- out\_nor: a nor b

- out\_xnor: a xnor b

- out\_anotb: a and-not b

解析:

(本次练习期望仅使用七行语句)

//Module Declaration

module top_module(

input a, b,

output out_and,

output out_or,

output out_xor,

output out_nand,

output out_nor,

output out_xnor,

output out_anotb

);

assign out_and = a & b;

assign out_or = a | b;

assign out_xor = a ^ b;

assign out_nand = ~(a & b);

assign out_nor = ~(a | b);

assign out_xnor = ~(a ^ b);

assign out_anotb = a & (~b);

endmodule

Problem 49 : 7420 chip

在此之前,我们已经复习了Wire, GND, NOR 和 Another gate,这对我们编写7420 chip的电路已经打下了基础。

牛刀小试

7420 chip是拥有两组4输入的与非门芯片,本练习需要构造一个与7420 chip功能一样的电路,拥有8个输入与2个输出。

解析: 7420 chip的电路很简单,仅有两个4输入的与非门,两条assign语句便可实现。

(本次练习期望仅使用两行语句)

module top_module

(

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y

);

assign p1y = ~(p1a & p1b & p1c & p1d);

assign p2y = ~(p2a & p2b & p2c & p2d);

endmodule

推荐阅读

- HDLBits:在线学习 Verilog (九 · Problem 40 - 44)

- HDLBits:在线学习Verilog(八 · Problem 35-39)

- HDLBits:在线学习Verilog(七 · Problem 30-34)

关注此系列,请关注专栏FPGA的逻辑