终于,可以从openwifi平台上很方便的实时获取信道状态信息了!

不知道openwifi是啥?一句话:openwifi是一个开源的WiFi芯片,目前还没流片,跑在FPGA平台上。长文介绍:纸飞机:开源Wi-Fi芯片/FPGA设计以及背后的中国开发者

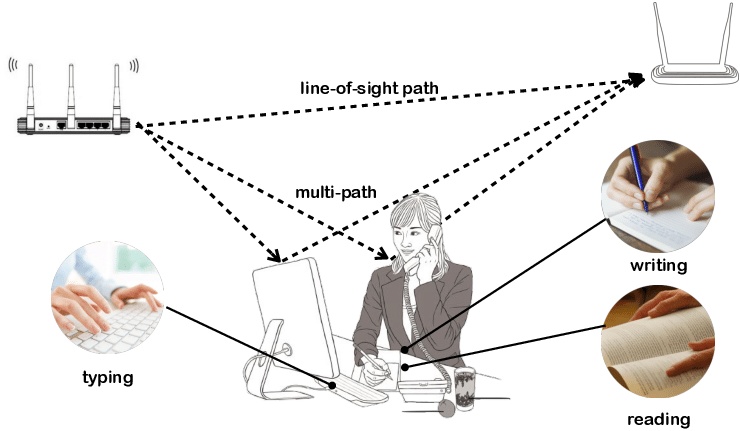

CSI在WiFi研究领域指Channel State Information,也就是通过接收到的WiFi信号来估计WiFi信号的传播信道长什么样子。目前人们可以从CSI里提取到很多信息,比如人的走动,心跳,敲击键盘(如上图),总之吹的很神就是了。

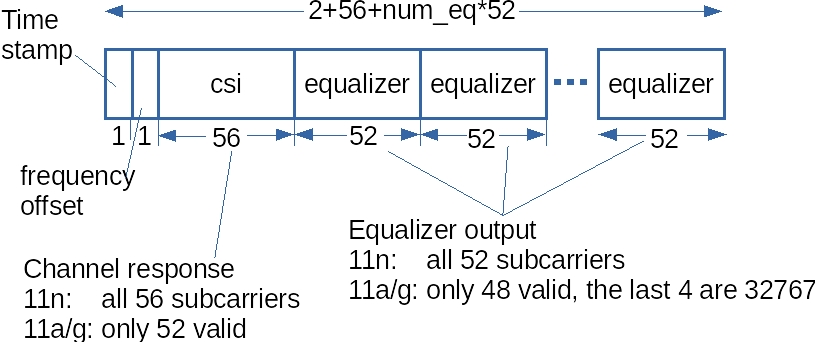

因为这颗WiFi芯片是开源的,所以我们可以获取比传统CSI更多的信息!比如我们现在还支持每个WiFi包的频偏,均衡星座图,时间标签等。所以题目的“从CSI到CSI”指的是从Channel State Information到Chip State Information!

先上真相:https://www.zhihu.com/zvideo/1297662571618148352

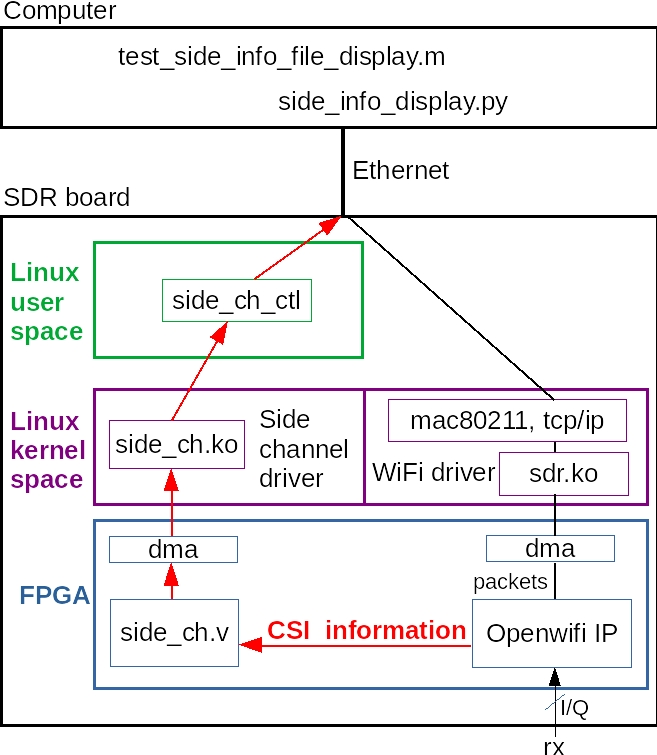

为何能从电脑上实时显示FPGA/芯片内部的信道响应,频偏,星座图信息?因为我们构建了一条从FPGA到Linux的通道(side channel),来把这些信息实时导出。详细参见这个说明文档:https://github.com/open-sdr/openwifi/blob/master/doc/app_notes/csi.md

CSI信息格式如下:

我们的源代码里提供了实时解析CSI信息并显示的python脚本,以及帮助大家离线分析存储下来的CSI的Matlab脚本,都在openwifi github上。

看起来这个功能只是个信息实时导出的功能。但仍然是挺麻烦的:

fpga里需要有逻辑把这些信息按照触发条件(可配置成MAC地址等)捕获下来,然后还需要通过DMA通道传给ARM,在ARM Linux内核中我们构建了相应的驱动来接收这些信息,并传给用户空间的程序,这个用户空间的程序也可以用来配置信息捕获的频率和过滤规则(地址匹配等),最后这个用户空间程序把信息通过FPGA板上的以太网传送给外部电脑(走UDP)。python和matlab脚本分析和显示都在外部电脑上。所以总结一下导出信息涉及到的知识点:

verilog/FPGA编程

FPGA内的wifi协议解析、触发和信息(信道估计,均衡器)捕获

FPGA-linux dma

linux 内核驱动

linux 内核和用户空间通信

python(电脑))和C(FPGA板)之间的TCP/IP通信

python实时绘图

feature虽小,但绝对需要全栈才能实现!