首发:GiantPandaCV

作者:ybai62868

【GiantPandaCV导语】

这篇文章为大家介绍了一下面向低功耗AI芯片上的神经网络设计,随着这几年神经网络和硬件(CPU,GPU,FPGA,ASIC)的迅猛发展,深度学习在包括互联网,自动驾驶,金融,安防等很多行业都得到了广泛的应用。然而当我们真正在实际部署深度学习应用的时候,许多场景例如无人驾驶对设备在功耗,成本,散热性等方面都有额外的限制,导致了无法大规模应用深度学习解决方案。感兴趣的同学可以了解一下有关如何面向AI芯片来设计神经网络。

一、目前算法和硬件co-design的一个大背景

- 从硬件方面来看,我们都知道,深度神经网络中的计算都是大量的稠密型运算。那么,当前的硬件发展其实已经很难满足这些稠密型的运算需求了。那么,设计低功耗,低成本,高性能的硬件计算部署平台就成为了当务之急。

- 对于算法来说,其实在某些公开的数据集上,已经有很多非常不错的算法了,但是这些算法仅仅是针对特定数据集(疯狂刷点...)而在真实的业务场景下,这些算法有时候就并不一定能表现的非常出色。这个时候,我们就要去设计那些不仅是针对一些public数据集能够表现的比较comparable的,同时在一些特定的业务场景下,也要能够表现令人满意的算法。

二、当前AI芯片的发展状况

总的来说,目前的硬件家族可以被分为两个大类。

一大类是以通用需求为主的:CPU, GPU

另一大类以特殊用途为主的:FPGA, ASIC

先有一个大体的宏观概念。然后在看看看算法和这些硬件是怎么结合的。

早期的代码都是跑在CPU上的,比如说,我们知道的LeNet,那会GPU并不像现在这么盛行。直到ImageNet的冠军Alex把网络跑到了GPU上。这个时候,大家都开始使用GPU作为自己的训练平台。其实,CPU并不能非常高效的去运行我们需要的神经网络。因为CPU的运行方式是以串行为主,并且CPU上有很多操作都是为了优化多级缓存,更加偏向的是对于数据IO处理的的能力。而这些方面的设计对于神经网络来说都是多余的。

那么,什么样的硬件结构设计才能更加满足神经网络的特性呢?

其实,这个问题上,超哥讲的很好。究竟什么样的硬件结构更加适合神经网络,还得从神经网络自身的特性来分析。

- 就拿我们熟悉的全连接层来讲,比如说,现在第i层的神经元和第i+1层的神经元之间是以全连接的方式沟通的,那么沟通每个神经元的运算实际上是非常简单的乘法和加法。那么在网络进行一次前向运算的过程中,硬件上能够支持乘法和加法的运算单元越多,那么此时就能够承载下更深的网络。

- 对于同一层上的不同神经元来说,我们需要他们能够相互独立的完成各自的运算,从这点来看,神经网络具有大规模的并行性。

- 不论是在网络进行前向计算还是反向计算的过程中,都会产生很多的中间计算结果。而这些中间结果并不是每个都会被复用,要能放下在网络运算过程中产生的中间结果,就需要我们的硬件有足够的带宽。对于一个理想的设备来说,它应该有比较大的片上存储,并且带宽也要足够。这个时候,对于属于的图片信息(以视觉任务为主)和网络的权重才能有足够的空间来做存储。就是说要它充分的利用片上资源,减少片外的访存。

- 其实,在我们对一个网络进行train和inference的过程中,网络本身对于计算精度并没有我们想象的那么敏感。那么,为了能够存下更多的权重(deep的网络),我们可以使用那些比较简单的数据类型,比如说,int8,fp16。因此,这些年来,大家对于CPU+(GPU, FPGA, TPU, ASIC)这些硬件所组成的异构计算平台。

第一种组合:CPU+GPU

其实,在我们平时做实验,训练模型的过程中,用的最多的就是CPU+GPU这样的组合。

借助现有的非常成熟的深度学习框架(mxnet,pytorch,tensorflow等),我们就能非常方便和容易的完成开发。

优点:编程容易,运算力和吞吐量大。

缺点:GPU的功耗高,延迟大,部署实际的AI产品,没人会用服务器级别的GPU。

第二种组合:CPU+FPGA

这种组合方式的功耗相比CPU+GPU就要低很多。但是,对于FPGA的开发难度则会大很多。

优点:功耗低,方便落地

缺点:编程开发难度大,需要学习专用的硬件语言来支持相应的设备

第三种组合:CPU+ASIC

ASIC指的的是按照产品需求不同而定制化的特殊规格集成电路,由特定使用者要求和特定电子系统的需要而设计,制造。也就是说,ASIC在特定功能上进行了专项强化,可以根据需要进行复杂的设计,从而实现更高的处理速度和更低的功耗。那么,ASIC的生产成本就会更高!

那么其实,可以对上面讲的这些硬件进行一个归类,CPU,GPU叫做通用性芯片。ASIC叫做定制化芯片,而FPGA叫做半定制化芯片。

Google的TPU就是采用了定制化芯片的设计。

其中TPUv1采用了大量的乘法单元,有256x256个8位乘法器。片上有28MB的缓存,能够存储网络的参数和输入。同时,TPU上的数据和指令

说白了,就是将训练好的model拿来定点化做inference。

TPUv2支持了train的功能,并且也能够使用fp进行训练。

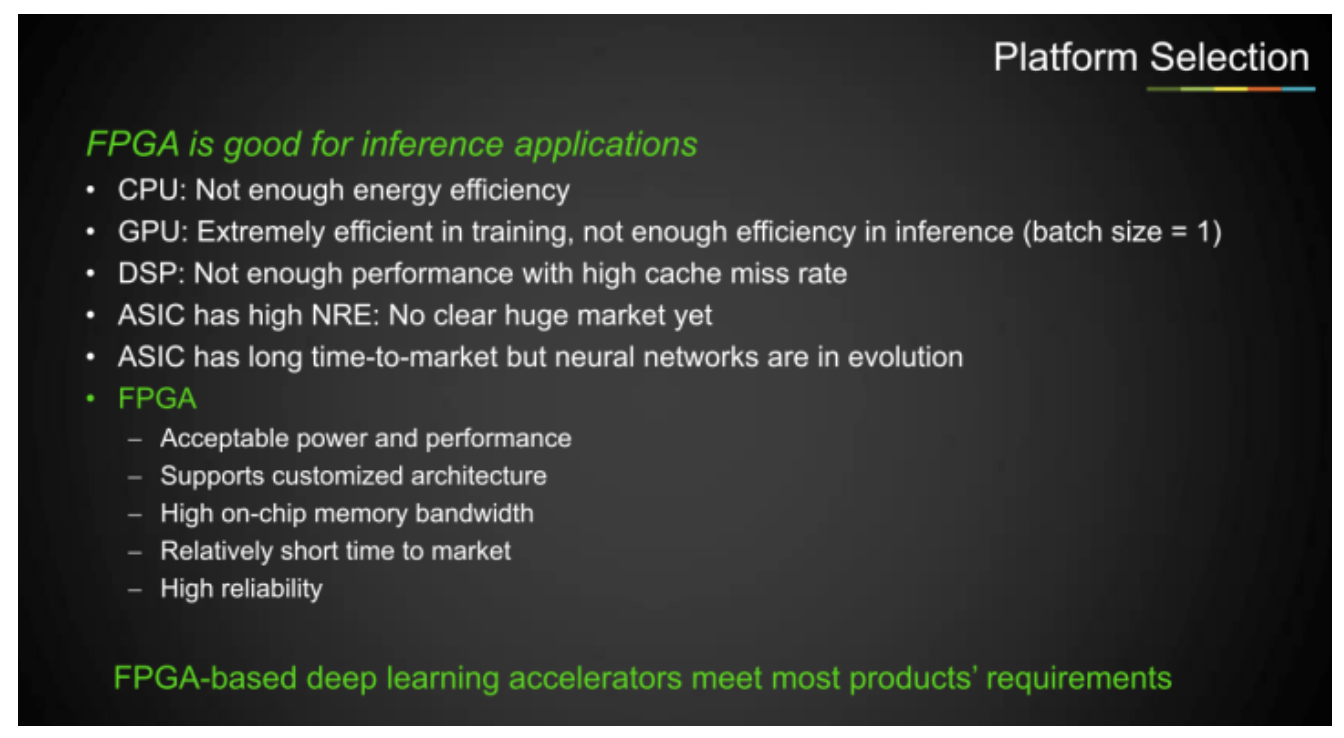

讲了这三种组合,其实如果就拿inference来说,FPGA才是合适的硬件。

各种硬件用于前向推理的优缺点

现在来看,要想设计一款适合深度神经网络的芯片,我们需要其具备什么特性呢?

- 支持主流的视觉任务(inference),不仅仅要支持int8,还要支持fp。

- high performance,low engergy,low cost

- 方便开发和支持主流的DL框架

这里要提的就是地平线自己设计的BPU,它也属于ASIC的范畴。并且支持主流的CV任务。

BPU最大的特点就是设计了弹性的Tensor Core,它能够将那些对于image来说所需要的op硬件化,这些op包括CNN中常见的(卷积,池化等),从而非常高效的去执行这些操作。中间通过一个叫做数据路由桥(Data Routing Bridge)的结构从片上来读取数据,负责数据的传输和调度。同时,整个数据存储资源和计算资源都可以通过编辑器输出的指令来执行调度,从而方便实现各种算法,各种model的结构,和各种不同的任务。

三,如何从算法层面设计高效的神经网络

从AI的解决方案来看存在两种方式:

- 云端 AI

- 前端 AI

云端 AI 说的就是把我们的计算放在远程服务器上去执行,然后把最终的计算结果传回本地,这就要求我们的设备时时刻刻联网,并且存在很大的安全问题和计算传输延迟问题,也就是我们通常所说的通信代价。

前端 AI 说的就是设备本身就能进行运算,不需要联网。那么在安全性,实时性,适用性方面都要胜过云端 AI 。但是,他们在功耗,计算,内存存储等方面有很多受限。

其实关于AI 产品落地,还是回到上面硬件部分讲过的内容,如何去寻求一套 低功耗,高性能,低成本的解决方案。

这里拿IPC和TX2进行比较来说明这个问题。

IPC通过网线来供电,功耗非常低,只有12.5w,TX2的功耗是10-15w。TX2虽然在算力和计算成本方面都要胜过IPC,但是TX2的价位对于嵌入式的方案是不能接受的。。。

那么,要想做好前端AI方案(针对embedd AI)设备来说,我们就要在给定功耗(12.5w)和算力(IPC最大能力)的情况下,去优化我们的算法和神经网络模型,来达到符合场景落地的需要。

那么,说白了,我们最终加速网络的目的就是,在网络保持不错性能的的前提下,尽量去降低计算代价和带宽的需求。

关于网络加速方面看songhan的,补。我在cs231n上学到的东西。

网络量化,网络剪枝,参数共享,蒸馏以及模型结构优化。

在工业界,用的最多的就是网络量化和模型结构化的方法。

下面重点来讲讲这些方法:

3.1 量化

量化其实说的就是离散化。将我们原先连续变化的量通过近似从而达到离散的目的。

神经网络的量化,值得就是将原先用浮点数表示的情况改成用更低的bit,从而继续完成原先浮点数能够完成的训练和测试。

前面再将神经网络特性的时候,我们也提到了网络本身对于计算精度并没有我们想象的那么敏感。所以,比较常用的方法,就是用fp16代替fp32来做train和inference。

其实,使用fp16去训练,有时候还能得到比fp32更好的精度。从ML的角度来看,量化网络本身就是对数据集正则化的一种方式,可以增强模型的泛化能力,从而提高精度。

其实还可以进一步的用int8来取代fp16,这样操作后,带宽只有fp32的四分之一。

当然,如果你不担心精度的损失,那么也可以使用4bit, 2bit, 1bit去代替int8。

神经网络的量化其实可以分为:网络权重的量化和网络特征的量化。

网络权重的量化对于最终的结果输出损失比较小,而特征量化对最终的结果输出损失就比较大。大模型和小模型对量化的敏感程度也不一样,一般小模型会更加敏感。

关于量化想更深入的了解可以看一下下面的这些讲解:

ICCV2019 高通Data-Free Quantization论文解读

3.2 模型剪枝和参数共享

可以参考下面的讲解:

深度学习算法优化系列八 | VGG,ResNet,DenseNe模型剪枝代码实战

3.3 知识蒸馏

蒸馏的思想非常简单,其实就是用一个小模型来取代一个大模型,从而使得小模型能够实现大模型的效果。大模型在这里一般叫做Teacher Net, 小模型叫做Student Net。从小模型到大模型的学习目标,包括最终的输出层,网络中间的特征结果,以及网络的连接方案。

其实,知识蒸馏本质是一种transfer learning,比直接用小数据从头开始训练一个model要得到更好的效果。

3.4 低秩近似

可以参考:https://blog.csdn.net/kathrynlala/article/details/82943291

3.5 二值化/三值化网络

可以参考下面的讲解:

3.6 Winograd 变化

可以参考下面的讲解:

3.7 模型结构化

模型结构化其实是对模型加速最有效的一种方式。

那么关于模型结构优化,又会涉及到很多的知识。

接下来,就要讲讲怎么去设计一个高效的神经网络结构,它需要遵循一些基本原则。

从最初的AlexNet到现在的MobileNetv2,网络的参数从最初的240MB降低到了35MB,

准确率从57%也提高了75%。那么,我们肯定是去设计小的模型结构从而完成相对于大模型难以完成的任务。那么在这个设计的过程中,会涉及哪些基本原则呢?

关于这些,超哥也讲的非常到位,我也总结下:

- 小模型其实并不一定比大模型运行(inference)的快。

- 一个网络计算量小,并不代表他就一定运行的快,因为运行速度还和带宽有关,计算量仅仅是其中的一个因素。

那么,结合上面两点,我们就能明白。一个好的,跑起来比较快的网络结构。必须要衡量计算量和带宽的需求。

推荐认真学习shuffleNet,shuffleNetv2

卷积神经网络学习路线(十九) | 旷世科技 2017 ShuffleNetV1

卷积神经网络学习路线(二十一) | 旷世科技 ECCV 2018 ShuffleNet V2

4. 总结

总结下,如果要设计高效的神经网络结构来部署到硬件平台。那么我们应该尽可能的让网络中的operator去做并行化计算,同时减少这些operator对于带宽的需求。

5. 参考资料

- http://www.rle.mit.edu/eems/wp-content/uploads/2017/11/2017\_pieee\_dnn.pdf

- 干货 | 地平线:面向低功耗 AI 芯片上视觉任务的神经网络设计 | 职播间第 2 期

推荐文章

- 【CUDA学习笔记】第一篇:一个基本的CUDA C程序(附配置方法和安装包下载方式)

- 【最强模型之道】AWS Auto-Aug:通过Weight共享改进自动数据增广,打造最高精度单模型

- 开源|全球最大最干净的人脸公开数据集Glint360K

更多嵌入式AI算法部署等请关注极术嵌入式AI专栏。