转载自:知乎

作者:真垃圾

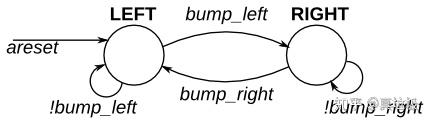

Problem 127 Lemmings1

游戏旅鼠涉及到有非常简单的大脑的生物,我们将会使用有限状态机(FSM)对其建模。

在旅鼠的2D世界中,旅鼠只有两种状态:向左走和向右走。当它遇到一个障碍物的时候,会转变方向。特别是,如果旅鼠被左侧撞到,它将会向右走,被右侧撞到,将会向左走。如果被两侧撞到,它依然会转换方向。

用两状态,两输入,一输出的摩尔型状态机对其行为建模。

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

output walk_left,

output walk_right); //

parameter LEFT=0, RIGHT=1;

reg state, next_state;

always @(*) begin

case(state)

LEFT: next_state = bump_left ? RIGHT:LEFT;

RIGHT:next_state = bump_right? LEFT:RIGHT;

endcase// State transition logic

end

always @(posedge clk, posedge areset) begin

if(areset) state <= LEFT;

else state<=next_state;// State flip-flops with asynchronous reset

end

assign walk_left = (state==LEFT);

assign walk_right= (state==RIGHT);

// Output logic

// assign walk_left = (state == ...);

// assign walk_right = (state == ...);

endmodule

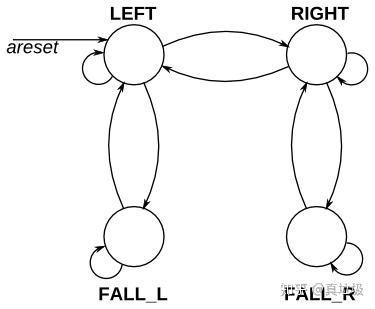

Problem 128 Lemmings2

除了向左和向右,旅鼠在它们脚下地面消失的时候还会掉落(发出“aaah!”)。地面重新出现的时候,旅鼠将会沿着掉落之前的方向继续行走。当旅鼠在地面消失的时候被碰撞(还没有掉落),不会影响步行方向,或者当地面重新出现但旅鼠仍在掉落过程中时,也不会影响步行方向。

用有限状态机(FSM)对此次行为建模。

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

output walk_left,

output walk_right,

output aaah );

reg [1:0]state,next;

parameter WL=0,WR=1,FL=2,FR=3;

always @(*)

begin

case(state)

WL: next = ground? ( bump_left ? WR:WL):FL;

WR: next = ground? ( bump_right? WL:WR):FR;

FL: next = ground? WL : FL;

FR: next = ground? WR : FR;

endcase

end

always @(posedge clk or posedge areset)

if(areset) state <= WL;

else state <= next;

always @(*)

case(state)

WL: {walk_left,walk_right,aaah}=3'b100;

WR: {walk_left,walk_right,aaah}=3'b010;

FL: {walk_left,walk_right,aaah}=3'b001;

FR: {walk_left,walk_right,aaah}=3'b001;

endcase

endmodule

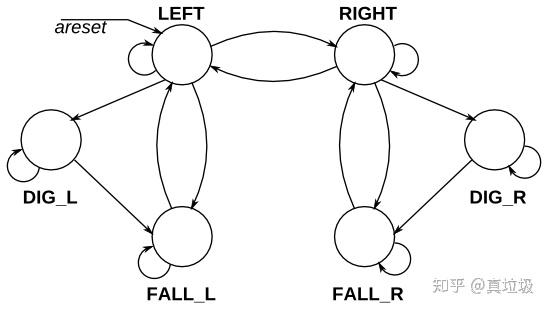

Problem 129 Lemmings3

除了走路和掉落外,旅鼠有时候还能做些有用的事情,比如挖洞(当dig=1时,开始挖洞)

旅鼠在地面的时候(ground=1)它能挖洞,直到到达地面的另一边(ground=0)。在那时,由于没有地面,旅鼠将会下落(发出“aaah”),当它再一次到达地面的时候,继续按照它原来的方向行走。和掉落一样,挖洞过程中被撞击不受影响,而且掉落或者没有地面的时候挖洞命令将会被忽视。

(换句话说,旅鼠能下落、挖洞、或者转变方向。如果多个条件同时满足,优先级是:下落>挖洞>转换方向),扩展你的有限状态机模型来建模其行为。

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

input dig,

output walk_left,

output walk_right,

output aaah,

output digging );

parameter WL=0,WR=1,FL=2,FR=3,DL=4,DR=5;

reg [2:0]state,next;

//state transtition logic

always @(*)

begin

case(state)

WL: next = ground? (dig? DL : (bump_left? WR:WL) ):FL;

WR: next = ground? (dig? DR : (bump_right?WL:WR) ):FR;

FL: next = ground? WL : FL;

FR: next = ground? WR : FR;

DL: next = ground? DL : FL;

DR: next = ground? DR : FR;

endcase

end

always @(posedge clk or posedge areset)

if(areset) state <= WL;

else state <= next;

always @(*)

case(state)

WL: {walk_left,walk_right,aaah,digging} = 4'b1000;

WR: {walk_left,walk_right,aaah,digging} = 4'b0100;

FL: {walk_left,walk_right,aaah,digging} = 4'b0010;

FR: {walk_left,walk_right,aaah,digging} = 4'b0010;

DL: {walk_left,walk_right,aaah,digging} = 4'b0001;

DR: {walk_left,walk_right,aaah,digging} = 4'b0001;

endcase

endmodule

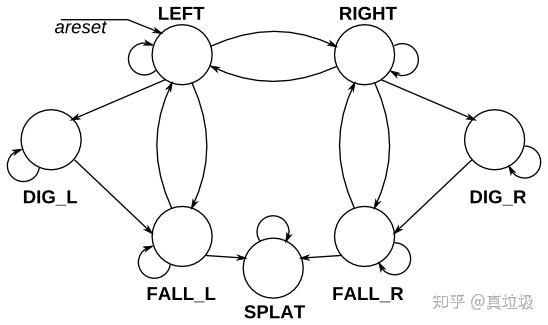

Problem 130 Lemmings4

尽管旅鼠能够行走,掉落,挖洞,但也并非无懈可击。如果旅鼠下落过程过长在落到地面,它会飞溅。特别地,如果旅鼠下落超过20个周期再下落到地面,它将会飞溅,停止行走,掉落和挖掘(所有的4个输出都将为0),除非FSM复位。旅鼠能够下落多远没有上限。旅鼠仅仅会在落到地面的时候飞溅,而不会在半空飞溅。

扩展你的有限状态机模型来建模其行为。

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

input dig,

output walk_left,

output walk_right,

output aaah,

output digging );

parameter WL=0,WR=1,FL=2,FR=3,DL=4,DR=5,Splat = 6;

reg [64:0]counter;

reg [2:0]state,next;

always @(*)

case(state)

WL: next = ground ? (dig ? DL: (bump_left?WR:WL)) : FL;

WR: next = ground ? (dig ? DR: (bump_right?WL:WR)) : FR;

FL: next = ground ? (counter>19? Splat : WL) : FL;

FR: next = ground ? (counter>19? Splat : WR): FR;

DL: next = ground ? DL : FL;

DR: next = ground ? DR : FR;

Splat:next = Splat;

endcase

always @(posedge clk or posedge areset)

begin

if(areset) state<=WL;

else if ( state==FL || state == FR )

begin

state <= next;

counter = counter + 1;

end

else begin

state <= next;

counter =0;

end

end

always @(*)

case(state)

WL : {walk_left,walk_right,aaah,digging} = 4'b1000;

WR : {walk_left,walk_right,aaah,digging} = 4'b0100;

FL : {walk_left,walk_right,aaah,digging} = 4'b0010;

FR : {walk_left,walk_right,aaah,digging} = 4'b0010;

DL : {walk_left,walk_right,aaah,digging} = 4'b0001;

DR : {walk_left,walk_right,aaah,digging} = 4'b0001;

Splat: {walk_left,walk_right,aaah,digging} = 4'b0000;

endcase

endmodule

推荐阅读

- HDLBits:在线学习 Verilog (二十四 · Problem 115-119)

- HDLBits:在线学习 Verilog (二十三 · Problem 110-114)

- HDLBits:在线学习 Verilog (二十二 · Problem 105 - 109)

- HDLBits:在线学习 Verilog (二十一 · Problem 100 - 104)

- HDLBits:在线学习 Verilog (二十 · Problem 95 - 99)

关注此系列,请关注专栏FPGA的逻辑