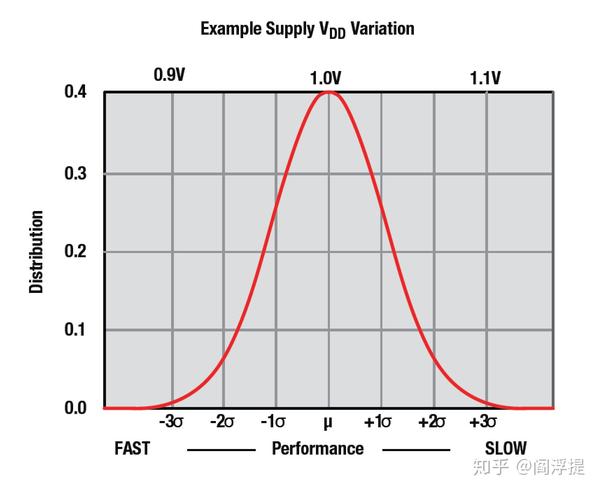

我们知道所有芯片在设计之初都需要规划好芯片的参数和应用场景,统称为芯片的spec。在spec中通常会定义一个或几个典型的应用场景以及它对应的工作条件如电压、频率和功耗上限等。因此绝大多数芯片的工作条件尤其是电压和频率在一开始就是比较固定的。然而在实际流片后,往往会出现不同芯片的最高频率不同的情况,最主要的原因相信很多人能猜到:process variation。一般来说这种variation会导致不同芯片达到相同性能所需要的电压也呈现正态分布,如下图所示:

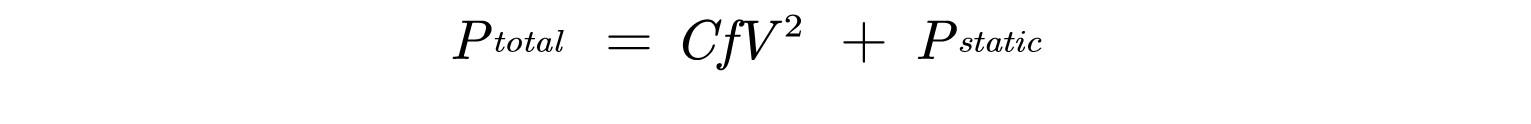

这就导致有的芯片比目标频率低,可称为Weak Device;有的刚好达到目标频率,可称为Nominal Device;还有的可以达到比既定目标更高的频率,称为Strong Device。由于芯片功耗由以下公式可以算出:

其中C晶体管的电容值,f是信号的频率,V为工作电压,Pstatic则是静态功耗的总和。那么我们就可以看出来因为电压的平方与整体功耗成正比,因此降低工作电压对总体功耗的效果应该最为显著。当芯片的最高频率超出既定指标,那么想通过降低电压来保证性能不变的前提下获得更小的功耗就成了自然而然的想法。

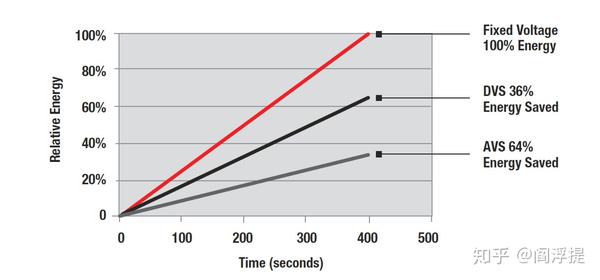

既然要调整电压,就需要引入两个概念:DVS(Dynamic Voltage Scaling)和AVS(Adaptive Voltage Scaling)。它们的核心目的都是通过调节芯片整体或者部分power domain的电源电压来实现降低功耗的目的。所不同的是,DVS会选取一个或者几个电压-频率的对应点来固定调节电压,AVS可以更精确地在一定范围内自由调节电压数值。在降低功耗的效果上,根据德州仪器的公开实验数据,AVS最高可以减少60%以上的功耗:

讲到这里大家应该能明白DVFS代表什么了。DVFS的全称是Dynamic Voltage Frequency Scaling,是IC设计中降低动态功耗的比较常见的概念。它可以根据芯片的性能和功耗需求调整电压和频率,从而在各个不同的工作需求中都已最小的功耗实现需求。

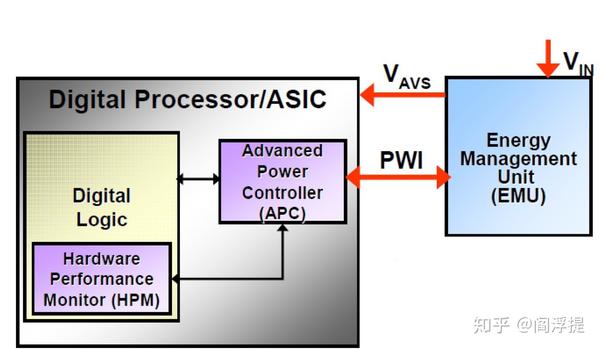

在实现DVFS的过程中,需要一个输出电压控制器,一般来说叫做EMU(Energy Management Unit)。它在芯片中的基本逻辑结构如下:

在实际芯片工作过程中,EMU会根据不同的功耗需求输出不同的电压供给部分或者全部芯片的逻辑部分,从而在满足频率的前提下有效降低整体功耗。

另外,在芯片设计过程中,为了在不同电压和频率条件下满足时序需求,需要在多个coner和多个mode下做时序收敛,也就是通常所说的multi-mode multi-corner。这里的mode不仅仅是功能上区分的function,test等mode,还需要同一功能模式下不同电压的时序,因此采用这种设计的芯片会带来额外的timing signoff复杂度和工作量。

需要说明的是,DVFS调整电压和频率仍然是采用固定的几个数值来调节,而对应的还有AVFS(Adaptive Voltage Frequency Scaling)尽管可以更精细地调节,但是在实际中应用却不多,原因在于AVFS会极大地增加timing signoff的难度,一方面很难用少数PVT条件去覆盖所有电压和频率的组合,另一方面想要增加PVT条件可能面临signoff corner过多或者时序库不全需要自己K库的问题。

总结来说,在实际应用中相较AVFS的方法,DVFS的应用更多。主要原因在于它可以在降低功耗和设计难度方面有一个较好的平衡。

以上就是本篇的全部内容,如果你觉得学到了新知识,请点个赞再走~

粉丝福利:

近期小编开发了一台用于芯片设计的云服务器,和主流IC企业的服务器环境类似,里面包含所有主流前后端EDA工具、几种开源45nm/32nm/14nm的工艺库和多个实验项目,非常适合初学者学习。每个人可以有一个独立账号可以随时随地用VNC远程访问服务器,里面的所有资源包括我开发的一些脚本和小工具都免费使用,只需分担一下云服务器的购置费用和服务器开发维护费用。小编会带着有需要的同学从头做一个小项目来帮助大家深入理解后端的工作和工具使用,而且不会是跑流程就能完成的,需要大家从原生命令开始一点点把设计做起来。目前首批开放的10个独立账号已经所剩不多,有兴趣的同学可以私信小编咨询,剩余账号先到先得!

推荐阅读

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。