时序上很难满足的那些时序路径称为时序关键路径(timing critical paths),可以分为建立(setup)和保持(hold)时序关键路径。

STA工具分别在max和 min条件下,分析setup/hold的违例,即设计中同时发生setup/hold违例可能发生在同一个工作条件下,也可能发生在不同的工作条件下。

下面分别举例说明这两种情况:

Case1(在同一个工作条件下,同时发生setup/hold的violation):

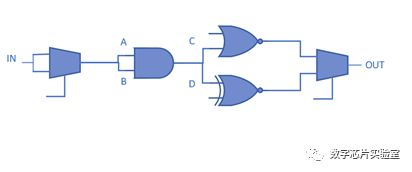

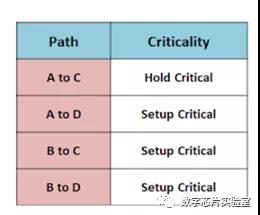

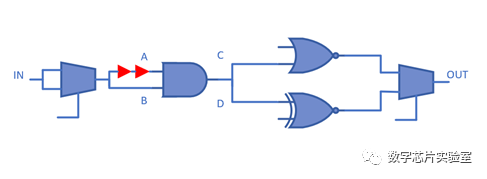

在上面的一条path中,(PS:上面的所有逻辑门换成其他组合逻辑black box)

IN -> A -> C -> OUT 为hold critical如果我们要修复IN -> A -> C -> OUT这条路径的hold time violation,我们可以:

1、在C上插入buffer,但是这会增加B -> C的延时,加剧B ->C的setup violation

2、在A 上插入buffer,但是这会增加A -> D的延时,加剧A -> D的setup violation

上述就是我们所阐述的同一个工作条件下,同一条路径,同时发生setup/hold violation的情况。

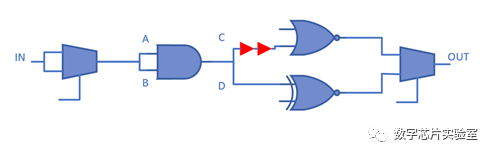

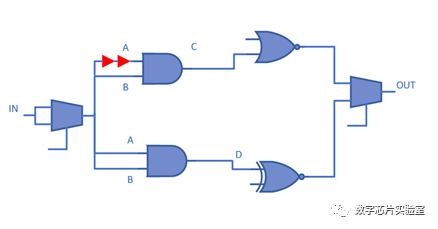

怎么修复IN -> A -> C -> OUT这条路径的hold time violation呢,我们可以:

再复制一个与门,在修复IN -> A -> C -> OUT路径上的hold violation的同时,而没有增加A -> D和B-C的延时。

Case2(在不同工作条件下,同时发生setup/hold的violation):

标准单元(standard cell)的延迟随PVT和OCV的变化而变化,cell delay从worst case scenario到best case scenario可能相差2倍。假设,setup/hold time要求也按相同比例缩放。

设计在所有的工作条件下都需要同时满足setup/hold time要求。这意味着需要在worst case scenario下满足setup time,并在best case scenario下满足hold time。

对于下面的示例(F=1.4 GHz,T= 714 ps ):

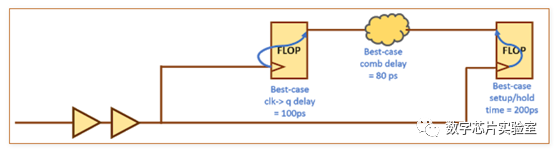

best case scenario如下图所示:

launch flop的clk-> q delay为100 ps,combinational delay为80 ps,hold time为200 ps。在这种情况下:

Hold slack = Tck->q +Tprop - Thold因此,在这种情况下,我们的hold slack是负的。因此,我们需要在保证setup slack为正的情况下,修复hold time violation。

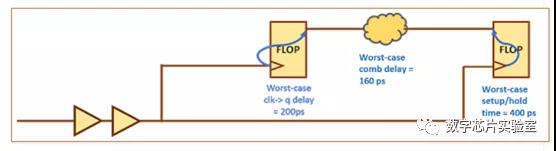

worst case scenario如下图所示:

如果我们假设worst case scenario延时相对于best case scenario延时都按比例缩放2倍,则clk-> q delay为200 ps,combinational delay为160 ps,setup time为400 ps。

Setup slack = Tperiod - (Tck->q +Tprop + Tsetup)因此,对于相同的时序路径,setup和hold slack都变为负值。解决方案可以是:

1、利用使用延迟变化较小的cell(或者线延时)。

2、将工作条件(PVT)限制在更窄的范围内。

3、降低频率,同时增加data path延时。

...

对于第3个解决方案,首先,我们需要确保满足hold time 要求(Hold slack >= 0)。将combinational delay为增加到 100ps。换句话说,worst case scenario下的combinational delay为200 ps(缩放2倍)。

如果setup的余量为0 ps,则最大工作频率为:

Tperiod(min) = Tck->q + Tprop +Tsetup本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/rCDXZVuBfA1nykQGzP_AFg

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,每日学习,渐进成长。