和某大公司一位后端资深人士交流发现,其对于PVT中局部偏差,全局偏差概念似乎有些问题。正好本文进一步解释为什么说PVT corner仅处理全局偏差,而OCV(包括flat OCV,AOCV, SOCV)处理的是局部偏差。欢迎探讨。

OCV中工艺偏差的考虑

ocv中对工艺偏差的考虑,分为两种情况。即为,时序库同时包含全局工艺偏差,局部工艺偏差的情况,以及时序库中仅包含全局工艺偏差的情况。

1. 时序库中包含有全局工艺偏差,局部工艺偏差的情况

前文结尾最后一句话在此进行更正。在采用包含有local variation的SS FF corner进行signoff时,仍然需要增加额外的ocv。下面进行解释。

在SS,FF corner中,虽然同时包含了全局工艺偏差,局部工艺偏差。但是,在进行静态时序分析(STA)时,仍然不能够覆盖最差情况。

我们假设process corner为ff。可以认为,晶体管的速度在ff corner下是最快的。也就是说,所有的cell都处于最快的状态。

而假设,我们现在检查的是hold timing。

对于data path,可以认为,cell全部处于最快速度,已经覆盖了所有最坏情况。

而对于clock。launch clock以及capture clock也都是用的最快的device。

这里的问题就在于,对于hold timing来说 capture采用最快情况来计算,带来的是乐观的结果。理论上,时序的计算并未覆盖最差情况。

反之,对于ss来检查setup,存在同样的问题。

因此,即使是用ss ff corner,也需要加上ocv,以便把这部分乐观成分去掉。

一般来说,hold check需要加一部分正的derate在capture path。setup check需要加一部分负的derate在capture path。

2. 时序库中仅包含全局工艺偏差的情况

目前较为先进的工艺中,更多的采用的是ssg, ffg。

原因在于,随着摩尔定律的延续,工艺尺寸的缩小,局部工艺偏差变得越来越严重。

举个例子,对于栅氧层来说,厚度可能仅为几个原子直径大小。仅仅一个原子的缺失,对于这个device来讲,性能都可能受到较大的影响。

那么,如果采用传统的,将局部偏差,全局偏差都考虑进时序库中,会产生什么样的情况呢?

我们仍然以在hold时序为例,为便于理解,仅考虑路径上的data path。

如果采用ff的库,则等效为,data path上所有的cell的local variation都向相同的方向进行的偏移。

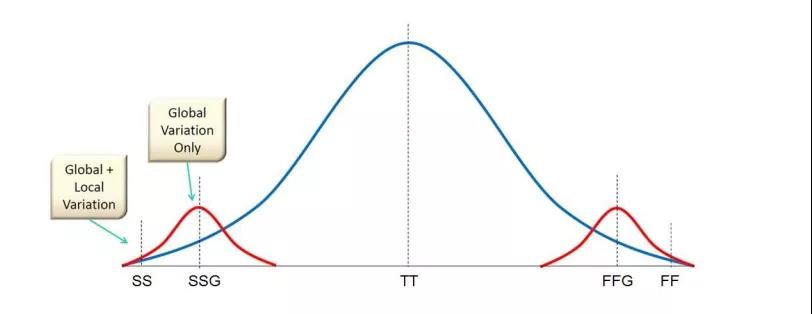

全局工艺偏差,局部工艺偏差关系图

实际情况是,local variaton成正态分布,而路径上所有device都从FFG偏移至FF的概率很低,一般以FFG为中点,取值3signal作为FF。而路径上所有device都达到FF的情况,概率可以理解为0.

那么如何去除这部分悲观情况?

就是将局部工艺偏差分离出来。采用AOCV,POCV等先进的OCV计算方法,来进一步去除局部工艺偏差造成的影响。而如果继续采用传统的ss ff,local variation的影响可能导致timing无法满足。

OCV中电压的考虑

电压需要分为电压全局偏差,电压局部偏差来理解。

同样以ffg 0.88v来check hold为例。我们可以将0.88v作为全局电压。在这个电压下,device的速度最快。但是,由于对于clock的lauch, capture都采用的最快的device,并不能覆盖所有的最差情况。

因此,在ocv中增加一部margin来覆盖这一部分情况也就可以理解了。

OCV中温度的考虑

温度同样可以划分为全局温度偏差,局部温度偏差。全局温度偏差,将在PVT中得以体现。由于温度反转的影响,仅采用极限温度-40c,125c有时候并不能覆盖全局温度偏差中的最差情况。有时需要增加额外的温度的corner。

而由于芯片内部不同位置之间,由于device翻转速率,电压降等不同,导致局部相同的时序路径中,温度也有偏差。采用相同的温度仍然不能覆盖所有最差情况。

在进行signoff时,需要增加ocv余量,覆盖温度局部偏差。

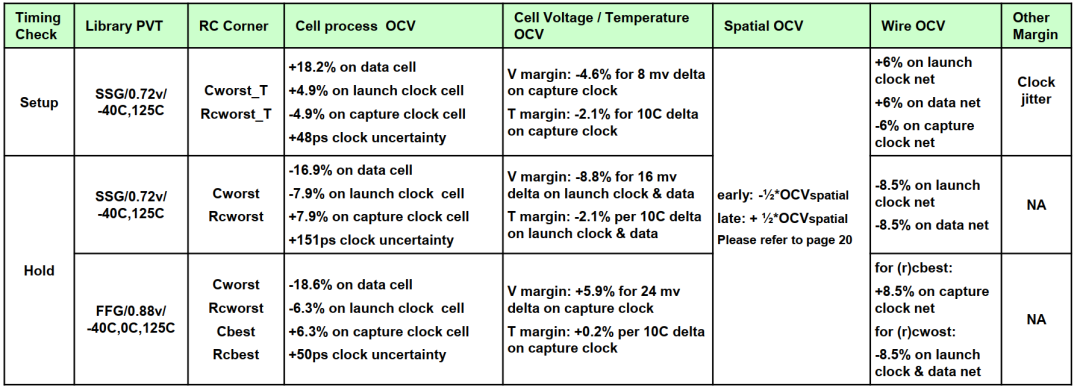

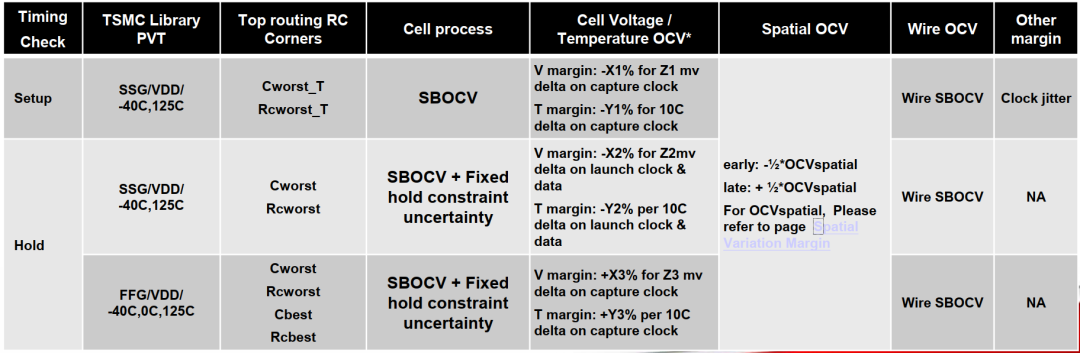

示例

TSMC 28nm 时序签收标准

OCV

AOCV

作者:白山头

来源:https://mp.weixin.qq.com/s/cw...

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。