动态电压降往往是在进行物理设计后期来进行的一项检查。

因为需要前端工程师提供准确的vcd或者saif文件来进行switching activity的反标。

这时候修改电源网络可能并不适合。

这里盘点修复动态电压降的一些方法:

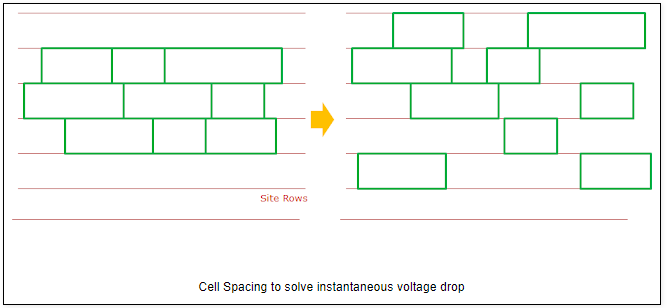

cell pading

尤其对于clock cell,由于翻转率高,应当避免多个clock cell集中于一处,加cell pading是个不错的方法。

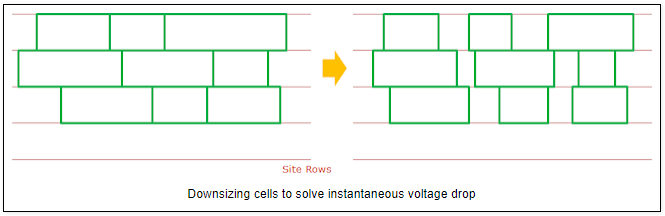

downsize

downsize不仅可以降低cell的功耗。留出来的空位也可加以利用。比如,加上decap cell。

split output capacitance

有动态功耗的公式可以知道,减少load可以减少cell本身的动态功耗。通过buffer将长net切断,将有助于降低局部的动态电压降。

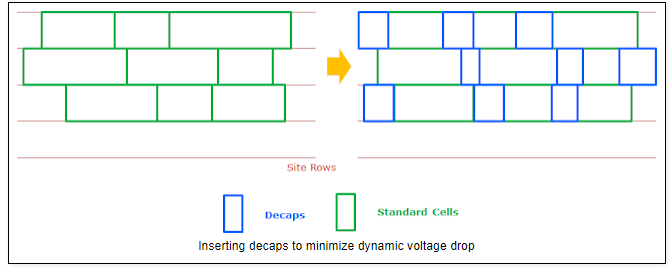

inserting decap cell

decap cell对于动态功耗意义非凡,尤其是decap对于与其附近,且相同row之内的cell的作用,会非常有效。

end

工艺尺寸的缩小,我们的芯片正从gate-dominated变为wire-dominated,同时频率也在不断的提升。

wire-dominated,意味着没有更多的绕线资源用用作电源网络。

频率的提升,意味着动态电压降会变得更加严重。

所有这些,需要我们采用以上提到的方法进行动态电压降的优化,而且这些方法会越来越重要。

作者:白山头

来源:https://mp.weixin.qq.com/s/ZF...

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。