Corner可以分为对晶体管的偏差建模的PVT corner,以及对互联线偏差建模的RC Corner。PVT Corner用于描述晶体管的全局工艺偏差。RC Corner 用于描述互联线工艺偏差。

PVT corner

PVT corner需要覆盖全局工艺偏差,温度偏差以及电压偏差。

process corner

Lot 与 Lot 之间, Wafer Wafer之间, Die 和 Die之间的工艺的偏差都是全局工艺偏差。全局工艺偏差的差别远大于局部工艺偏差的影响(local process variation)。由于全局工艺偏差的存在,导致CMOS的速度有的快,有的慢。从而导致芯片有快有慢。

Process corner被用于对全局工艺偏差进行建模。

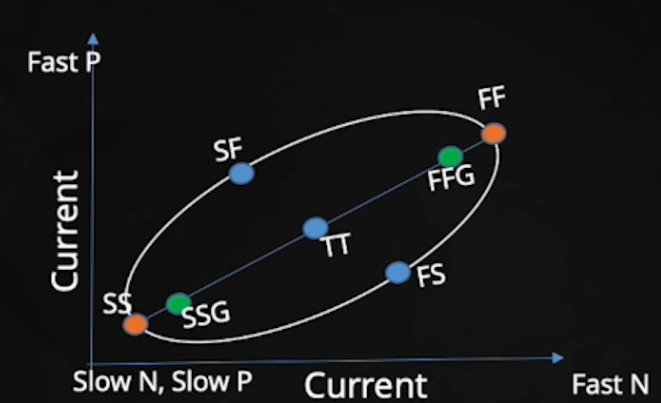

由于全局工艺偏差对CMOS中NMOS, PMOS的影响有所不同,因此按照晶体管的速度,可以分为以下五种process corner:

- TT:Nominal

- SS:Slow N Slow P

- FF:Fast N Fast P

- SF:Slow N Fast P

- FS:Fast N Slow P

其中常用于进行时序签收的corner为SS FF。

比较先进工艺中,foundary会提供排除local process variation的spice model,即SSG FFG等。

SS FF Corner包含了local process variation

voltage corner

晶体管的速度随着电压的升高而提高。因此,时序签收时需要考虑极限电压的情况,以保证芯片在整个电压范围能够正常工作。

temprature corner

温度会影响晶体管的速度。时序签收时,需要能够保证芯片在设计的整个温度范围能够正常工作。由于结温与环境温度的差异,需保留足够的设计余量。

RC Corner

工艺与温度会对芯片内部的互联线以及via的电阻,电容造成影响。RC Corner用于对互联线的偏差进行建模。

常用的RC Corner:Typical Cbest Cworst RCbest RCworst

由于温度对于互联线以及通孔的RC有影响,因此RC Corner也需要考虑到温度的影响。

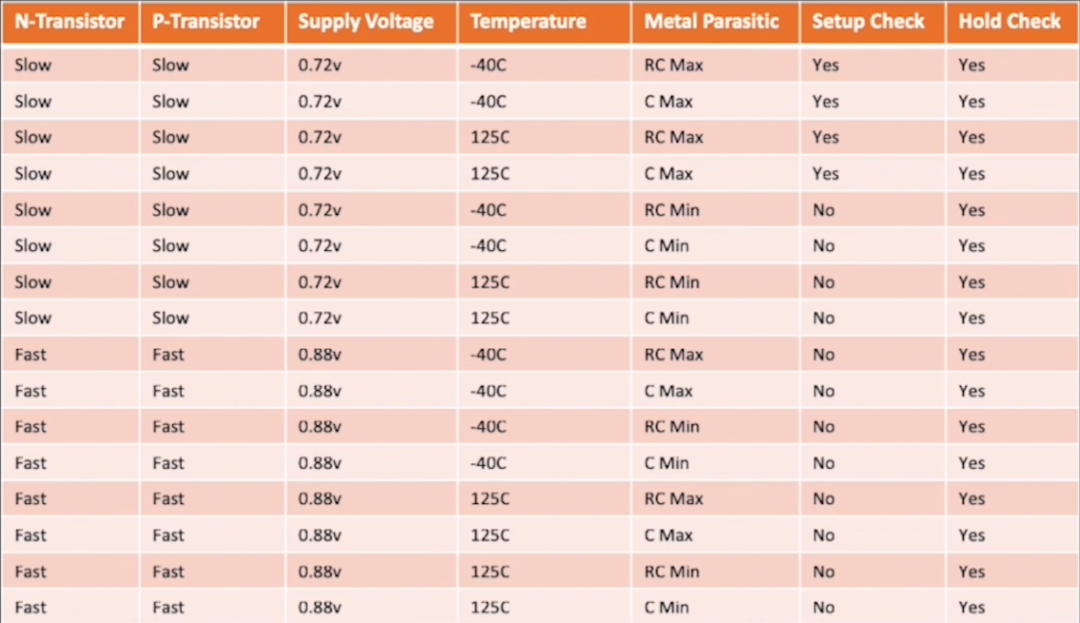

时序签收所用的Corner示例

电压范围:0.72 ~ 0.88 温度范围:-40C ~ 125C

22nm 时序签收Corner示例

其他

注:若使用的包含有局部工艺偏差的时序库,则在ocv设置中无需再考虑局部工艺偏差。设计余量的大小需根据实际工作的温度,电压的变化谨慎评估。

作者:白山头

来源:https://mp.weixin.qq.com/s/85...

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。