转载自:知乎

作者:ljgibbs

上期我们基于 JESD-79 学习 DDR 的刷新及其刷新命令。本期我们将讨论 DRAM 的自刷新特性(Self-refresh)。

基于 JESD79-48 / 4.27 节

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICSIG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

DDR 学习时间 - OpenIC SIG 开源数字IC技术分享

DRAM 自刷新

上期我们说到 DDR 控制器会定时向 DRAM 发出刷新命令(REF),DRAM 根据指令对存储数据的电容进行充电操作,防止表示数据 1 的电荷因为漏电流的原因随时间流失。

而所谓”自“刷新,即无需控制器发出刷新命令,DRAM 也会基于内部的定时器进行定时刷新。那么在哪些场景下会使用到自刷新特性呢?

笔者理解有两种典型的情况

- 系统异常掉电。

因为现代系统中 DRAM 采用一路独立电源供电(V\_DDR),区别于系统剩余部分的电源(V\_CORE)。所以,当系统的其余部分因为故障或者受到外部条件影响掉电(Power down)或者奔溃时, DRAM 仍能够保存数据。

但是由于控制器已经掉电, DRAM 无法继续收到刷新指令,如果系统不能马上恢复,数据仍然将会丢失。因此,系统在检测到掉电时,比如在 power down 中断中,可以使 DRAM 进入自刷新状态以保护数据。更近一步,系统还可以将掉电时的状态信息存入 DRAM,用于调试系统掉电故障。

当然如果是整个系统的外部电源掉电了,那就没什么好说的了,肯定全玩完了。

- 系统进入低功耗模式。

当系统进入深度睡眠状态以节约电能消耗时,不会产生 DRAM 读写请求。此时使用控制器来维持 DRAM 状态已经没有必要。因此可以关闭控制器,并停止 DRAM 的外部时钟,使用自刷新状态来维持 DRAM 中的数据,以节约电能。

低功耗自刷新模式

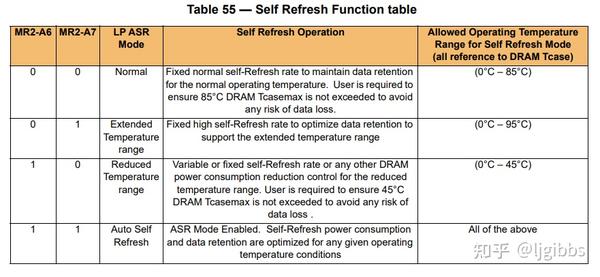

DDR4 支持多种低功耗自刷新模式,以适应不同的工作温度。这里主要考虑到高温对于漏电流的促进作用,在高温下需要提高刷新的密度,以防止潜在的数据丢失。

那么在工作温度不高的低功耗场景中,则可以适当减少刷新的密度,多少也能省点电。蚊子腿也是肉啊。

如果温度范围发生了变化,可以通过先退出当前的自刷新状态,切换自刷新模式,重新进入自刷新状态这样一个流程切换模式。

DDR4 定义了一种自动刷新模式 (ASR) 减少上层应用的麻烦。在 ASR 中 DRAM 会自动根据工作温度调整刷新密度,这应该需要 DRAM 内置温度传感器来实现。

自刷新命令

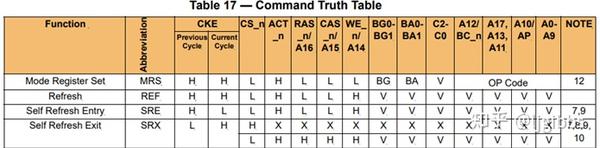

进入/退出自刷新状态分别使用 SRE/SRX 命令。

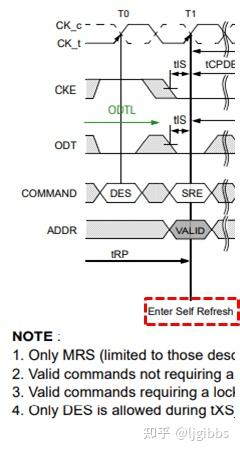

SRE 命令

SRE 命令要求控制器置低 CKE、CS\_n、RAS\_n、CAS\_n,置高 ACT\_n、WE\_n。

Before SRE

在进入自刷新,DRAM 必须处于 IDLE 状态

- 所有 BANK 已经完完全全关闭

- 所有先前的命令已经完全结束

- 没有传输中的数据

- CKE 信号为高

After SRE

CKE 信号保持为高,使 DRAM 处于自刷新状态。所以我们一般可以通过 CKE 的电平判断 DRAM 是否处于自刷新状态。

DRAM 在自刷新期间, 只在乎 CKE 信号(什么时候退出自刷新)和 RESET\_n 信号 (什么时候复位),其他信号一概不在乎,包括外部输入的时钟信号。

SRX 命令

SRX 命令使 DRAM 退出自刷新状态,SRX 有两种实现方式:

- CKE 置低一个周期后置高,置高 CS\_n。

- CKE 置低一个周期后置高,置低 CS\_n,置高 ACT\_n、WE\_n、RAS\_n、CAS\_n。

其中前者只能在 Max Power Saving 模式中使用。

Before/After SRX

和进入时一样,退出自刷新状态时我们必须满足一定条件:

在发送 SRX 命令前,

- 恢复稳定的外部时钟输入,如果自刷新期间时钟关闭的话。

在发送 SRX 后,

- CKE 信号需要保持为高,直至完全退出自刷新状态。

- SRX 命令之后的第一条命令,需按照该命令是否使用 DLL 满足一定时序。

- 在 SRX 命令与下一次 SRE 命令之间必须有至少一条 REF 命令。

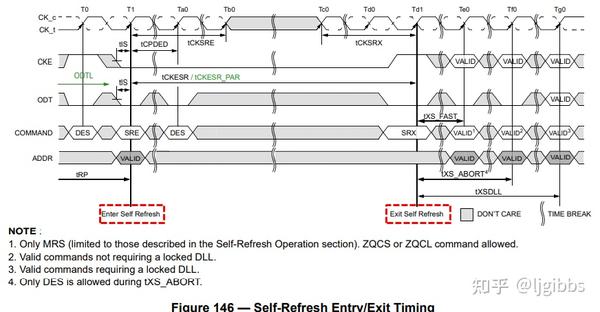

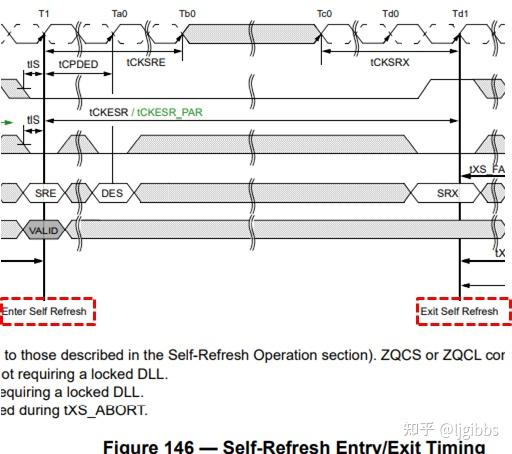

DRAM 自刷新相关时序

上图是 Specification 中关于自刷新的时序图,一上来就看这张图可能信息量比较大。我们可以分成几个阶段来看。

阶段一 SRE 之前

tRP

这里假设 SRE 之前是一个 PRE 命令,SRE 命令必须与之间隔 tRP 以上,以确保进入自刷新状态时,所有的 Bank 都已经真正被关闭了。

阶段二 Self Refresh 期间

tCPDED

与自刷新无关

tCKESR

一次自刷新至少要持续的时间。在 DDR4 中一般为 5ns+ 1 个时钟周期。(JESD79-48 P231)

tCKSRE/tCKSRX

在进入自刷新后,外部时钟可以停止输入以减少功耗。但是,自刷新期间停止的外部时钟输入,必须在退出自刷新前 tCKSRX 时间重新启动并稳定。

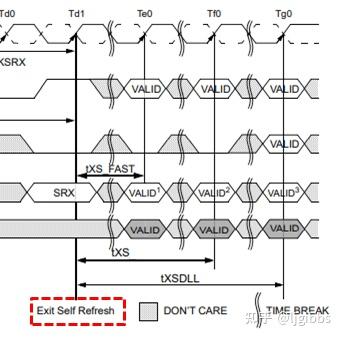

阶段 SRX 之后

tXS

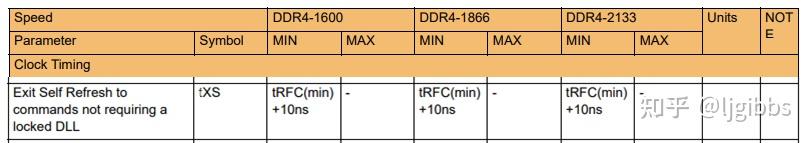

tXS 是 SRX 命令距离第一个有效命令的间隔时间,按照有效命令是否需要 DLL 可分为两种类型。(下图为了便于理解有略微修改)tXS 的数值为 tRFC + 10ns。

tXS\_fast 和 tXS 代表那些无需 DLL 的命令距离 SRX 命令的间隔,具体 tXS/tXS\_fast 分别对应的命令可以查看 JESD70-4B 的 4.27。

tXSDLL 代表需要 DLL 的命令与 SRX 命令的间隔,基本上也就是各类读命令。

结语

本期我们讨论了 DRAM 的自刷新特性,以及一些相关的时序与细节。总的来说有三点需要了解:

- 自刷新状态用于在系统异常掉电或者低功耗状态下,保持 DRAM 中的数据。 * 自刷新状态需要根据工作温度选择不同模式,发出足够密度的自刷新命令,以维持数据。

- tXS 是自刷新相关的重要时序参数,代表有效命令与 SRX 命令的间距。 PS:这里总结下系列文章“扣标准细节”的程度。首先,本系列不会是标准文档的翻译,会涉及一些细节。细节的程度大概是 SoC 之下,IP 之上:

- SoC 集成与验证工程师无需关注所有的细节,比如不常用的时序参数等等。 但本系列文章仍过滤了一些细节,可以节省你们翻阅标准的时间。

- DDR IP/model 设计与验证工程师会觉得这些细节不足够,毕竟你们的工作还是以标准手册为准。但本系列文章中收录的部分细节可以提示你这些内容在标准中的位置。

- *

关于《DDR 学习时间》专栏

在 DDR 学习时间专栏中,目前有两个 Part:

- Part-A DRAM 课程、论文以及其他在线资源的学习

- Part-B 基于 DDR4 Spec 的 DDR 特性学习

推荐阅读

- DDR 学习时间 (Part B - 1):DRAM 刷新

- 开源仿真器 EpicSim 运行 SM3_core

- DDR 学习时间 (Part A - 1):一篇 2002 年的 DDR 控制器设计硕士论文

- HDLBits:在线学习 Verilog (三十二 · Problem 155-159)

- HDLBits:在线学习 Verilog (三十一 · Problem 150-154)

关注此系列,请关注专栏FPGA的逻辑