set\_data\_check 是个啥?

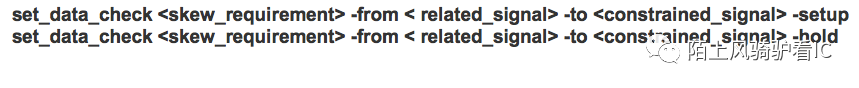

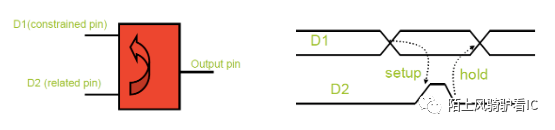

set\_data\_check 是一条SDC 的命令,用于约束『数据-对-数据』的『建立保持』时间检查,通常被称为非时序约束 ( non-sequential constraints ), 理论上set\_data\_check 可以设在任意的两个data pin 上,其中一个pin 称为 constrained pin 类似于寄存器的data pin, 另一个pin 称为related pin 类似于寄存器的clock pin.

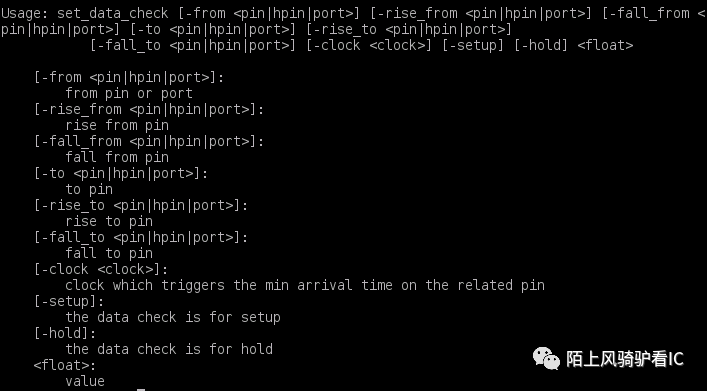

用set\_data\_check 约束时,-from 指定的pin 为related pin, -to 指定的pin 为constrained pin.

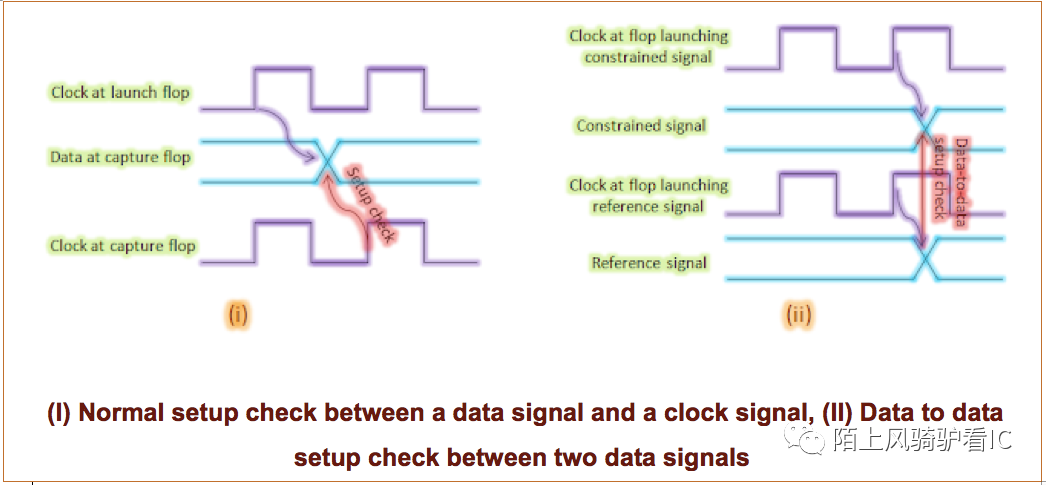

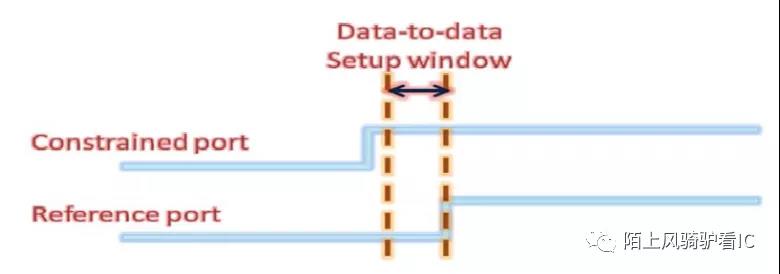

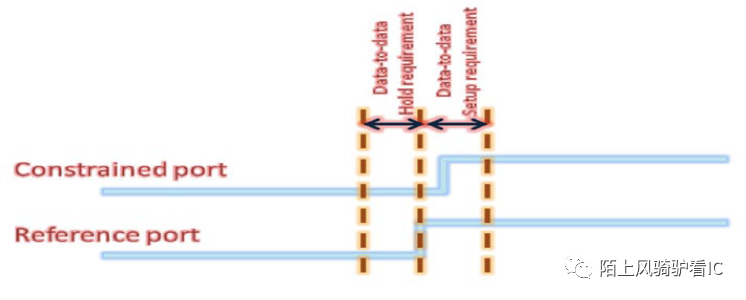

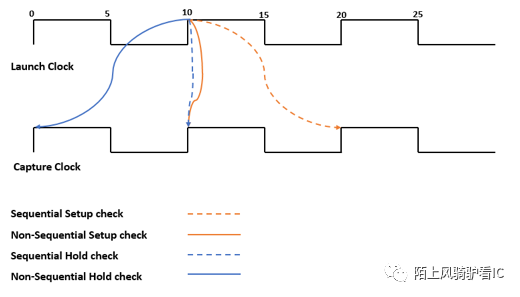

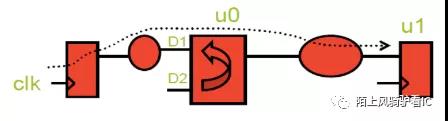

用set\_data\_check 约束的『建立保持』时间检查跟普通寄存器的『建立保持』时间检查最大的区别是:set\_data\_check 约束的『建立保持』时间是zero-cycle check, 即constrained signal 跟related signal 两个数据信号在同一个时钟沿被采样释放,如下图右侧所示;而传统的DFF setup check 默认是跨一个时钟周期的。

set\_data\_check 也分setup 跟hold:

- set\_data\_check setup: 类似于寄存器的setup, 即related signal 翻转前,constrained signal 必须保持稳定的时间。

- set\_data\_check hold: 类似于寄存器的hold, 即related signal 翻转后,constrained signal 必须保持稳定的时间。

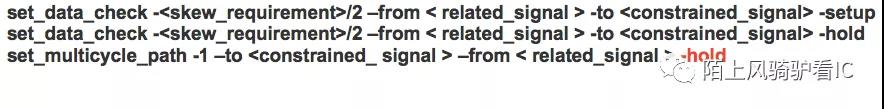

set\_data\_check hold check 时,capture clock 同样会往前推一个cycle, 所以如果设了hold data check通常需要设一个multi\_cycle 将其拉回来。

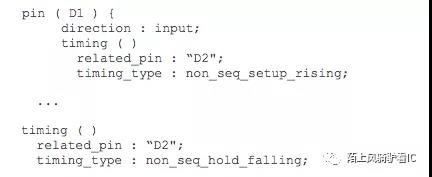

除了用set\_data\_check 约束『数据-对-数据』的检查之外,有的lib 里也会定义『数据-对-数据』的检查,lib 中的关键词是:

- non\_seq\_setup\_rising

- non\_seq\_setup\_falling

- non\_seq\_hold\_rising

- non\_seq\_hold\_falling

用set\_data\_check 约束的『数据-对-数据』检查跟lib 里定义的『数据-对-数据』有以下区别:

- set\_data\_check 只能指定一个值,而 lib 里定义的non\_seq timing check 则是一张index 为input transition 跟output load 的表格,所以更精确。

- 但是lib 里定义的non\_seq timing check 只能在该lib cell 的leaf pin 上,而set\_data\_check 可以对design 中任意两个pin 进行约束。

- 对于C 家工具,如果既读了定义有non\_seq timing check 的lib, 也设了set\_data\_check, 则set\_data\_check 优先级更高。

set\_data\_check 用在哪?

set\_data\_check 通常用于信号间的skew 约束,比如一些高速接口相关信号间的约束。摘一段:

Data checks are normally applied where there is a specific requirement of skew (either minimum of maximum) or race condition (where the order of arrival of two signals can affect output and the intention is to get one of the probable outputs by constraining one signal to come before the other) between two or more signals. These may be required where:

- At the digital-analog interface within a chip where analog signals at the analog block boundary are required in a specific order.

- At the chip boundary, some asynchronous interface signals may have skew requirements.

set\_data\_check 在EDA 中的使用

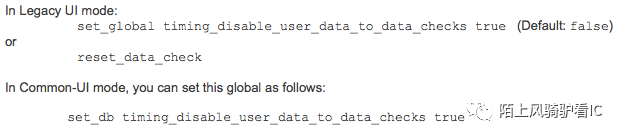

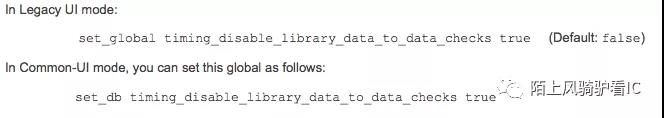

在Innovus 或Tempus 中『数据-对-数据』检查默认是开启的,可以用如下变量控制。

- 对于用命令set\_data\_check 设置的约束,可以通过如下变量控制:

- 对于lib 里定义的non\_seq timing check, 可以通过如下变量控制:

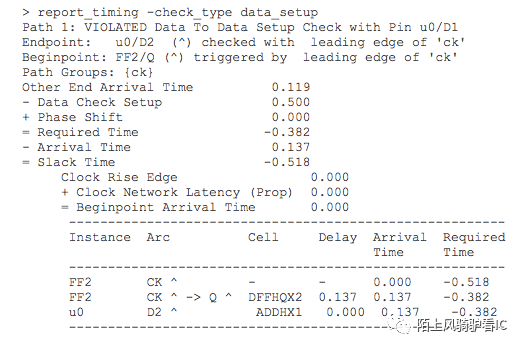

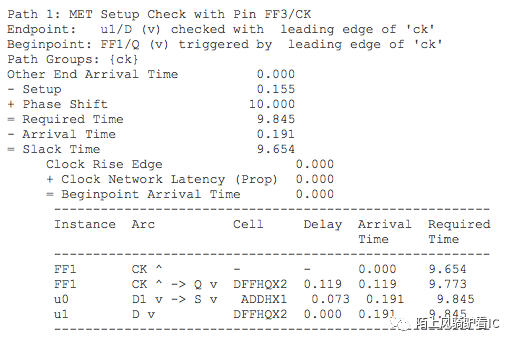

如果在Innovus 或Tempus 中设了如下约束,在report\_timing 的时候需要加-check\_type data\_setup/ data\_hold 来report 相应的data check:

set\_data\_check -from u0/D1 -to u0/D2 0.5

不像set\_max\_delay 会将原始的timing path 打断,set\_data\_check 是不会将原始timing path 打断的。

如上示例,即使在pin u0/D1 到u0/D2 上设了set\_data\_check 的约束,但是在timing 分析时u0/D1 不会被当做一个endpoint, 对于如上的path, timing 分析会同时做:

- u0/D2 相对于 u0/D1 的data check.

- 到寄存器u1 的setup/hold check.

在Innovus 或Tempus 中默认其他的false path 之类的timing exception 不影响data check, 可以用如下变量控制:

timing\_apply\_exceptions\_to\_data\_check\_related\_pin

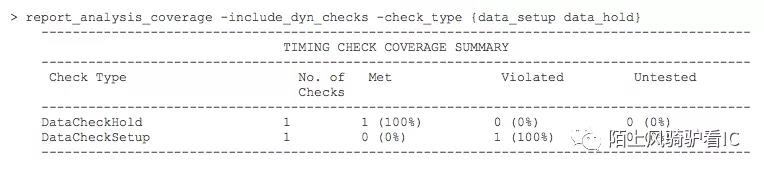

report\_analysis\_coverage 会将data-to-data check 归类于:DataCheckSetup 和DataCheckHold.

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/arB6LfCMalAYw8EtRzK2gA

作者微信公众号

相关文章推荐

•STA | Logical DRC

•大牛访谈:纯粹的技术控——旭姐

更多IC设计技术干货请关注IC设计技术专栏。