在数字实现过程中,如果把DFT 合到综合这一步,那只有综合跟布局布线是优化过程,其他步骤都是『验证』过程。所以只有综合跟布局布线会做逻辑更改,不论是综合还是布局布线都可以细分成多个步骤,在每一个细分步骤中都有逻辑的增减,对于每一步加入的cell 都会有对应的命名规则,这些命名规则对于PPA debug 很有用,可以根据这些命名规则得知相应的cell 是在哪一步加入的,依图索骥就可以到对应的步骤里去看,是否可以通过调整变量设置来约束工具行为以得到想要的结果。

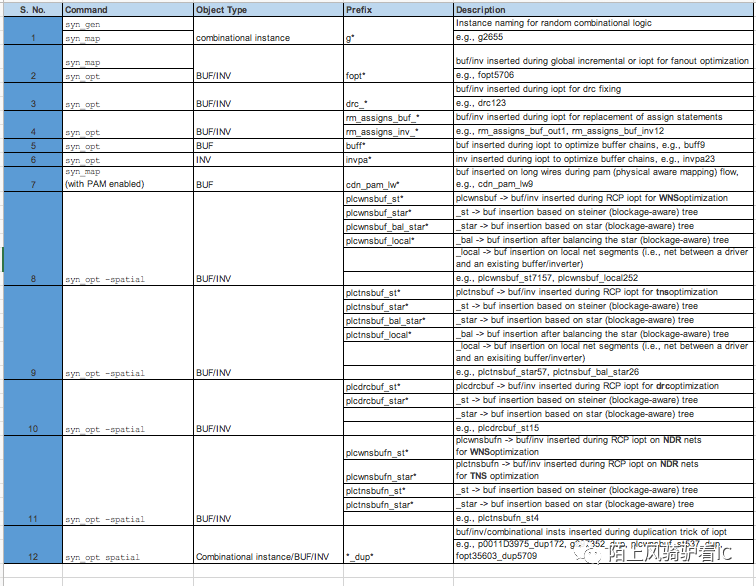

对于Genus 而言,命名规则为,可从文末参考文献中可找到 support.cadence.com 上对应的文章。

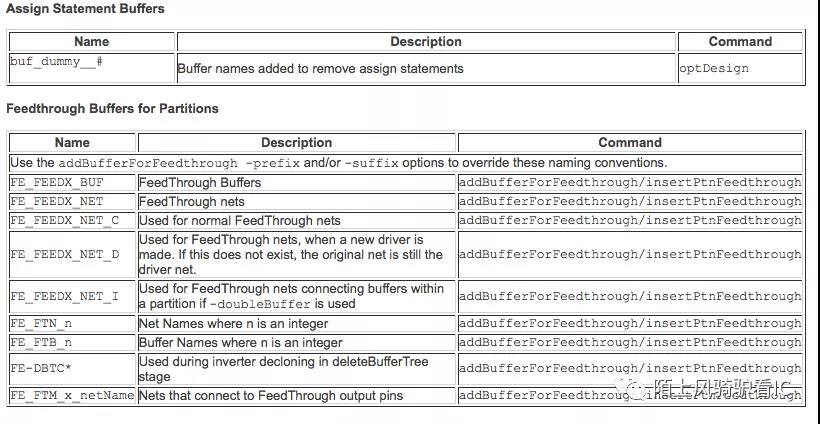

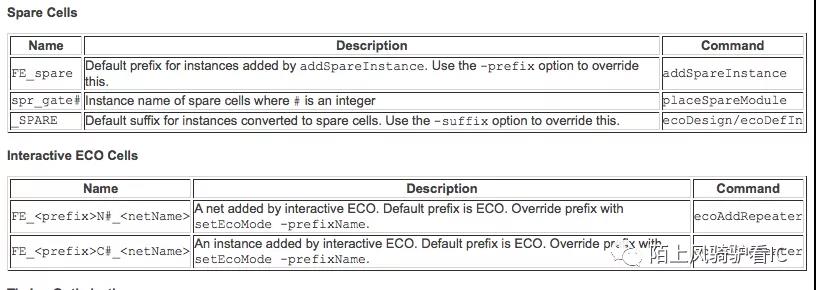

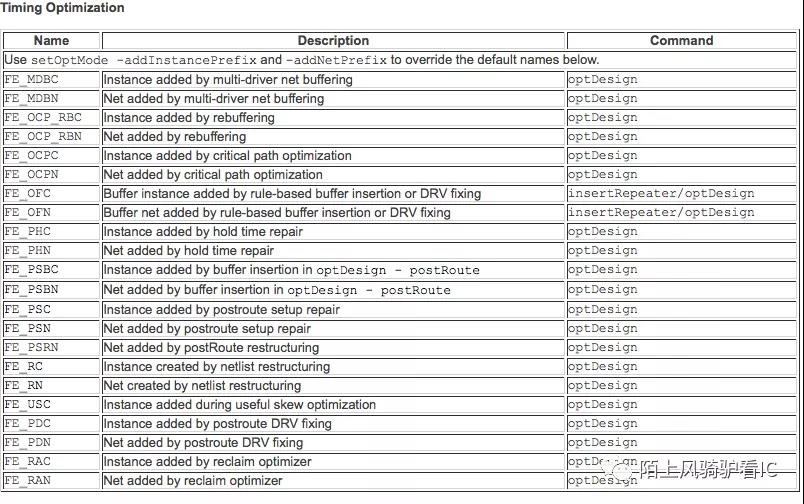

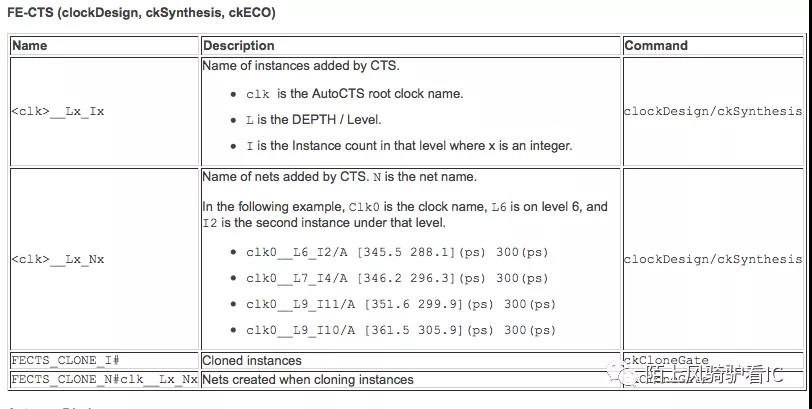

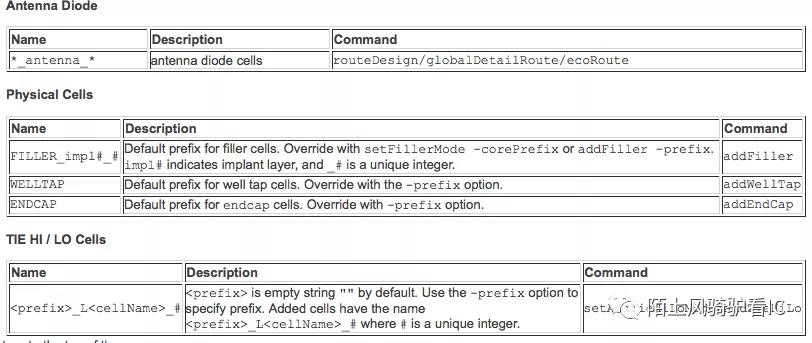

对于Innovus 而言,命名规则为,可从文末参考文献中可找到 support.cadence.com 上对应的文章。

参考文献:

https://support.cadence.com/apex/ArticleAttachmentPortal?id=a1Od0000000uuNrEAI&pageName=ArticleContent

https://support.cadence.com/apex/ArticleAttachmentPortal?id=a1Od0000000tWuvEAE&pageName=ArticleContent

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/vDHKDVr0lH6dc2ntMkiVmA

作者微信公众号

相关文章推荐

•lspatial | Early clock Flow

•大牛访谈:DFT一哥老K

更多IC设计技术干货请关注IC设计技术专栏。