在当前数字电路实现中,clock gating 是节省动态功耗最有效且成本最低的办法,所以一直以来业界都在想方设法进一步去挖掘,期望用这种低成本办法进一步节省动态功耗,如XOR clock gating. 关于clock gating 驴曾码过三篇短文《clock gating | 从ICG cell 在 library 中的定义说起》、《clock gating | Gating 的插入与验证》、《clock gating | clock gating 的timing check》。

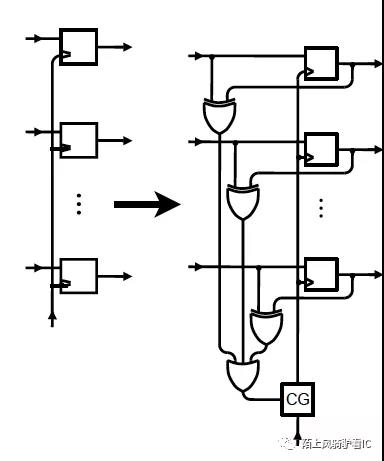

前几天接触了一个新概念,ODC-based Clock gating, 研读了一些文章,有了个大致的概念,码篇短文总结一下。下图是综合工具插clock gating 时,逻辑的映射,即将寄存器D-pin mux 的选择信号用于Clock gating 的enable 信号,此处最关键的就是enable 信号的抽取,传统做法是从RTL 语句中直接抽取。

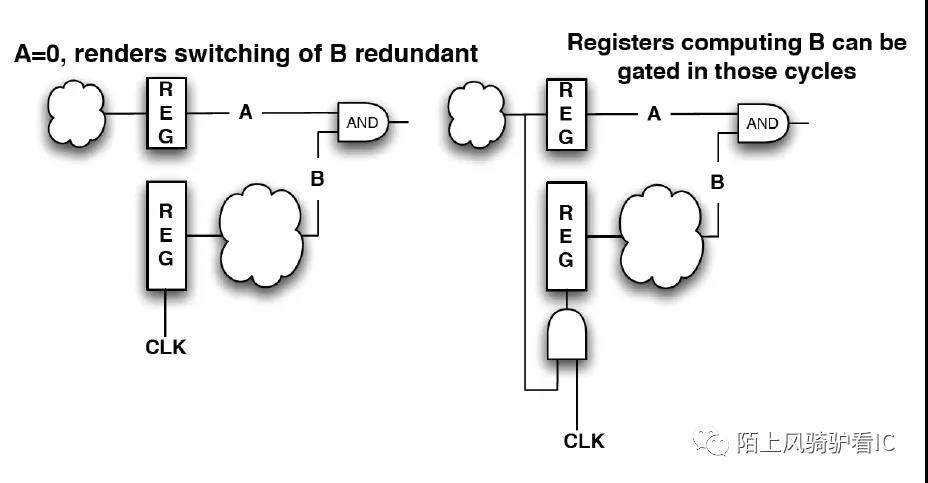

所谓的ODC 即是:Observability Don’t Care 的首字母缩写,以下图为例,当A=0 时,不论B 如何变化,"AND 门"的输出都是0,此时B 点即为Observability Don’t Care 点,所以如果可以将B 点源头的寄存器gate 掉,那后续逻辑的无效翻转都会被消除,从而节省了功耗。

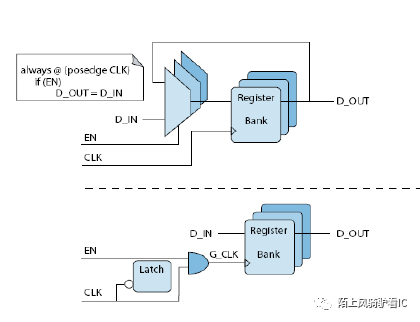

以下图为例,在传统综合流程中,为了保持逻辑一致性,如果在RTL 中只有寄存器dout 的描述中有 "if (vld\_d2)", 那工具只会对dout 插gating, d\_1, d\_2 因为缺少enable 信号不会被gating, 但是d\_1, d\_2 都是Observability Don’t Care 点,如果可以gating 就能省更多功耗。

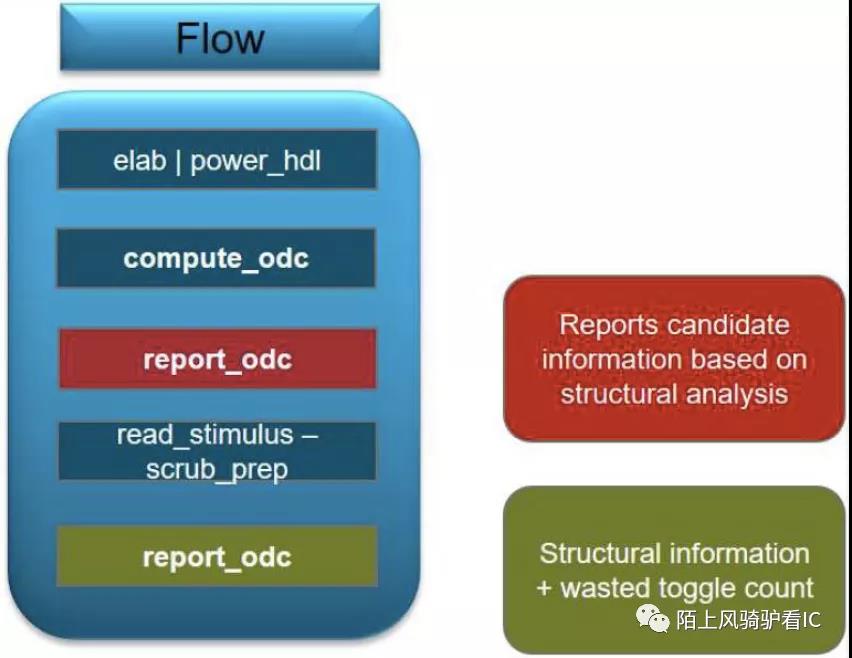

要想让工具对这些ODC 点插gating 就需要在RTL 中把对应的enable 加上,如果在写代码时无法确定这些ODC 点,可以借助Joules 对RTL 进行分析。Joules 的 ODC-based Logic Gating 流程大致如下:

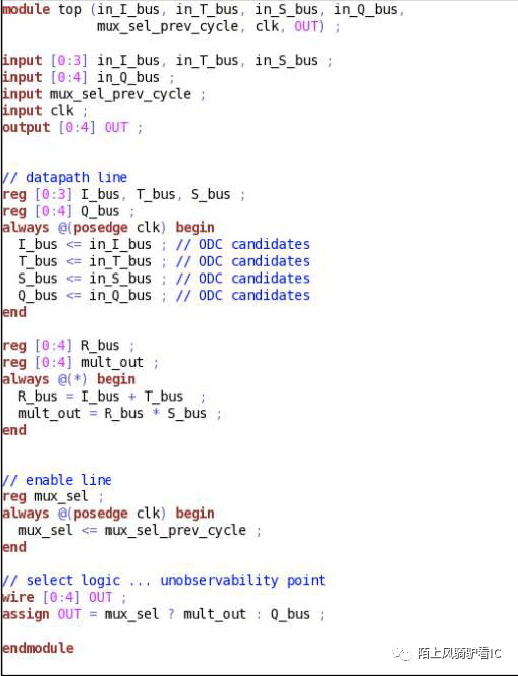

对于如下一段代码,I\_bus, T\_bus, S\_bus, Q\_bus 因为没有enable 信号,工具无法对其插入clock gating,但因为最后选择逻辑的存在,I\_bus, T\_bus, S\_bus, Q\_bus 都是ODC 点。

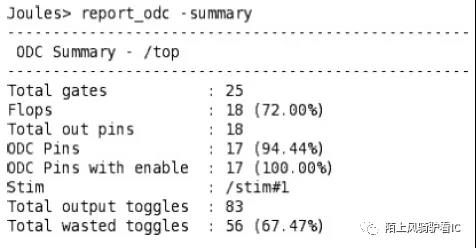

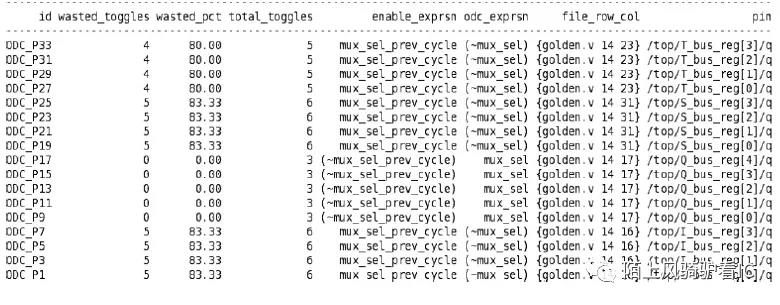

在Joules 中用命令report\_odc 和report\_logic\_gating 可以报出代码中所有的ODC 点,及可用的『enable 信号』。

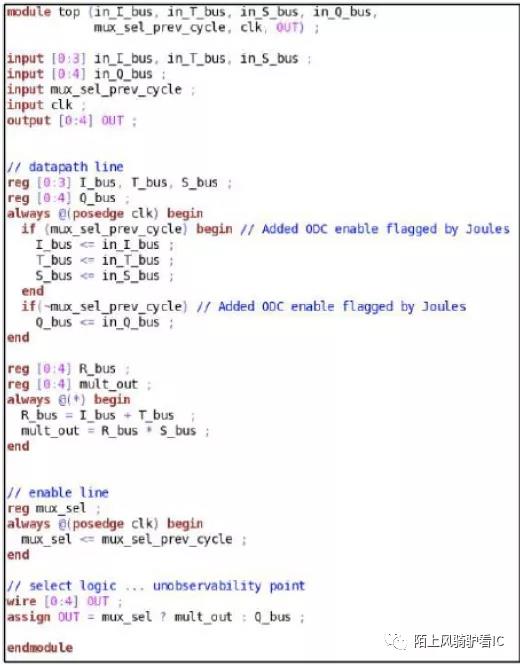

根据Joules 的report 可将代码修改为如下形式,如此,在综合时工具就可以插入更多的clock gating.

在数字电路中 clock gating 从设计开始就需要考虑,在某文中读到设计实现中要考虑的一些点,甚是认同,搬运至此:

- Identify registers with low data activity, additional CGs would cost area.

- Grouping registers and building an XOR tree, introduces a single CG for the group.

- To guarantee power reduction, method should be based on placement information.

- Timing and congestion are affected.

- Activity driven clock gating: 1) Clock gating should be done if it helps improve overall power, based on switching activity; 2) There can exist more than one scenarios that need to be optimized; 3) Clock gating should not be done for high switching activity registers.

- Placement-driven optimisation: Cloning/Merging of clock gates.

- Observability Don’t Care: 1) Registers whose outputs are not observable, during a clock cycle, should be isolated; 2) Ability that can ‘observe’ a logic path beyond a clock-to-clock boundary; 3) De-Assert a data path if its forward stage is gated; 4) De-Assert forward stage, if the current stage is gated; 5) Apart from sequential power savings, combinational logic cones can also be gated.

- Leakage/Static Power Impact: All clock gating techniques should comprehend total power.

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/pg13mCI5e-ceP5BouqpybA

作者微信公众号

相关文章推荐

• 大牛访谈:传说中的小西

•形式验证 | LEC,CLP\,LP-EC 的区别

更多IC设计技术干货请关注IC设计技术专栏。