最近在泡VLSI System Design 这个网站,看到了多年前牛人们码的许多文章,内容翔实无一句废话,内容质量比我这破号好太多了,今天搬一篇Crosstalk 分析的文章,原文题目是《 Effect of Coupling Capacitance》可以点击本文左下角『阅读原文』跳转到原文。关于串扰老驴之前挖过一个坑《论STA | 数字电路中的串扰》,一直也没填,争取2020 年活着填完。

文章开宗明义,从130nm 开始互连线之间的耦合电容不能再忽视,耦合电容可以造成两种影响:导致逻辑功能失效,即Glitch; 影响延时,即Delta Delay.

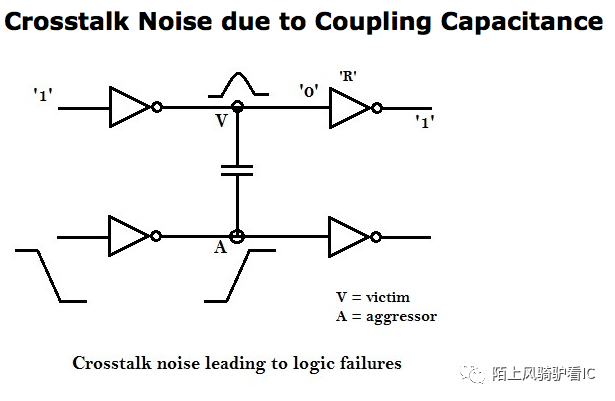

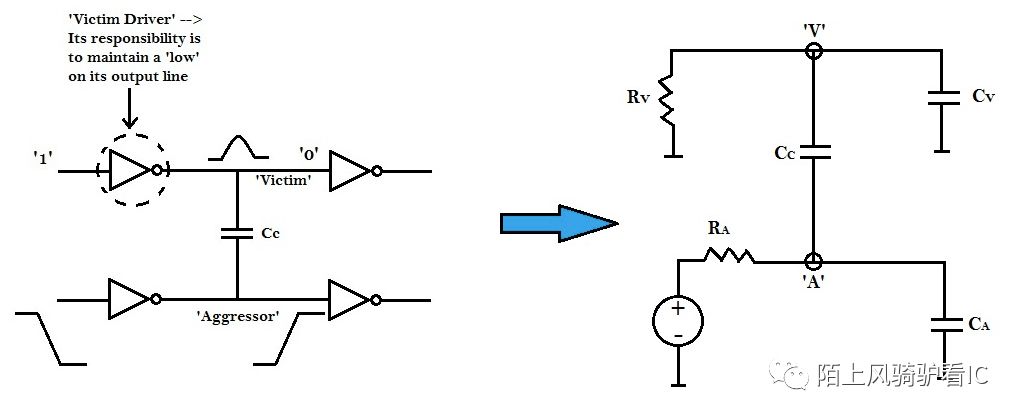

Giltch

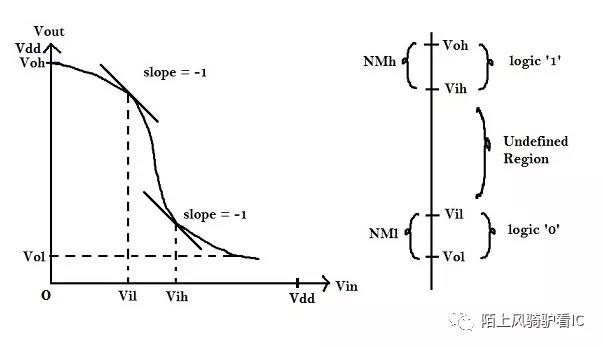

一张简明扼要的图,当A 点翻转时,由于耦合电容的存在,V 点会受到『扰动』,如果V 点扰动的范围超出扇出反相器的噪声容限R 时,反相器的输出就会翻转。噪声容限是CMOS 电路逻辑功能不受影响的情况下所能承受的噪声量,噪声容限可以确保任何逻辑为“1” 的信号加上有限的噪声,仍然被识别为逻辑为“1” 而不是逻辑为“0”。 拿最简单的反相器为例,理想情况下:

- 输入高低电压为:Vil=0, Vih=Vdd.

- 输出高低电压为:Vol=0, Voh=Vdd.

- NML(Noise Margin low) = Vil - Vol =0;

- NMH(Noise Margin high)= Voh - Vih = 0;

但是由于 "Voltage drop" 跟 "ground bounce" 效应,通常Vih 小于Vdd, 假设其值为Vdd', 而Vil 大于Vss, 假设其值为Vss'. 于是实际电路中,噪声容限的定义为:

- NML(Noise Margin low) = Vil - Vol = Vss'

- NMH(Noise Margin high)=Voh-Vih=Vdd-Vdd'

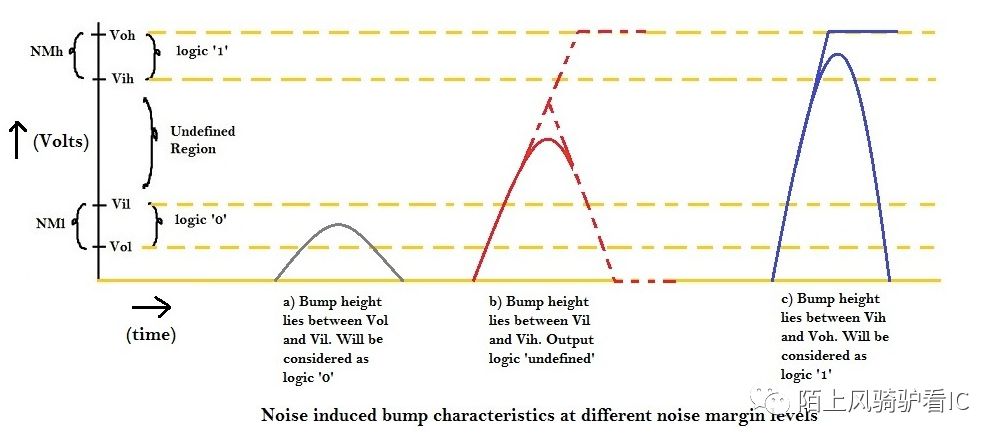

回到第一副图的示例,当V 点的扰动:

- 介于Vol \~ Vil, 则扇出反相器不会发生翻转;

- 介于Vih \~ Voh, 则扇出反相器一定发生翻转;

- 介于Vil \~ Vih, 则扇出反相器可能翻转也可能不翻转。

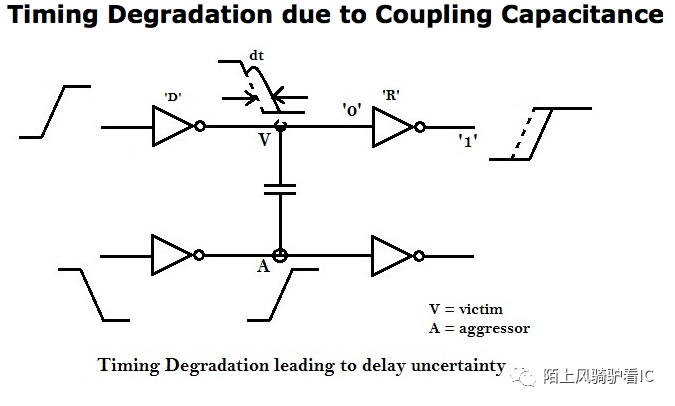

Delta Dealy

又一张简明扼要的图,当V 点驱动反相器的输入从 0-> 1 翻转时:

- 如果A 点驱动反相器的输入恰好从 1->0 翻转,A 点会对耦合电容进行充电,从而拖延V 点的翻转,使得V 点的延时增加了 "dt".

- 如果A 点驱动反相器的输入恰好也从 0->1 翻转,A 点会对耦合电容进行放电,从而加快V 点的翻转,使得V 点的延时减少了 "dt".

- 在STA 分析时,在计算late path delay 时假设所有的『攻』跟『受』都是同性相斥,异向翻转,在计算 early path delay 时会假设所有的『攻』跟『受』都同性相吸,同向翻转,所以在clock path 上同一个串扰点,会分别在launch clock path 跟capture clock path 上分别计算一次,而且即使是common path 上的串扰,在做非同沿check 时(如 setup check), CPPR 也不会将其减掉,所以在timing 难收的设计中,要尽量把clock 上的串扰干掉。

Crosstalk Modelling and Analysis

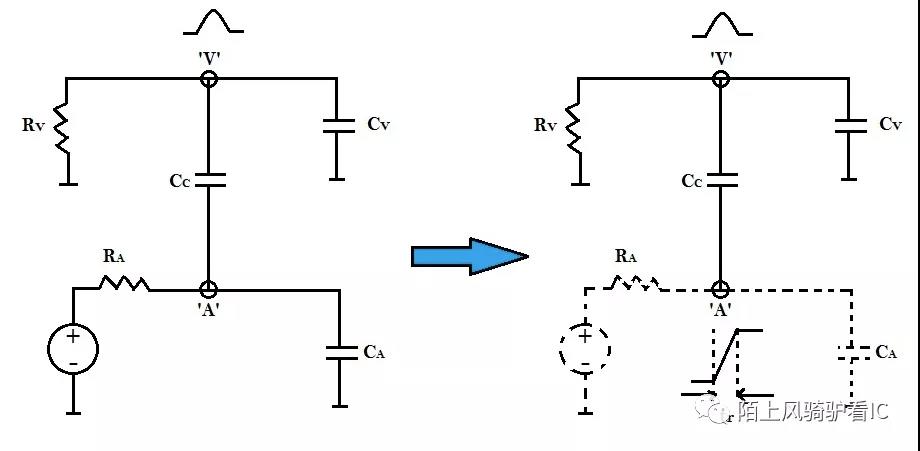

将『攻』跟『受』的驱动用电阻RA 跟 RV 表示,负载用CA 跟CV 表示,耦合电容用CC 表示,电路可以进一步简化为,则A 点的上升时间为:

tr = RA * ( CC + CA ) .

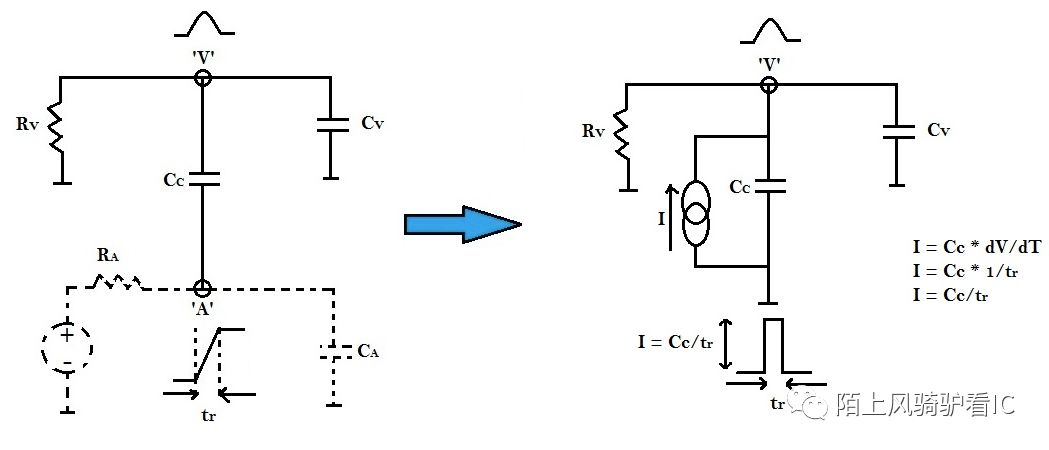

上图串联耦合电容的电压源电路可以等效转化为并联耦合电容的电流源,那么V 点的电压为:

Vfinal = I * R

Vfinal = (CC / tr) * RV

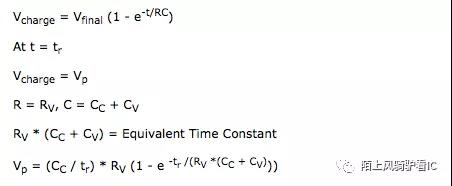

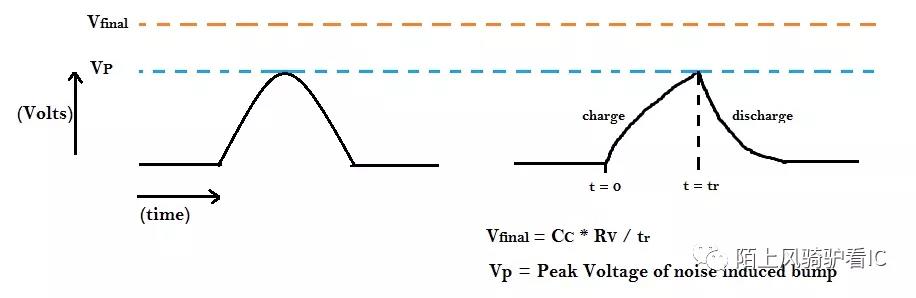

串扰引起的电容充放电波形如下,充电电压为:

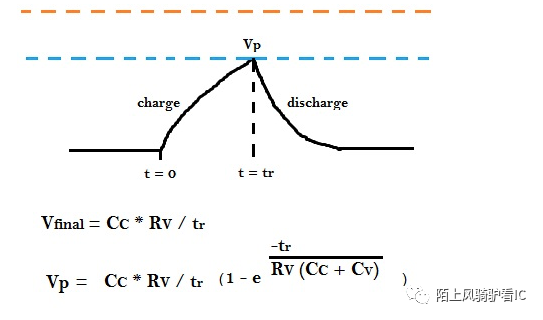

由下图可知,V 点由串扰引起的峰值电压是耦合电容、『受』前驱动器的驱动强度,『攻』的上升时间的函数。

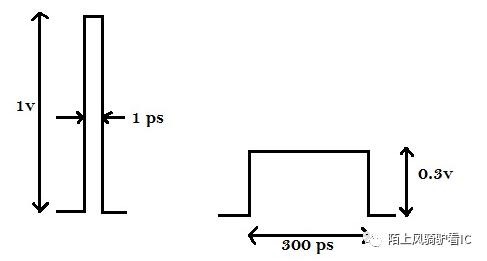

在STA 分析时,并不是『受』点峰值电压超过噪声容限就一定可以导致其扇出翻转,如下图,当串扰持续时间太短时,并不能引起『受』点扇出翻转,所以通常都是要计算『电压 X 时间』的面积,用以判断该Glitch 是否可以引起逻辑失效。

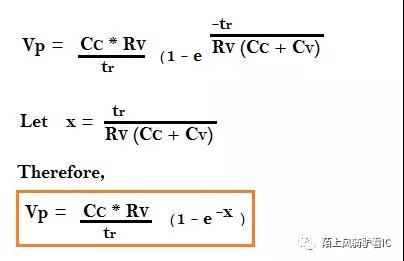

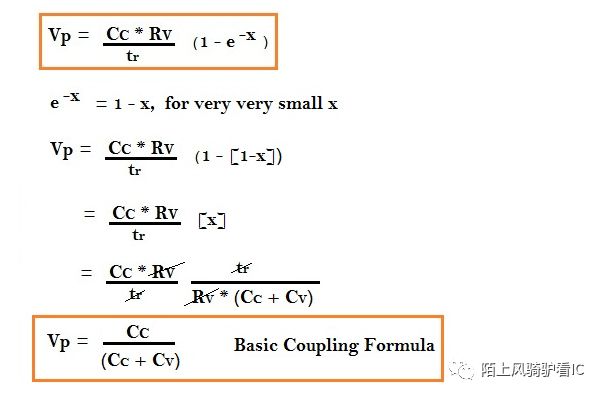

别人码文都是从公式入手,专业且高级,『受』点的峰值电压:

如果Rv(CC + CV) 远远大于 tr 则 e-x \~ (1 - X), 可得峰值电压:

『受』点由串扰引起的脉冲宽度取决于『攻』的翻转时间,『攻』翻转越快,『受』点由串扰引起的脉冲宽度越窄。

根据如上分析,消除串扰的方法有:

- 增加『受』点驱动的电阻:To increase the Resistance of Victim driver (RV).i.e. downsize the victim driver, so that, the high resistance of the victim driver restricts the supply of current and charging of victim net capacitance during the rise time (tr) of aggressor signal, which would in turn reduce the bump height.

- 增加『受』点负载电容:To increase the Capacitance of Victim load (CV).i.e. upsize the victim load, thus the resistance will reduce, which will in turn help the victim net to maintain a strong static voltage.

- 缩短『攻』的翻转时间:to maintain sharp transitions on aggressor.

- 加隔离:to introduce shields in between victim and aggressor.

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/b42F0UctZhwis3UofWtamw

作者微信公众号

相关文章推荐

•形式验证 | LEC\,CLP\,LP-EC的区别

• 大牛访谈:传说中的小西

更多IC设计技术干货请关注IC设计技术专栏。