低功耗检查是低功耗设计必不可少的一个环节,此处所谓的低功耗设计指:多电压域设计,实现过程中在原有功能逻辑基础上插入低功耗单元,如:isolation cell, level shifter cell, retention register, power switch 等。

低功耗设计涵盖于设计流程的每一个环节:架构设计确定电压域划分,designer 负责power intent <1801>编写,验证人员完成low power verification, 实现人员负责各种插入并做插入后检查。

低功耗检查很重要,涉及到的面也多,需要对设计、电压域划分、power intent 语法及对应的实现流程都熟悉,当然还要熟练掌握低功耗检查工具——CLP 可谓低功耗检查领域的霸主——世上如果有一个工具,上手简单、使用方便、Debug 功能强大,一天熟练,一周变老司机,那定非CLP 莫属。

CLP 可以做什么

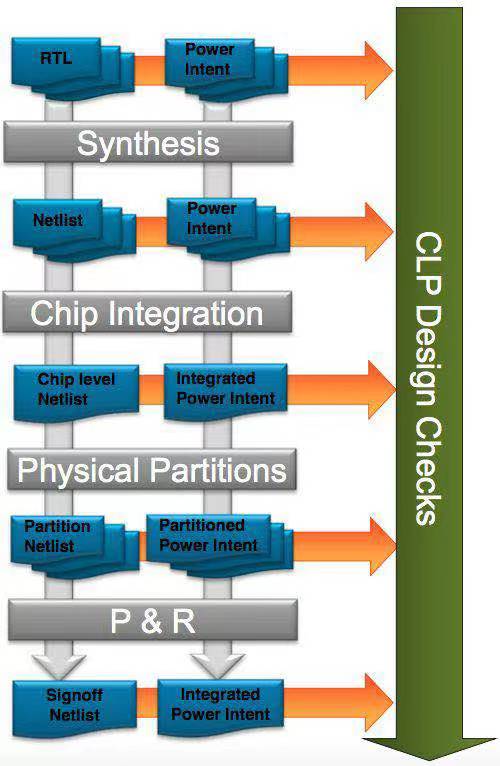

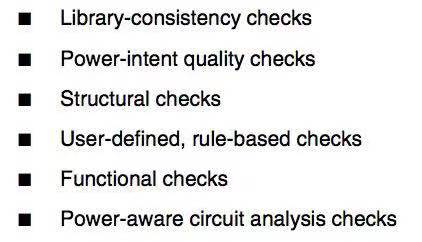

对于低功耗设计,从RTL 到GDS 的每一步都要用到CLP, 在RTL 阶段可以用CLP 检查power intent 的质量,在集成阶段可以用CLP 做power intent 的集成,在综合到P&R 每一个实现阶段都需要CLP 检查low power cell 插入是否恰当。

CLP 1801 flow 是什么样

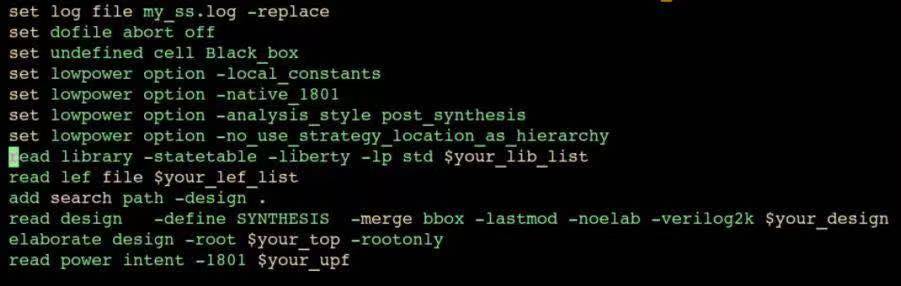

CLP 1801 flow 十分简单,只要读入lib/lef, RTL/netlist, power intent 即可,最关键的命令是 set lowpowr option, 用于指定power intent 是CPF/UPF/1801, 用于指定当前分析是针对哪个阶段的设计,用于指定constant signal 的power domain 信息等,该命令有许多option, 且针对CPF 跟1801 有不同的option 组合,通常一般设计大部分option 用默认值即可,对于特殊设计,根据需求加不同的option 即可。

CLP 结果呈现

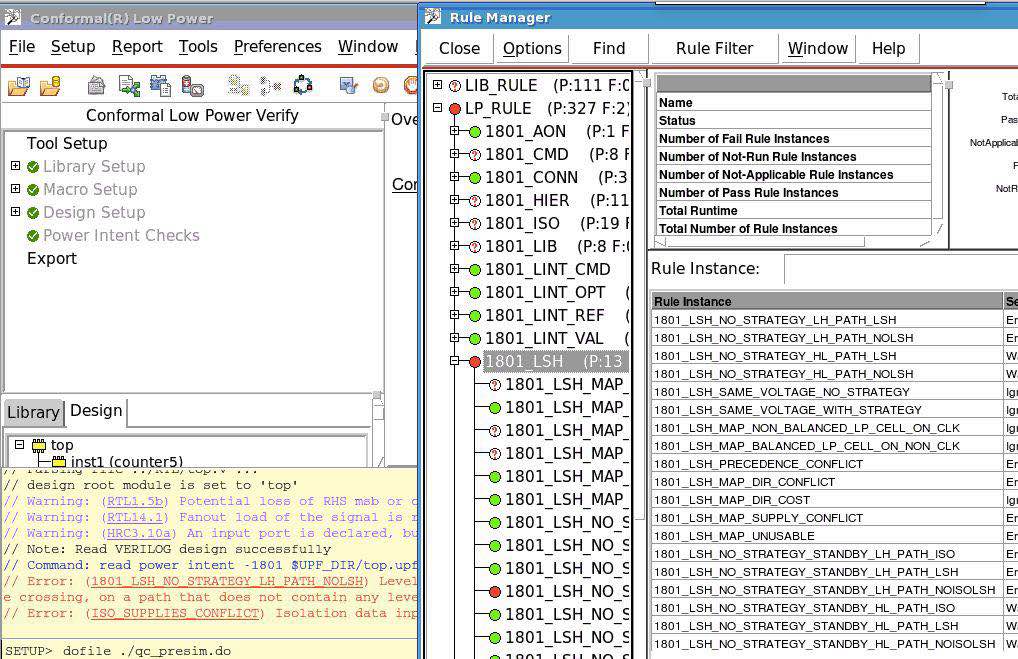

推荐用GUI 来check CLP 结果,run 完CLP 之后,打开low power rule manager 『点击工具栏上长得像电池的那个图标』,会将所有的violation 归类,绿色的表示没问题通常不用关注,红色的表示有violation 需要特别关注,黄色的表示有warning 通常也需要关注。

如何Debug CLP

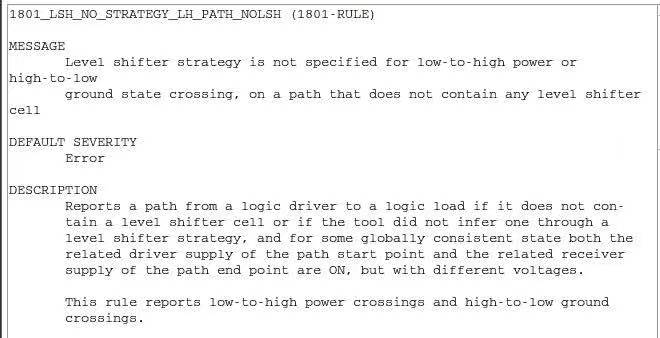

CLP 的debug 手段十分简单明了,点开某一个violation, 右键选中对应的violation -> report rule check, 会得到该violation 的详细信息,可以点击rule 的ID 得到该rule 的详细解释跟常用的解决办法。

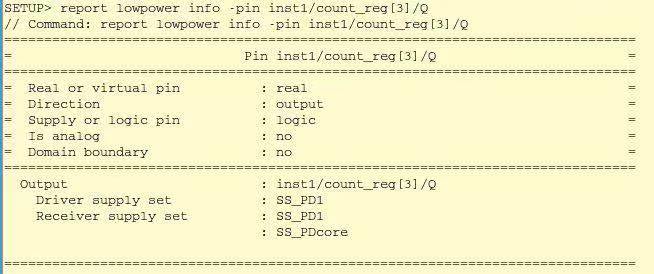

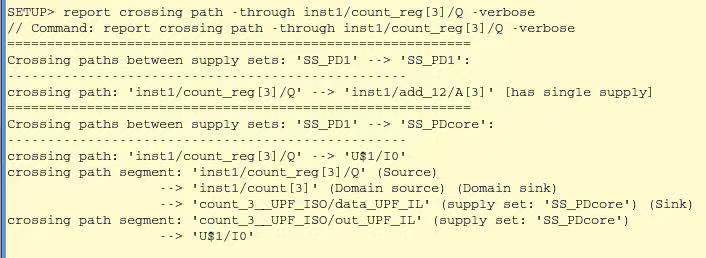

除此之外,CLP 1801 flow 有两条大牛逼命令:report lowpower info 跟report crossing path, 用这两条大牛逼命令可以解决90% 的问题。

结语:在实现阶段做低功耗check ,记住九字箴言:不乱插、不漏插、不多插。CLP 用起来简单方便高效,但是要求使用者对自己的设计十分了解,对1801 十分了解。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/2-IlswuKEl91UL1z6XfFMQ

作者微信公众号

相关文章推荐

•Innovus Mixed Placer

•大牛访谈:我的益友良师——伟哥

更多IC设计技术干货请关注IC设计技术专栏。