越熟悉的东西越不知从何下笔,总觉得就那一眼东西,没什么可写的,想试一下按照每一步要检查的东西或debug 时候常需要看的东西写一下,简单基础但是重要。

相比STA 或P&R, 综合表面看似简单,其实涉及到的步骤跟算法要比前两者繁杂艰难得多。STA 考虑的因素再多,也只是一个分析工具,只需要根据已有的东西做计算即可,所有逻辑优化工具都比分析工具复杂。

而相对于P&R, 综合需要将设计从RTL 级转化到gate 级,在转化过程中:

- 需要做数据路径结构选择、冗余逻辑优化、同等逻辑合并、常值优化、工艺库映射等;

- 如果是带物理信息的综合,还需要做module placement, cell placement, global routing, congestion 优化等;

- 如果是多电压域设计,还需要结合power intent 插入low power cell;

- 如果要做可测性设计,还需要插入所有DFT 相关的逻辑。

而且整个过程都需要在Performance, Power, Area 三者之间做『竞选』,如功耗优化对实现工程师可见的是:clock gating insertion, operator isolation, multibit merging, Multi-VT leakage optimize, dynamic power optimize, retiming等。在整个过程中,只要有一步做得不够不好,就得重头再来。

对于综合而言,结果的好坏基本取决于三个因素:

- 输入质量,决定80%, Garbage in Garbage out, 是真理。

- 工程师素质,决定15%, 是否能对输入做透彻分析、是否对工具足够了解,是否能对输出做有效解读,是否具有debug 90% 的非工具问题的能力。

- 工具能力,EDA 发展到今天,综合端不论是在方法学上还是工具端都极度趋同,论及能力无非是:算力——可处理设计的大小、优化速度,优化能力,用户友好度,就目前世面上常用工具而言,只能决定5%.

综合流程可以粗暴地划分为如下几步:

- 输入文件读入,输入包括lib, lef, qrc, rtl, sdc, power intent, def等。

- 工具变量设置,目前世面上的工具都是『通用』工具,所谓通用是指:其不针对某类特定设计、某一个或几个特定目标;所以都有大量的变量,需要硅农根据设计本身的特性和目标去做对应设置。

- 优化,根据输入的限定,工具自己闷头苦干。

- DFT 插入,根据可测性设计的目标,插入所需逻辑。

- DFT 插入后优化,包括逻辑优化及物理优化。

从综合流程看,首先读入的是library, 所以要求硅农对library 十分了解,这可以避免许多不必要的问题。额外提及一点,在读lib 时如果要用search path 就明确指定,工具都有默认的search path, 老驴一直以为这种默认search path 就是卖给老年人的保健品,不仅无用还有害。

在开始做综合之前,强烈推荐去解读跟分析library, 老驴就当下想到的点列一些,望请驴友补充:

- 明确library 中定义的unit.

- 明确library 中定义的operating condition.

- 明确library 中有多少cell, 有无特殊定制cell.

- 明确每个类型的cell 有哪些size 哪些VT, 各size 各VT 之间的PPA 有什么差别。

- 明确每个类型cell 的delay, output transition, internal power 跟input transtion 和output load 之间的关系。

- 明确知道有哪些多pin cell, 根据设计是否congestion 敏感确定是否可用。

- 明确哪些cell 不推荐使用,哪些cell 是为了特殊用途。

- 明确有哪些可用的low power cell.

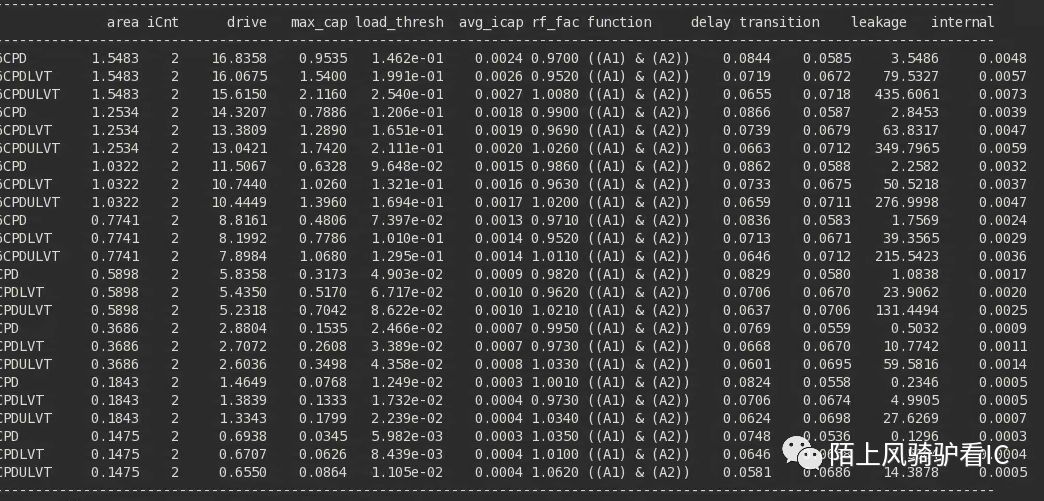

上述各点,大部分可以从library 中直接读出,对于每个类型cell 不同VT 不同size 间的PPA 对比,过去在工具端没有直接命令的时候需要借助脚本去分析,如今工具会有对应的命令,如在Genus 或Joules 中用命令:report\_libcells 可以报出指定cell 的相关信息,如下图报了某工艺下在输入transition 跟输出load 相同时,二输入与非门不同VT 跟不同size 的一些属性,从该report 可以一目了然delay, leakage, internal power 等信息。

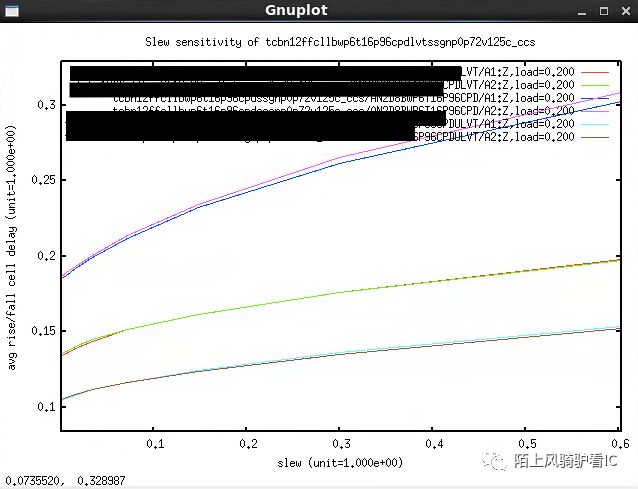

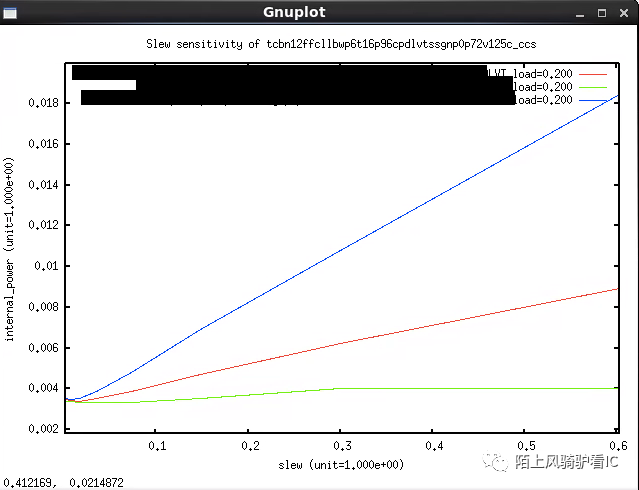

也可以借助工具画一些更直观的图出来,如下是在load 一定时,第一副图是cell delay 跟输入transition 之间的关系图,第二幅图是internal power 跟输入transition 的关系图。

老驴以为,所有数字实现端的硅农都需要对library 有清晰且准确的认知,这样才能更明确用哪些cell 穿成的项链挂到你的脖子上才更美丽。

最后,祝大家健康!

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/3vm7iDjv8apwcxmFjma9lg

作者微信公众号

相关文章推荐

•从EDA使用,捋数字芯片设计实现流程 | 实现

•低调的实力派:Conformal

更多IC设计技术干货请关注IC设计技术专栏。