《抽刀断水水更流,RC Corner不再愁:STA之RC Corner》发出之后,陆续收到一些问题跟指正,打铁趁热,总结于此,来,一起继续讨论完善。

Q:还有一种RC corner 带后缀『\_T』,只用于setup signoff,T指的是什么?

A:T代表tighten,在rc的variation上的sigma分布比不带T的更紧,因此只能用于setup,hold不推荐。Appleto Apple地比较,T的variation更小,理论看到的rc变化更小,单从setup产生violation的可能性更小。至于悲观还是乐观,除非自己定criteria,其余的follow foundry或者vendor的rule最重要。

Q:为什么setup既需要sign-off C-corner又需要sign-offRC-corner?

A:因为C-corner表示『电容』最大/最小,而RC-corner是『电容*电阻』最大/最小。通常对于短线而言,电容占主导地位,C-corner可以cover RC-corner,但对于长线则电阻占主导地位,C-corner无法cover RC-corner,而是反过来RC-corner去cover C-corner。而没人保证一个设计里只有短线没有长线,也没权威对长短的幅度有量化的定义,所以最保险的就是两者分别sign-off。

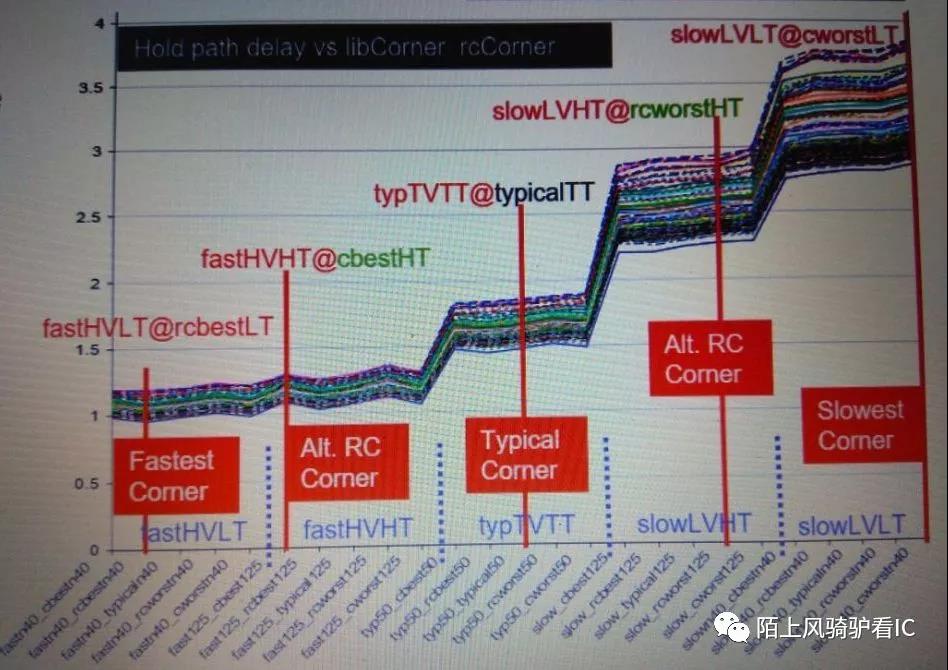

Q:为什么hold需要sign-off所有的corner?

A:对于hold而言,根据其仿真曲线,相互之间都无法完全覆盖,故需要sign-off所有corner。

图片来自网络

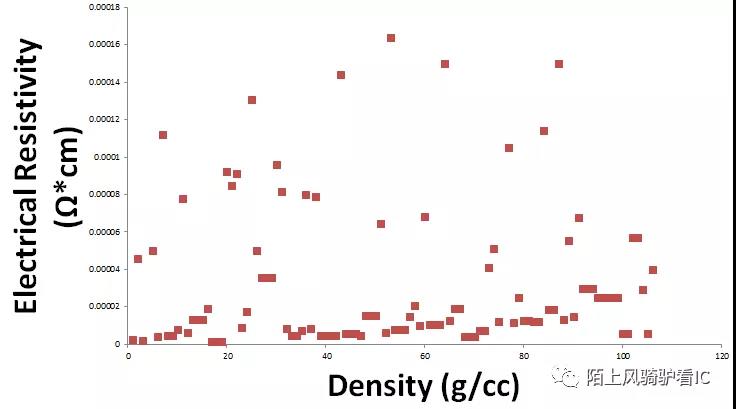

Q:金属电阻是否跟density/spacing相关?为什么方块电阻跟density/spacing相关?

A:就电阻本身而言,阻值跟density没有关系,只跟金属线自身的宽厚和电阻率相关,详细描述:

There is no relationship between the density of a metal and itselectrical resistivity.

There is a big database of material properties called MatWeb which is recommend as a legitimate source of data by UCSD's and Stanford's library systems, Rose-Hulman, etc. I took data fromaround 60 different metals and graphed them:

As you can see there is no empirical relationship. From a theoryperspective, density has to do with atomic packing and resistivity has to dowith electronic structure.

Iwill admit, however, that gaseous copper is an extremely poor conductor.

但是,在半导体制造过程中,由于工艺偏差,电阻跟金属线的density是相关的。此时,电阻率是线宽跟线间距的函数。这一关系,在foundry给的工艺文件里都有相应的描述,这些都是在抽RC时需要考虑的因素。

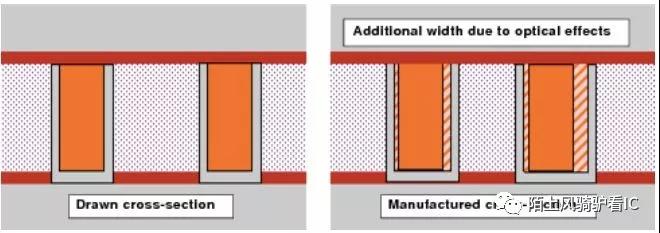

Resistivity as a Function of Width and Spacing (Rs = f(W) or rho=f(W,S))

Variationin resistivity is caused by a number of phenomena. Copper is a softer materialthan the dielectric in which it is embedded. As a result, the polishing of thewafer during the CMP process has a tendency to remove a little extra copperfrom the top of the wire. This effect is called dishing because of the shape ofthe resulting wire top. The effect becomes more pronounced as the wire widthincreases. This effect is shown in exaggerated form in following pic.

To reduce theeffect of dishing on wide wires, small holes, or slots, can be inserted atregular intervals in wide wires. These slots insert a form of hard"posts" in the wire so that the CMP process removes less copper. Thistechnique reduces the dishing, as well as the effective resistivity.

Anothercontributor to resistivity variation is the cladding in copper wires. Claddingis the material grown around the sides and bottom of copper wires to protectthem from chemical reactions with the dielectric material. This cladding isillustrated in gray in following pic. The thickness ofthe cladding on the sides and bottoms of wires also varies with the width of awire. Because cladding has a much higher resistance than copper, it impacts theeffective resistivity of copper wires. This effect is more pronounced in thenarrowest wires. The combination of the effects ofdishing, slotting, and cladding thickness is modeled by the wire resistivity asa function of the wire width in silicon, and its spacing.

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/zmLIPoUvxyHWPV3vFR1DUA

作者微信公众号

相关文章推荐

•Innovus Mixed Placer

•大牛访谈:我的益友良师——伟哥

更多IC设计技术干货请关注IC设计技术专栏。