《clock gating | 从ICG cell 在 library 中的定义说起》陈述了clock gating 在library 中的描述,本文捋一捋综合时clock gating 的插入跟插入clock gating 后的形式验证。目前大部分设计都会在RTL 中时钟的『根部』例化一些『全局』的clock gating cell. 在综合时再指定工具对满足要求的寄存器组更精细地插入clock gating cell. 先抛开对工具具体的约束,综合工具插入gating 时的核心算法是从RTL 中提取gating cell 的enable 信号,以保证每个gating cell 的插入都能有效地减小动态功耗。

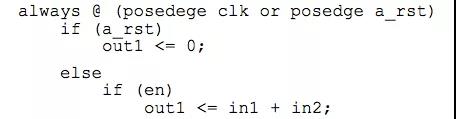

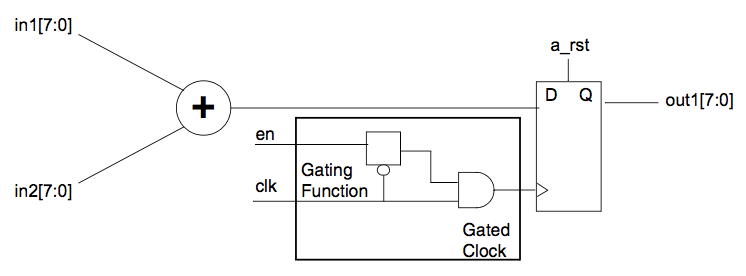

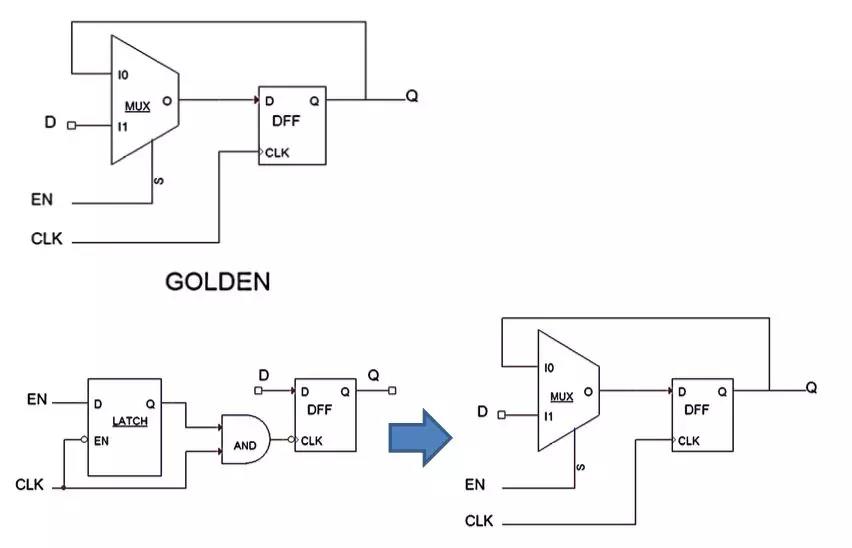

以最常见的异步复位寄存器为例,对于这样一段代码,『直译』的逻辑结构如下,每个寄存器的D-pin 输入都是一个二选一的MUX, MUX 的一个输入是寄存器Q的反馈,表示在en 信号无效时寄存器的值不变;MUX 的另一个输入是加法运算的结果,表示当en 信号有效时寄存器的值更新。在综合时,如果使能了clock gating 的插入,而且寄存器组的个数满足用户设定的约束,工具先会从代码中提取enable 信号,对于这样简单的逻辑很明显en 信号就是enable 信号,但实际设计中的enable 信号可能是一个非常复杂运算的结果,工具需要分析提取,以确定每组寄存器公共的enable 信号。

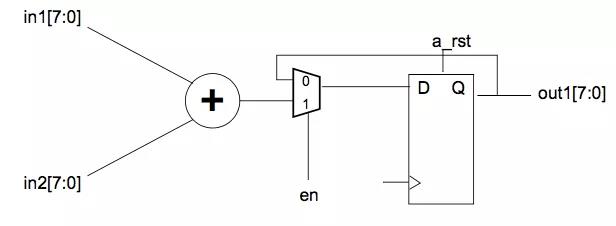

Clock gating 的原理十分简单,即:将D-pin MUX 的选择信号用来控制时钟,在寄存器不需要更新数据的时候将clock 关掉,在寄存器需要更新数据的时候将clock 打开。插入clock gating 后的电路如下,插clock gating 前每个寄存器都有一个mux, 这些mux 有相同的控制信号,在插gating 时,工具用一个gating cell 来控制这一组寄存器的clock。在该示例中,相对于『直译』电路,插入gating 后的电路,用一个ICG cell 代替了8个二选一的MUX,即省了功耗又减小了面积。

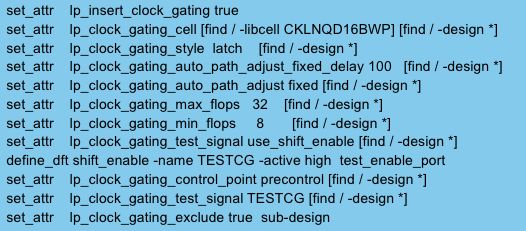

如今综合工具插入gating 的技术已十分成熟,用户只需要根据需求设置约束,剩下的交给工具即可。DC 用命令set\_clock\_gating\_style + 各种option 来约束,Genus 用set\_attribute 来约束,至于约束的内容两个工具大同小异,如:使能clock gating 的插入,用哪个ICG cell 做gating cell, ICG cell 的类型,对gating cell 的过约,每个gating cell 最多能带多少个寄存器最少必须带多少个寄存器,用哪个信号接ICG cell 的TE-pin, ICG cell 的控制是precontrol 还是postconstrol, 哪些寄存器不需要做clock gating 等。

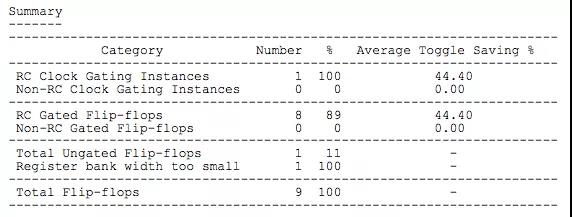

插完clock gating 后需要检查gating 的效率及覆盖率,在Genus 中用report clock\_gating 可以得到一个如下的summary, 在实际项目中,一定要确认插入的gating 个数。

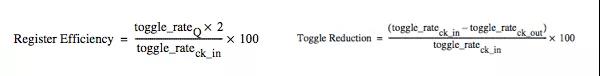

除了覆盖率之外,可以用register\_efficiency 跟toggle\_reduction 这两个指标来检验gating 的效率。register\_efficiency 用来衡量clock 是否只有在寄存器需要load data 的时候才发生翻转;toggle\_reduction 用来衡量gating 减少的toggle 百分比。

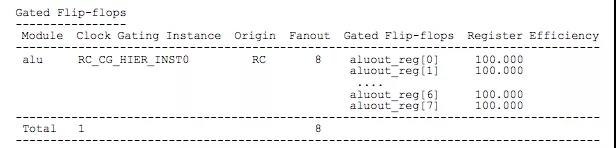

在Genus 中用report clock\_gating -gated\_ff 得到register\_efficiency:

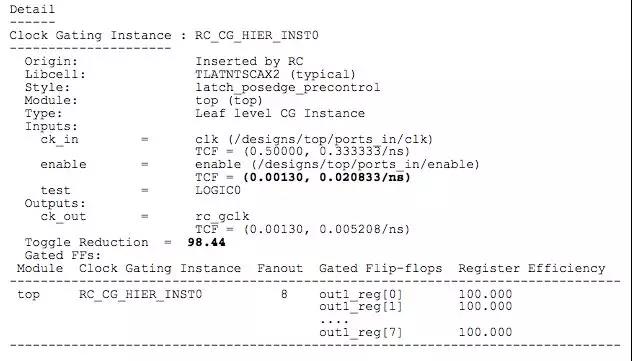

在Genus 中用report clock\_gating -detial 得到每个gating cell 可save 的toggle\_reduction:

Note:

- clock gating 是时钟树上的cell, 在综合时就要予以考虑sign-off 时不同corner 的variation, 体现在综合时选择使用哪种类型的gating cell, 如果后端没有明确要求,常见做法是:使用同CTS 所用buffer/inverter 相同VT 的ICG, size 可选X4\~X9.

- clock gating 的TE-pin 用哪个信号来控制,通常用scan\_enable 而不是test\_mode, 因为前者DFT 覆盖率更高。

- 插完gating 一定要做report, 检查插入的gating 数目,覆盖率跟效率,驴曾在这里栽过。

- 因为gating 在时钟树上,而在综合的时候时钟是ideal 的,所以到gating 的timing 要比真实情况乐观,所以通常都会在综合时对到gating 的timing path 过约,在DC 跟Genus 里都有专门的命令或变量来设置,至于过约值来源于以往经验。

- 通常在插入gating 后再做multibit merge, 这就涉及到一个gating fanout 如何计算的问题,如果记忆正确,现在DC 跟Genus 都是将一个多bit cell 当做一个fanout 来计算,那么在做完multibit merge 后clock gating 的fanout 就发生了变化,如:一个clock gating 驱动了一组8bit 的寄存器,multibit merge 前它的fanout 是8, 如果这组寄存器merge 成了一个8bit 的multibit 寄存器,那merge 后它的fanout 是1, 如此又引入了一个问题,在做完multibit merge 后是否有必要再做一次clock gating 的balance 呢?目前没有一个统一的说法,各家有各家的操作方式。

- 前几天一个朋友问到:如果enable 信号来自异步时钟域,工具是否会用其做clock gating 的控制信号?首先,这一定是设计上的一个bug, 跨时钟域的信号不做同步就是作死;其次,工具在插gating 提取enable 信号时只看逻辑关系而不会去trace 它的时钟关系,所以工具会用其来做gating 的enable 信号。

- 目前,只想到这些,欢迎补充,指正。

在形式验证中,默认所有的sequential cell 都会被当做一个key point 来处理,而clock gating 是在综合时插入的cell 在RTL 是没有key point 与其对应的,所以在形式验证时需要对gating 予以特殊处理。在LEC 中用命令"set\_flatten\_model -gated\_clock" 来处理,设置了该条命令之后,在mapping 时LEC 会将revised 侧clock gating 的逻辑反向映射到寄存器的D-pin, 如此只要将两个寄存器MAP 上即可。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/usX-BlGP5CnD5s-SbZJNpg

作者微信公众号

相关文章推荐

• 论功耗 | 如何计算toggle rate

• clock gating | 从ICG cell 在 library 中的定义说起

更多IC设计技术干货请关注IC设计技术专栏。