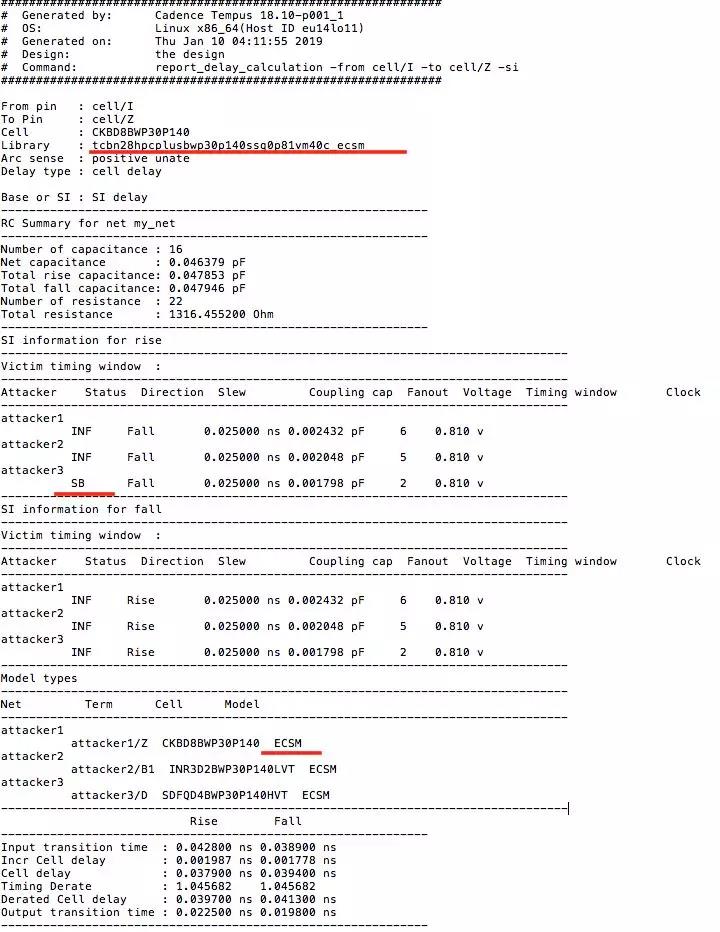

《论STA | 读懂timing report,很重要》写到如何debug 一颗cell 或一段net 的delay, 常用的办法是用report\_delay\_calculation 报这颗cell 或这段net, 会得到形式如下的report, 从该report 中可以得到:

- 表头需要特别关注的是command, 确定report 的对象及加的option;

- From/To pin: cell 的input pin 和 output pin;

- Cell: 该cell 对应的lib cell;

- Library: 该cell 来自哪个lib, 需要特别关注一下,确定用的lib 正确,避免低级错误;

- Arc sense: Arc sense 分三种positive unate, negetive unate, non unate; 输出信号同输入信号跳变方向相同的称为positive unate 如buffer 的timing arc; 输出信号同输入信号跳变方向相反的称为negetive unate 如inverter 的timing arc; 输出信号的跳变方向由另一个输入信号的值决定称为non unate 如xor 的timing arc;

- Delay type: 标示是cell delay 还是net delay;

- Base or SI: 因为加了option -si, 所以当前是SI delay;

- RC summary for net: 从这一块可以得到电容电阻个数、net 电容值、总上升电容值、总下降电容值、总电阻值。这部分信息在debug 不同工具间的correlation 时非常有用。

- SI information: 从这一块可以得到所有的attacker 信息,及每个attcker 的status, direction, slew, coupling cap, fanout, voltage, timing window, clock. 另外还可以得到attacker 的model type 要特别注意用的是什么model, 是NLDM, CCS, ECSM, 示例中是ECSM, 这一点同样在debug 不同工具间的correlation 时至关重要。

- delay information: 从这一块可以分别得到rise/fall 的输入transition, incr cell delay (由cross talk 造成的delay), cell delay, timing derate, derated cell delay, output transition.

除了report\_delay\_calculation, 顺带说三个常用的其他命令:

check\_timing

用于check SDC 的quality, 会check 以下列出的内容,可以概括为:少了什么、多了什么、冲突了什么、错了什么;SDC 可以看作是STA 的『法规』,所以对制定者要高要求,STA 工具并不能check 出SDC 中所有的问题,有一些问题必须由设计者负责,如multi-cycle 设多少,写SDC 时是否手一抖把不该设false path 的地方设了false path, 这些人为大坑是STA 工具没办法check 到的。复杂SDC 的quality 通常需要用CDC 工具去做check, 除了SDC 本身还需要check 设计中是否放了正确的同步电路等。

需要对check\_timing 报出的warning 做细致check, 把需要修的都修掉,可以忽略的都要有明确的原因。

report\_annotated\_parasitics

用于check RC的反标情况,要保证所有的real net 都可以被正确反标上,如果有未反标的net, 需要去找抽RC 的坑友确认。首先确认数据是否匹配,再确认是否做了该做的change\_name 动作,再确认除了real net 之外的其他warning, 为什么有assign 为什么有dangling net, 最好让坑友一齐处理掉,看着清爽。

report\_analysis\_coverge

check STA coverge: check 设计中有多少需要check 的东西,在当前约束下,总共有多少被check 到了,多少没有被check 到,check 到的有哪些满足了需求有哪些没有满足。这个report 很重要,如果是初次分析最好把每一项的详细信息报出来,列一张表,对没有被check 到的部分进行分类,并对每一类归因。

Tempus 中分成以下几类check , 不同工具大同小异。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/aNQmpPX2rbNDxpn74-WlRQ

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。