有时候,问题的来去也会扎堆,周二跟某几位小朋友讨论过clock min period check, 今天又跟某小猪讨论了一遍。

按照惯例从lib 说起,通常RAM 的lib 里都会定义min\_period 的timing check, 至于为什么RAM 需要check min\_period 而其他时序逻辑不需要,驴还没搞清楚,请教各位予以指导。

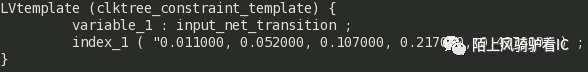

老工艺,min\_period 在RAM 的lib 里是一个定值;新工艺,min\_period 在RAM 的lib 里定义为index 是CLK pin transition 的一张一维表,在lib 里会先定义一个如下图所示的Lookup table , index\_1 里列出的值是CLK pin 的transition 值。

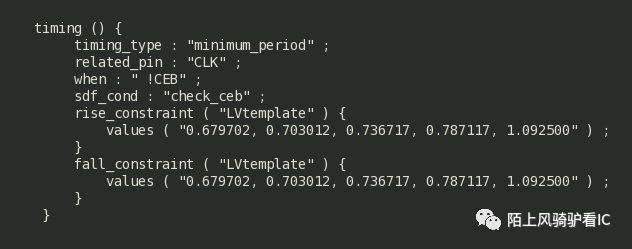

在CLK pin 上会定义如下的minimum\_period 的timing check. Values 的值即为对应transition 所要求满足的min\_period. 显然,输入transtion 越大,min\_period 要求越大。

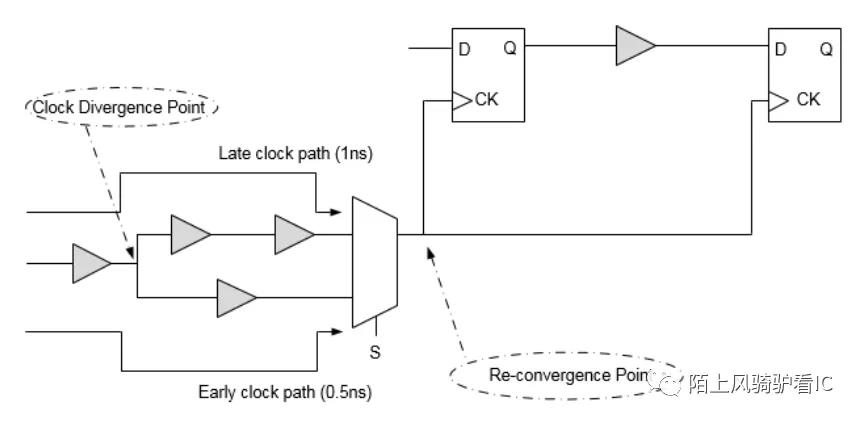

搞清楚lib 的定义之后再来对着具体电路看,老驴懒得画图,从Tempus 的user guide 里找了一张比较典型的图,假装后面的寄存器是RAM. 所谓的clock min period check, 就是先计算电路中到达RAM CLK pin 真实的clock period 值,然后跟lib 中定义的值比较。

要计算电路中到达RAM CLK pin 真实的clock period, 首先要明白都要考虑哪些因素:

- SDC 中定义的clock period: T;

- Clock lunch path 跟Capture path 上的derate 值;

- Clock uncertainty.

- Clock path 上的crosstalk.

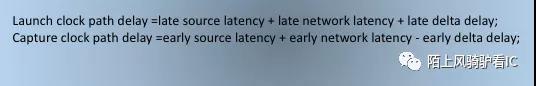

对于示例电路,Clock 在到达RAM 的CLK pin 之前就有了分叉,按照惯例, 此处从clock root 点到clock 分叉点的delay 称为source latency; 从clock 分叉点到RAM CLK pin 的delay 称为network latency, 那么在考虑串扰的情况下可得:

如果设置了OCV 或读入了AOCV/ SOCV 文件,并且enable 了对应的计算,工具在计算latency 的时候会自动将derate 值计算在内,对于source latency 需要减去CPPR. 因为Clock period 计算的是不同沿clock 的delay 所以CPPR 中只减掉Derate 部分,cross talk 引起的delta delay 不会被减掉。故,clock period 的计算为:

在memory 选型的时候,clock min period 是一个重要指标,需要根据电路实际的工作频率, clock 的uncertainty, Crosstalk, 工艺的Variation 来选定。

在STA 阶段如果有clock min period 的violation, 可以做:

- check 是否有clock 的分叉点,如果有是否可以尽量把分叉后的path 做短;

- 修clock transition, 更小的transition 对应的clock min period 要求更小。

- check clock path 上是否有crosstalk, 如果有,修干净。

如果以上事情都做好了,依然meet 不了clock min period 的需求,说明memory 选型时考虑不周全,可以尝试换low VT 的memory , 再不行就需要推倒重来。

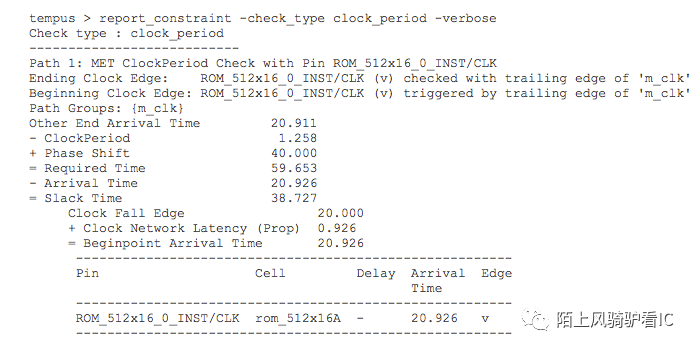

再贴一个Tempus report 的示例:

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/4oggZ07jG9MEFXen83qA2Q

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。