题记:记得曾在一个电影里看到,德军二战后在月球建有基地,若干年后逮到一地球人,地球人的一部手机的算力超过了德军月球基地一屋子的机器。这一『科幻』很现实,集成电路自诞生之日便依照着摩尔定律,管子的尺寸越来越小,集成度越来越高,从而使得单芯片上集成的功能越发强大,算力也是一『日』千里<被新工艺搞得精疲力竭的硅友应能深刻体会到此处『日』的深意>。

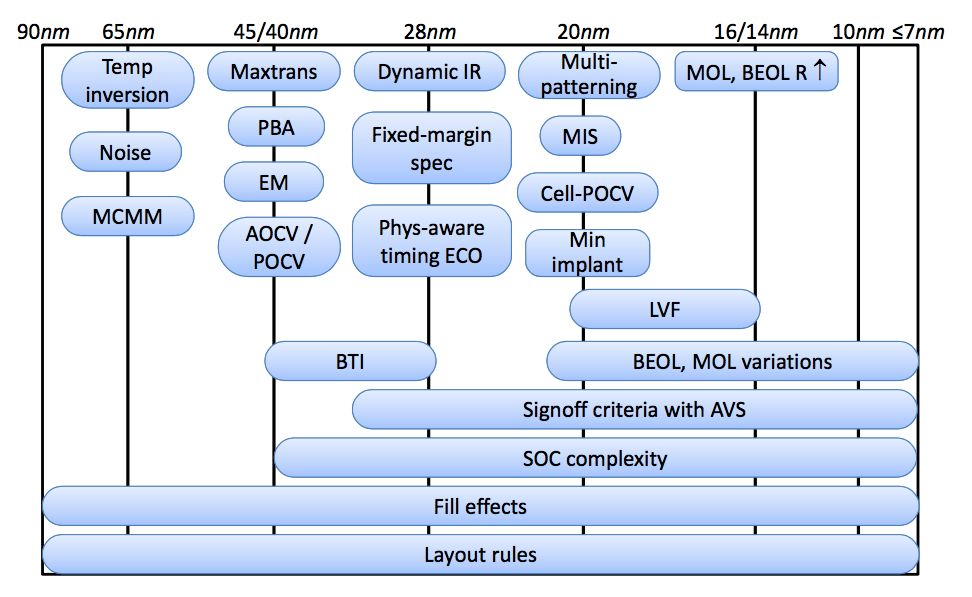

一切都是发展的需要,工艺更新给整个半导体行业带来了巨大的挑战,从生产设备到EDA到芯片设计实现无不在被泽科技之光时气喘吁吁。下图是从DAC15 Andrew B. Kahng讲synthesis 的slide上抠的图,这幅图直观地呈现了从65nm到16/14nm,物理实现尤其是 STA 需要考虑的由工艺进步引入的因素。

在芯片设计实现这一截,P&R工程师对工艺带来的挑战感受会更直接,综合跟 STA 跟 DFT 也都有新的点跟方法学的更新,但大都被 EDA 工具严实地包了起来,就拿综合来说,相对于传统综合而言最大的更新莫过于physical aware synthesis,但对于大部分综合工程师而言,这一点似乎只是一件水到渠成的事儿,你用或不用,flow 就在那里,不吼不叫。驴今天就自己浅显的认知,就这一点做一个简单的论诉。

为什么要做physical aware synthesis?

最根本的目的就是减少前后端的迭代次数,前后端迭代次数多的根本原因是 correlation 差,而 correlation 需要从timing 和 congestion 两个方面来看:

Timing

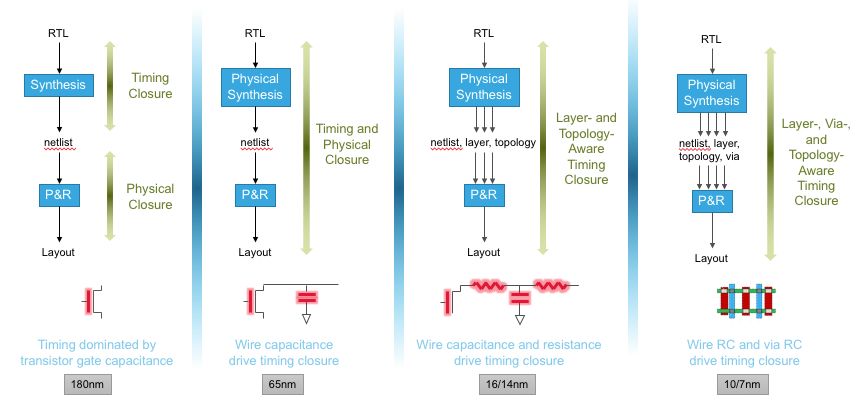

综合优化的对象是 timing path,而 timing path delay = net delay + cell delay,90nm之前由cell delay 主导,而进入65nm net delay所占比例日渐增加,进入40之后几乎跟cell delay平分秋色,所以从40 开始physical aware synthesis 被硅农熟知,因为physical aware synthesis在优化过程中可以看到更精确的net delay。

为什么logical synthesis 不能精确计算net delay?

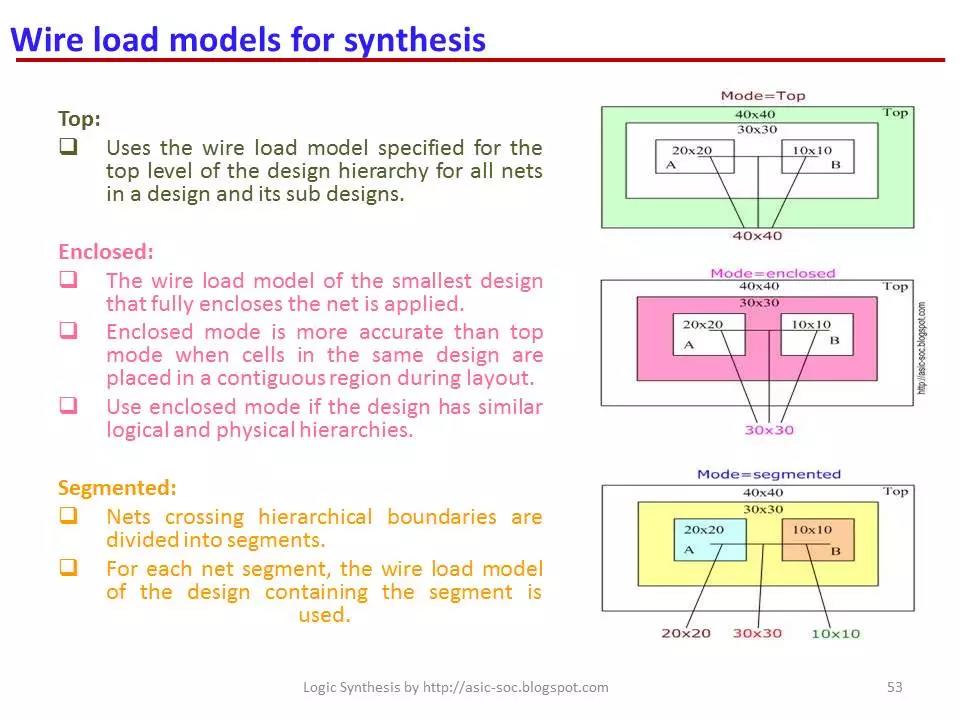

这就要回看一下传统综合是如何估算 net delay 的。传统综合俗称logic synthesis,它根据WLM 来估算net delay。WLM (wire load model) 由foundry 提供,WLM通常包括面积系数、电容系数和单位长度的电阻系数,以及一个用于估计net 长度的表格,表的index是 fanout,直白地说就是将net 的长度模拟成fanout 的函数。

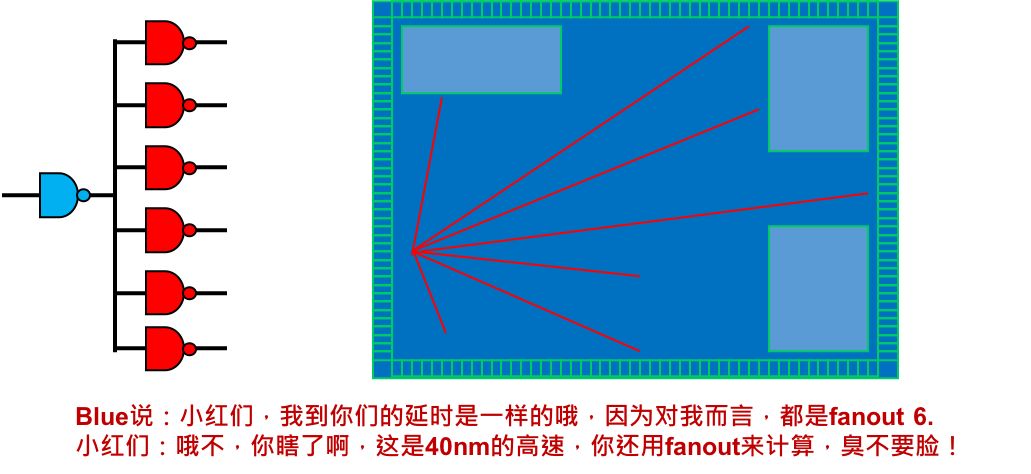

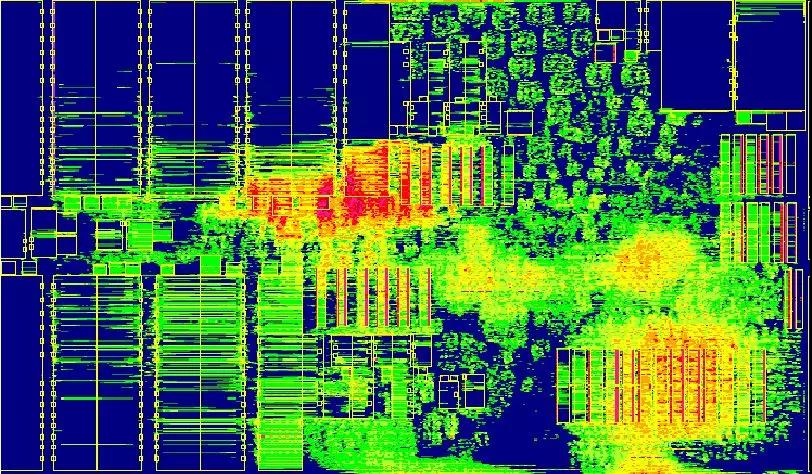

看下图:按照WLM 来计算,blue 到red 的所有net 长度都一样,net delay也一样,而实际上 net 行走的姿势五花八门,根本就不可能一样,缺点显而易见。另一个缺陷是WLM 的单位电容电阻是一个常值,无法模拟不同layer RC 值的差异,而工艺进入16nm 之后,必须要考虑 layer aware 的 net delay,进入7nm 之后除了layer 还要考虑VIA对net delay的影响,为什么要考虑VIA? 因为VIA delay占的比重已不容忽视。

在40甚至28,依然有人在用传统的方式来做综合,做法简单粗暴加时钟周期30%甚至更多的过约,这样做是可以cover net delay,但是实在是过犹不及。据统计在一颗芯片里80%以上的线都是短线,为了cover那不到20%的线,付出的代价就是更大的面积及更多的功耗,当然如果你不在乎,那就无所谓了,毕竟任性是你们土豪的特性之一!

Physical aware synthesis 如何更精确的计算net delay?

要精确计算net delay必须要知道net的行走姿势,而要知道net 的行走姿势必需要知道:它来自哪里?要去向何方?这就需要知道cell 的位置,cell 位置确定了之后,综合工具会做global 绕线,根据global 绕线的结果来估算net delay。cell 位置由placement 确定,所以如今综合工具都集成了 placement 引擎,这也是做 physical aware synthesis 的关键所在。目前大概有两种做place的方式:

- 做完优化跟mapping之后,再做place,操作对象是std cell。

- 在elaborate 之后优化之初就做place, 即所谓的 early physical, 早期阶段针对module 做palce,mapping之后再以std cell为对象做place。

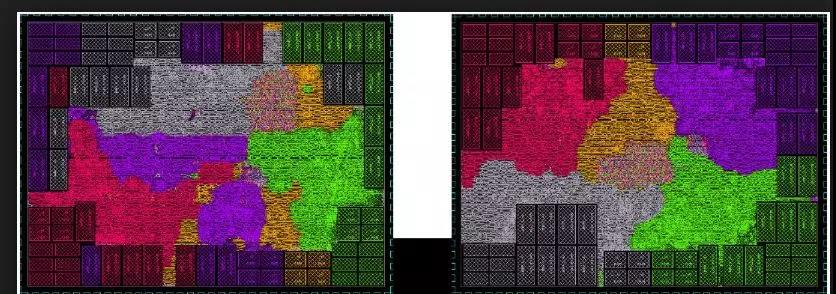

下图是谷歌上随便找的一张图,只为显示什么是module place, 从Layout 上看每一个颜色对应一个 module, 对应于RTL中的 hierarchical, 所以 module place 的QA 对 PPA 会有很大影响。综合工具基本都按 translation + optimization + mapping 三大步来走, 所有结构的选择跟大部分优化的动作都在 optimization 这一步完成,如果可以在 optimization 时就知道 module 的位置信息,优化会更有的放矢会更能『精准打击』,所以 Early physical 十分必要。现在看到的趋势是把更多的物理信息拿到前端来,越早考虑物理信息得到的结果会越好。

**结论:**physial aware synthesis根据真实的物理信息,用跟 P&R 一致的 place 引擎跟 global route 引擎,可以精确估算 net delay,并且是layer 跟VIA aware的。通常physical aware synthesis 只需过约时钟周期5%\~10%即可,用于conver legalization跟detail route 的影响。

Congestion

同样由于工艺进步,集成度提高,单位面积上要走的线骤增,所以 congestion 成了一个从RTL 设计就要开始关注的问题,否则到了绕线的时候绕不通,前面所做的一切都成了无用功。很显然,logical 综合是无法考虑 congestion 的,要在综合阶段做congestion 优化必须要 physical aware synthesis.

其实不论PPA还是congestion主导决定权都在进实现之前,架构算法设计,才是真正决定一切的『权贵』,所以才说实现是个没有灵魂的工种,只要按着 设计/EDA/foundry 定的规则往下走就可以,切忌的就是『发挥』。

于congestion 综合工具能做的基本只有两件事儿:选结构跟推cell。至于选结构,一个用烂的例子就是把一个大MUX 拆成多级MUX 用于解congestion。推cell 这一点完全依赖于EDA 工具,如果你不知道如何做,那就找AE要变量或 option 让工具在综合做place 时将 congestion 严重区域的cell 推散。除此之外,还有一点可以人为干预,禁用或让工具少用size 小的复杂cell 比如x1的 AOI/OAI。

要特别说明一点,在16之后,layer 的影响特别大,所以综合用的 DEF 一定要有special net 部分,也就是你的power plan,让工具在综合时清楚地知道哪些layer 的绕线资源已经被占用。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/wX1rPgGrn4IwHfXc-f\_e9Q

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。