之前写过《 论STA | clock min period check 》今天再撸一下min pulse width.

提纲:

什么是min pulse width?

如何check min pulse width?

如何计算min pulse width 的CPPR?

如何fix min pulse width?

什么是min pulse width?

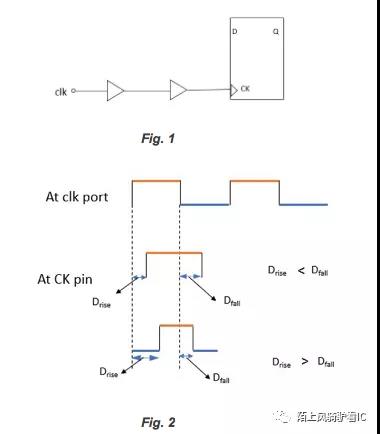

min pulse width 是对信号高电平或低电平脉冲最小宽度的衡量,通常都只针对clock path 做min pulse width 检查。min pulse width 的计算公式为:

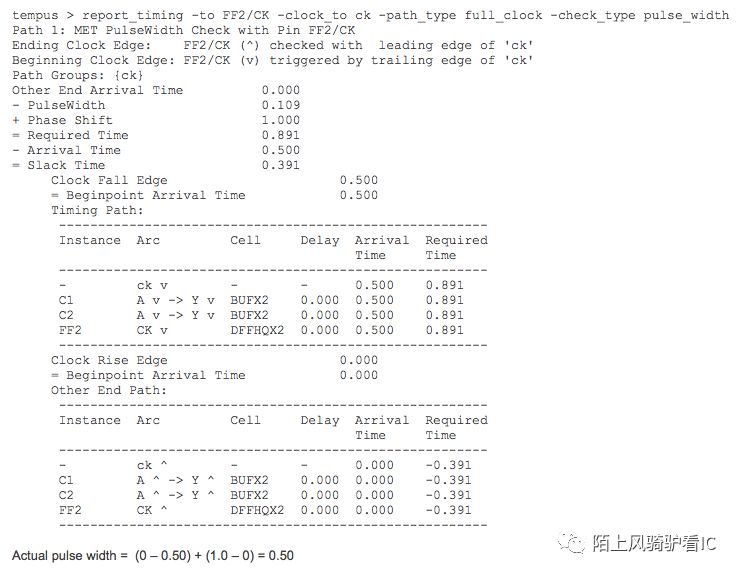

- 高电平min pulse width = (时钟源头原始下降沿时间 + 下降沿到达时序逻辑clock pin 最早时间) - (时钟源头原始上升沿时间 + 上升沿到达时序逻辑clock pin 最晚时间) + CPPR - uncertainty = ( original\_fall + fall\_early arrival time ) - ( original\_rise + rise\_late arrival time ) + CPPR - uncertainty.

- 低电平min pulse width = (时钟周期 + 下一上升沿到达时序逻辑clock pin 最早时间) - (时钟源头原始下降沿时间 + 下降沿到达时序逻辑clock pin 最晚时间) + CPPR - uncertainty = ( period + rise\_earlyarrival time ) - ( original\_fall + fall\_late arrival time ) + CPPR - uncertainty.

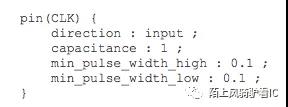

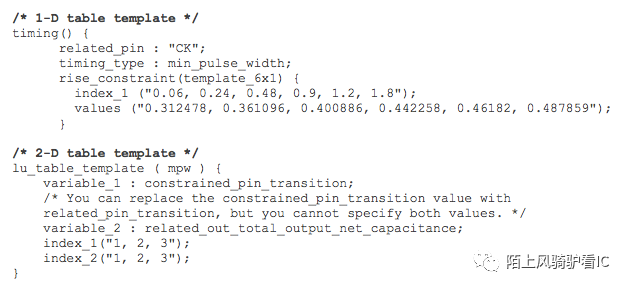

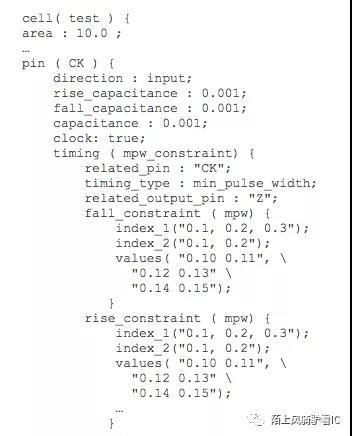

min pulse width 是在library 中预定义的attribute, 计算得到的值跟library 中的值去比较以判定当钱值是否满足要求。min pulse width 在库中可以是一个简单的值,可以是以input transition 为index 的一张一维表,也可以是以input transition 跟output load 为index 的一张二维表。

如何check min pulse width?

在Innovus 跟Tempus 中,只要有如下信息就可以做min pulse width 检查:

- 做了CTS.

- library 中相应clock pin 上定义了min pulse width 属性,或用命令set\_min\_pulse\_width 设了约束。

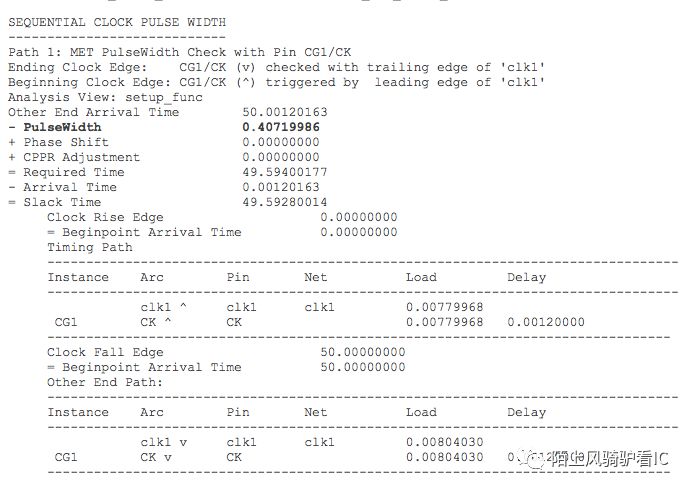

用命令report\_min\_pulse\_width 可以报出相应check, 可用上述公式对应计算。

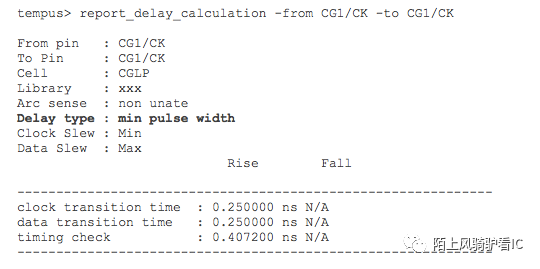

当然也可用命令report\_delay\_calculation 报告:

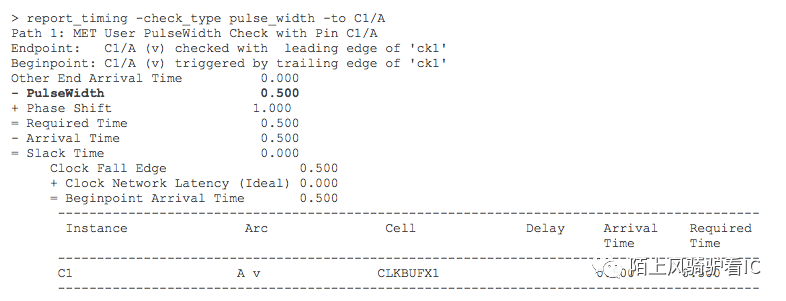

也可以用report\_timing -check\_type pulse\_width 报,通常,在library 中只有clock pin 上会定义min pulse width 属性,其他cell 或其他 pin 不会有相关属性定义,Innovus 跟Tempus 也只对时钟信号和时钟网络做min pulse width 检查,对于时钟网络上的非时序逻辑单元,可以用命令 set\_min\_path\_width 做约束。

Innovus 跟Tempus 默认是不对data/async pin 做min pulse width check 的,如果想要check data/async pin 的min pulse width 可以通过定义dummy clock 来实现。

如果时序单元clock pin 有多个clock, report\_min\_pulse\_width 只会报最critical 的情况,如果要得到其他clock 的 min pulse width 的信息,可以用命令 " report\_timing -check\_type pulse\_width -to \<pin/port> -clock\_to -path\_type full\_clock" 报出相应的timing 信息来计算得到。

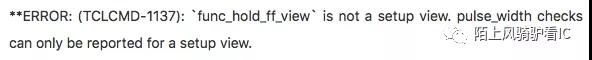

实际上,min pulse width 可以理解为对clock 自己做的 "setup check", launch clock path 用late 值,capture clock path 用early 值,再将uncertainty 跟CPPR 考虑在内。在Innovus 跟Tempus 中如果在hold view 报min pulse width check 工具会报错:

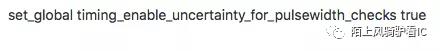

Innovus 跟Tempus 在做min pulse width check 时默认不将uncertainty 计算在内,可以用如下变量控制,因为clock uncertainty 通常用于模拟clock jitter 跟IR-drop 等因素对delay 的影响,而这些因素对min pulse width 同样也有影响,所以不能为了滤掉min pulse width violation 将uncertainty 关掉。

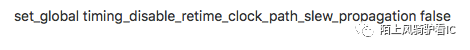

可以通过设置如下变量,做PBA min pulse width check:

如何计算min pulse width 的CPPR?

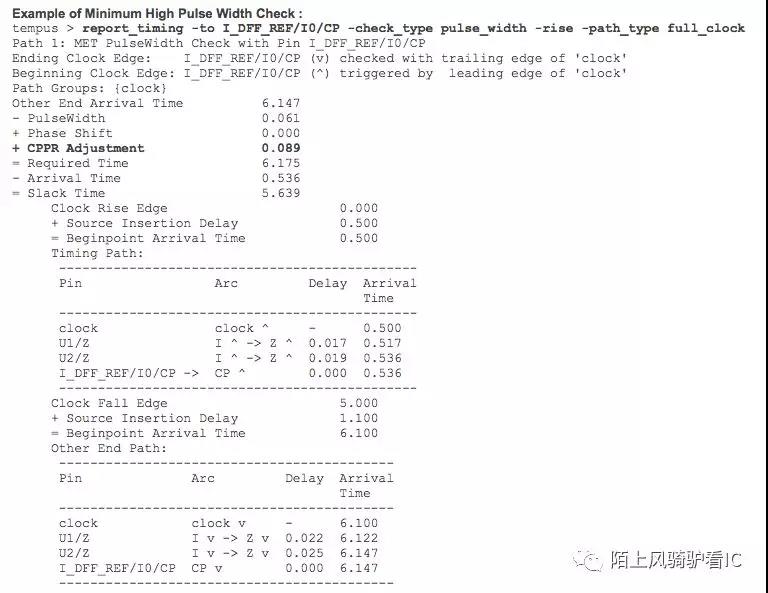

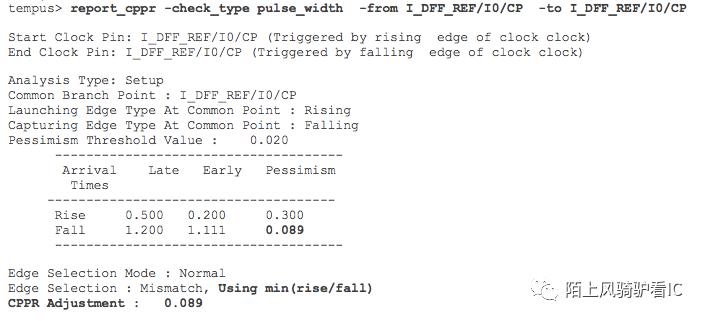

min pulse width check 永远都是『异沿』 check, 对于『异沿』check 的CPPR 在STA 中有两种做法,一种是严格做法按0 处理;另一种是分别计算时钟上升沿跟下降沿的CPPR 然后取两者中的最小值做最终的CPPR 值。如下例即是选择两者中的最小值。

可以用report\_cppr 来报出CPPR 值的计算:

如何fix min pulse width?

min pulse width 是STA 的hard rule, 有违规必须要修掉,否则可能导致时序逻辑功能失效。因为PMOS 管跟NMOS 管的充放电时间有偏差,导致同样大小的管子上升跳变跟下降跳变的延时有偏差,从而导致时钟信号传过时钟网络后占空比发生扭曲。通常,在时钟网络上可用的cell 如CK-buffer, CK-inverter 会尽量做得上升下降时间对称,但是完全对称也不现实,所以用CK-inverter 做tree 对clock 上升下降的对称性更有帮助。

防患于未然,在做CTS 时:

- Use faster cells wherever possible.

- Set aggressive clock transition targets.

- Verify the clock tree structure pre-CTS and make sure that the placement of the clock leaf cells is as expected. It is also important to check the placement of the combinational cells in the clock tree.

- In case high-speed functional clocks get multiplexed with low-speed test clocks, make sure that the latency of the high-speed clocks does not suffer.

- Try to build your clock trees (at least the ones for the fast clocks that are most sensitive for pulse width distortion) with inverters only.

- In the case of combinatorial cells in the clock tree. Often, there are symmetrical versions of certain cells available in the libraries. Use these cells whenever possible.

- use LVT cells which has low variation.

在CTS 之后,进STA 之后,通常有如下手段fix min pulse width:

- 修crosstalk 引起的delta delay;

- 修transition;

- 换成variation 最小的fastest VT cell.

- 将CK-buffer 换成CK-inverter;

- 如果以上方式还是无法修干净,看是否可以将有violation cell 的clock 接到离root 更近的地方;

- 如果还不可以,可以用非对称cell 如normal buffer 来修只对high-pulse width或low-pulse witdh 一个方向有要求的点。

- 如果再不行,那只能从头再来了。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/DTSMr6o\_IFnIJWeEt9XsdA

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。