ILM = interface logic model, 是用来描述设计『接口逻辑』的一种『模型』,一个完整的ILM 包括:netlist, DEF, SPEF, SDC; 所有的这些文件都只描述跟输入输出接口相关的逻辑,设计中与接口不相关的逻辑,一概不写入ILM.

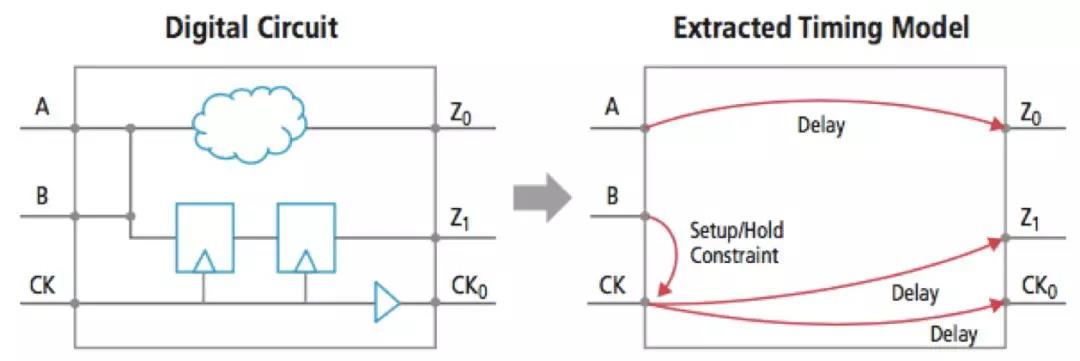

ILM 模型用于综合、PR, STA 的hierarichical flow, 相对于ETM 模型更精确,ETM 只包含接口的timing arc 信息,无法用于精确的cross talk 分析。而ILM 模型包含所有接口相关的逻辑,除此之外 XILM 模型还包含所有接口相关的耦合电容,可以用于精确的cross talk 分析。

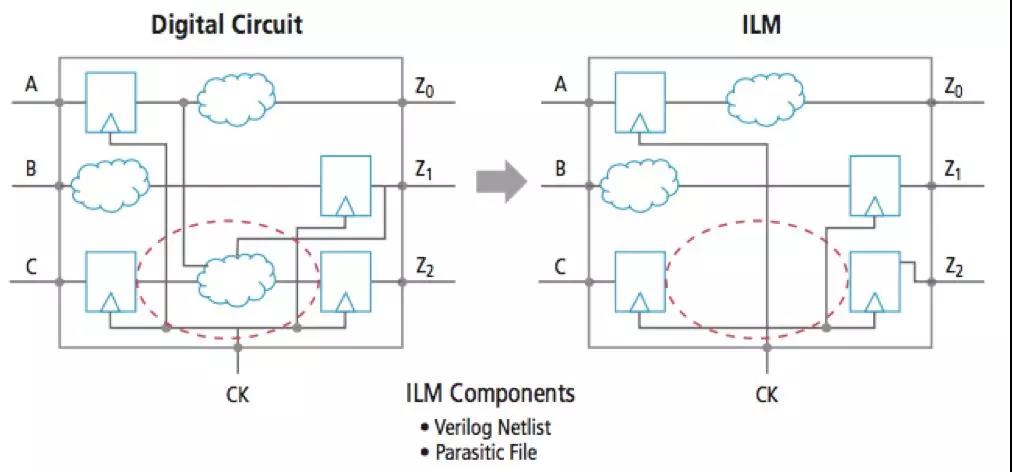

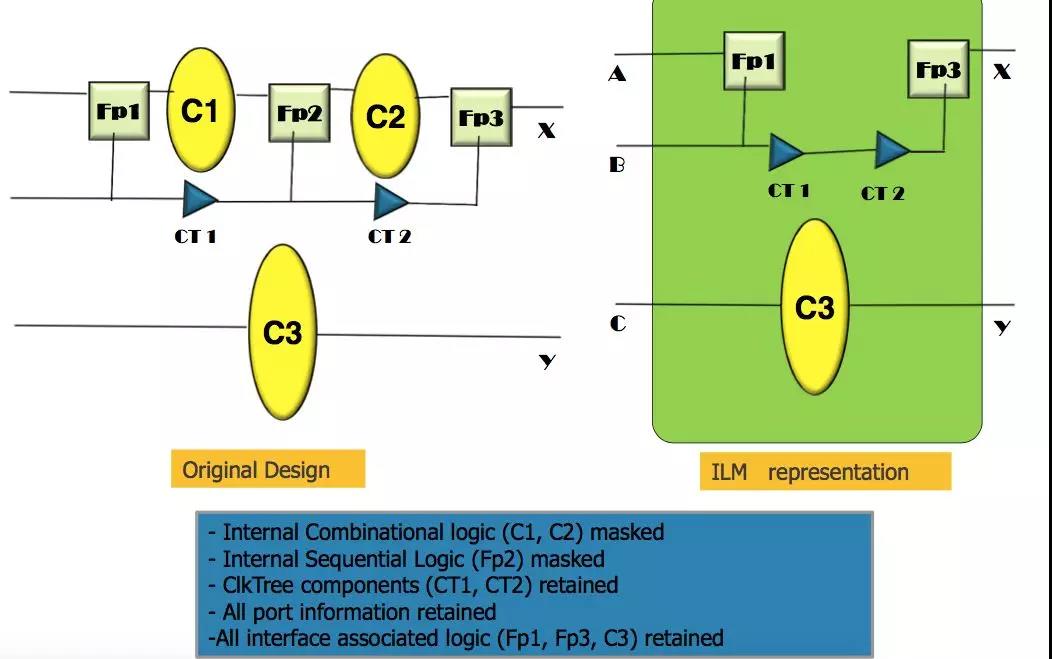

下图是一个ILM 模型抽取示例,看图说话,ILM 模型其实就是将所有跟接口相关的逻辑留下,且将所有跟接不直接口相关的逻辑抛弃,所有接口相关的逻辑信息、时序信息、物理信息、寄生参数信息都可以被完整保留。

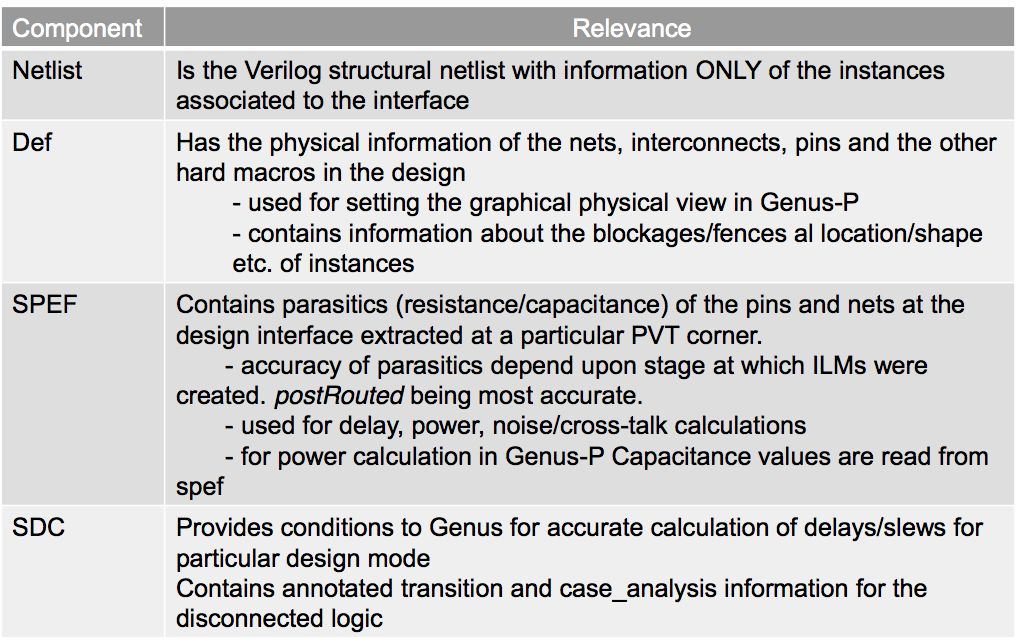

一个完整的ILM 模型应该包括netlist, SPEF, SDC, DEF, 分别用于描述接口的逻辑信息、寄生参数信息、时序信息、物理信息。

ILM模型可以在设计实现的任何一个已map 阶段提取,如:可以在Genus syn\_map 之后提取,也可以在PrePlace, PreCts, PostCts, PostRoute 之后的任何一个阶段提取。不同阶段提取的ILM 模型的精度不同,适用场景不同。

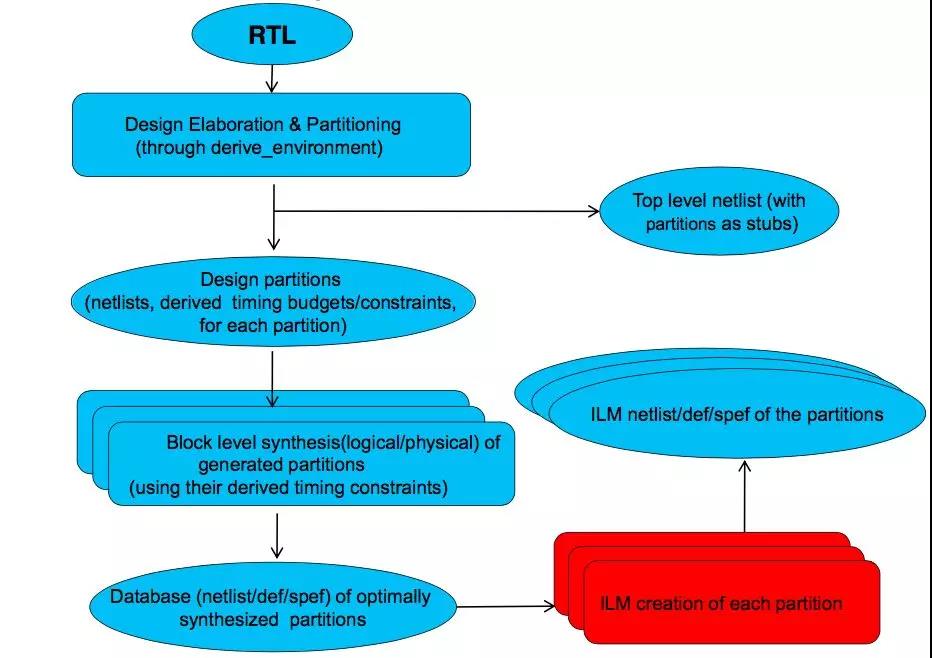

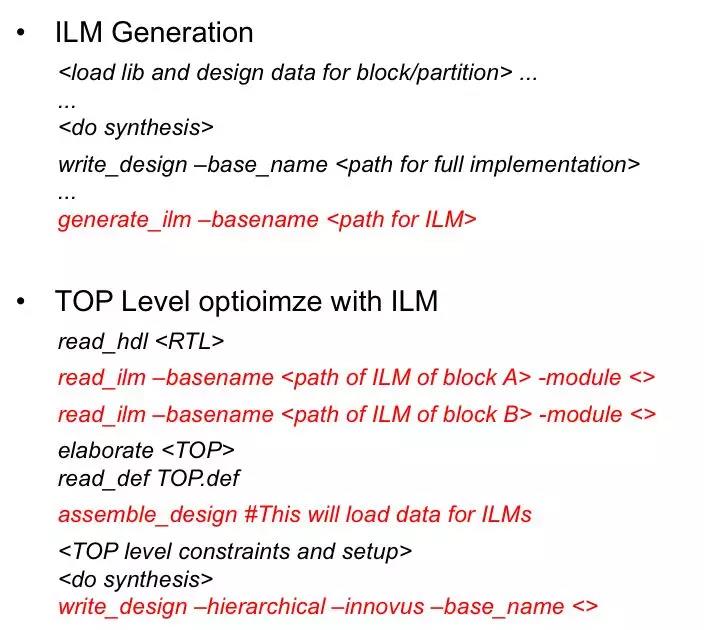

Genus 用ILM 模型做hierarchical 综合的流程非常简单明了,如下图所示,如果当前没有sub module 的ILM 模型,可以先用Genus 对sub module 进行综合,并用命令 "generate\_ilm" 生产一个ilm 模型;然后再综合上一层设计,在综合父级设计时关键的命令只有两个 " read\_ilm " 跟 " assemble\_design "。

参考文献:

Genus\_ILM\_RAK.pdf

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/ZSK9meMilc4LcUuueDTdUA

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。