PANIC

原版见OSDI2020。

这个专题主要对基于FPGA的智能网卡技术进行介绍,上篇介绍了NanoPU,这次介绍“PANIC: A High-Performance Programmable NIC for Multi-tenant Networks”。高山阅读留存点滴。

网络线速处理与CPU产生和消耗数据的速率之间的差距正迅速扩大。可编程(“智能”)NIC可以帮助克服这个问题。有许多不同类型的功能可以卸载到可编程NIC上。这些功能卸载加速了网络堆栈所有不同层的计算,可以减少通用CPU的负载,减少延迟,并提高吞吐量。

许多不同的云和数据中心应用已被证明受益于将计算卸载到可编程NIC上,但是,没有一个“银弹”卸载方式可以在所有情况下提高性能。相反,不同的应用程序将指定自己的卸载链,然后运营商将这些链与基础设施相关的卸载合并,并在其可编程NIC上运行它们。为了实现这一目标,提出了一种新的可扩展的高性能可编程多租户网络网卡PANIC,它支持多种不同类型的卸载,并将它们组合成独立的卸载功能链。

为了使云运营商能够将NIC卸载功能链作为服务提供给租户,可编程NIC必须支持:1)卸载种类:功能卸载(如加密)最适合硬件实现,为应用程序中的RPC提供低延迟旁路的卸载更适合嵌入式核心;2)卸载功能链:为了最大限度地减少冗余功能上浪费的芯片面积,NIC应便于根据需要将独立的硬件卸载单元组成一个链,在租户之间共享通常需要的卸载;3)多租户隔离:租户应该不能消耗超过其分配的共享卸载;4)变化的性能卸载:有些有用的卸载不能保证以线速处理,也有一些重要的卸载以低延迟和线速运行。

存在许多不同的可编程NIC,但是,目前没有一个可编程NIC能够提供上述所有属性。现有的NIC设计可分为以下几类,每类都有关键限制:

•卸载流水线NIC。在流水线中部署多个功能卸载,以使数据包能够由一系列功能处理。功能链可以在这些NIC中修改,但是需要大量的时间和开发人员的努力来进行FPGA合成,并且慢的卸载会导致数据包丢失或头(HOL)阻塞。

•Manycore NIC。跨多个嵌入式CPU内核对数据包进行负载平衡,然后CPU内核根据不同的卸载需要控制数据包的处理。这些设计都存在性能问题,因为嵌入式CPU内核会增加数十微秒的额外延迟。此外,现有的多核心NIC都没有提供隔离竞争租户的性能机制。此外,如果工作集不适合内核的缓存,许多内核NIC的性能可能会显著降低。

•RMT NIC。在NIC可重构匹配+操作(RMT)流水线上使用,以实现NIC卸载。RMT流水线支持的卸载类型是有限的,因为每个流水线级必须能够在每个时钟周期处理一个新的数据包。

PANIC克服了现有网卡设计的主要局限性。PANIC从最近关于可重构(RMT)交换机的工作中获得了灵感。PANIC的设计利用了三个关键原则:

1)卸载应该是独立的。潜在有用的卸载集是多样的和巨大的,跨越了网络堆栈的所有层。因此,可编程NIC应该能够支持硬件IP核和嵌入式CPU作为卸载。

2)数据包调度、缓冲和负载平衡应集中化,以获得最佳性能和效率。因为分散决策和每次卸载队列可能会导致较差的尾部响应延迟,以及由于负载不平衡而导致较差的缓冲区利用率。

3)由于中小型无阻塞结构的成本相对于NIC整体而言较小,因此卸载应该由无阻塞/低超额订阅交换结构连接,以实现卸载的灵活链接。

遵循这些设计原则,PANIC做出了三个关键贡献:1)一种新的可编程NIC设计,其中不同的功能卸载连接到一个非阻塞交换结构,功能链由可编程RMT流水线编排;2)一种新的混合推拉调度器和负载均衡器,具有优先级感知丢包功能,3)对网卡上可编程交换和调度的成本进行分析,发现它们相对于网卡整体而言成本较低。

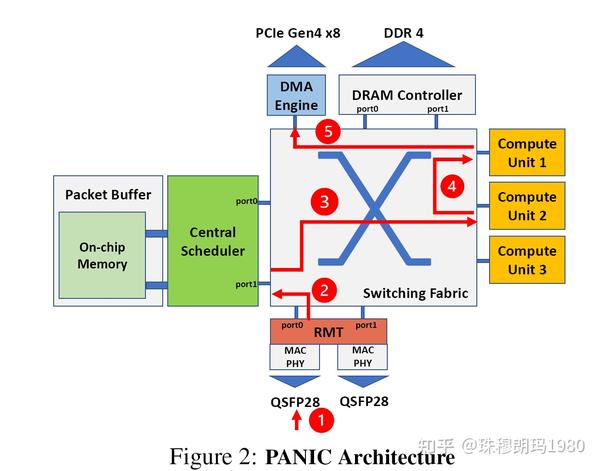

PANIC NIC有四个组件:1)RMT交换流水线,2)交换结构,3)中央调度器,4)独立的计算单元。RMT流水线提供可编程的功能链编排。一个高性能的互连,使可编程功能链线速处理。中央调度器提供隔离、缓冲区管理和负载平衡。独立的计算单元可以是硬件加速器或嵌入式内核,不需要以线速率运行。

为了评估PANIC的可行性,进行了ASIC分析和FPGA原型实验。FPGA原型能够以100Gbps的速率执行动态卸载链,并在各种链配置下实现纳秒级(<0.8ms)的数据包调度和负载均衡。经验表明,与最先进的基于流水线的设计相比,PANIC可以更好地处理多租户隔离和线速功能卸载。在小型试验台上的端到端实验表明,PANIC可以在100Gbps下实现动态带宽分配和优先分组调度。总的来说,包括8*8的PANIC组件只消耗了Xilinx UltraScale Plus FPGA上可用的总逻辑区域(LUT)的11.27%。

智能网卡专题:

FPGA-inline加速器SmartNIC(1):NanoPU

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/359361616

更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。