FPGA OS

原版见OSDI 2020。

FPGA开发有没有基础库,“Do OS abstractions make sense on FPGAs?”部分部解答了这个问题,首次提出FPGA抽象技术FPGA OS。

FPGA编程问题

现场可编程门阵列(FPGA)现在是数据中心和云提供商的标准配置,尽管(由于其在嵌入式系统和原型设计方面的传统)仍然难以编程、部署和部署,但与ASIC或GPU相比,现场可编程门阵列(FPGA)在许多应用程序中以更低的功耗提供了更大的灵活性,安全管理。因此,随着许多关于使FPGA更易于编程的研究,最近相当多的工作应用了从操作系统设计和实现到以FPGA为中心的计算机的资源分配、共享、隔离和管理的思想。

到目前为止,这些工作是零碎的,集中在功能的一个特定方面,例如Feniks以FPGA访问外设为目标,Optimus通过地址转换等提供对主机虚拟内存的访问。这些都比现有技术有了实质性的增量改进。

同时,好的操作系统设计如此具有挑战性的是内核中所有功能之间的紧密交互。不支持多个应用程序(多租户)或它们之间的强隔离的虚拟内存的使用是有限的。在不提供虚拟寻址的情况下虚拟化硬件设备,并创建一个抽象硬件的公共执行环境,使得大部分问题没有得到解决。不能利用动态重新配置芯片部件的能力的FPGA调度器具有有限的保存期,等等。

FPGA操作系统

传统的操作系统概念(进程、虚拟内存等)在多大程度上可以(或应该)有效地转换为FPGA?需要采用一种全面、整体的方法,并考虑完整的功能,而不是坚持操作系统的特定方面或只支持有限的FPGA功能。

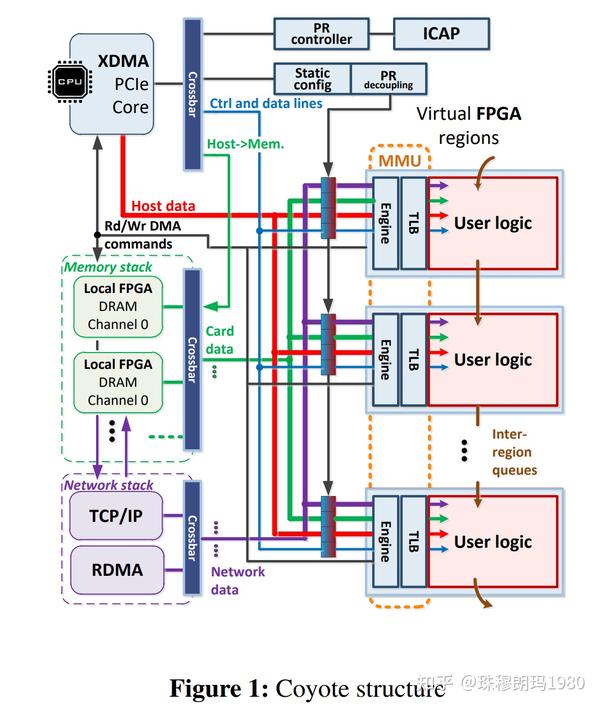

Coyote提出在一个统一的运行环境中为基于FPGA的应用程序组合了一组连贯的操作系统抽象。与微内核一样,Coyote提供了一组核心的基本功能,其他服务可以基于这些功能:统一的执行环境和可移植性层、虚拟内存、物理内存管理、通信、时空调度、网络以及用于用户逻辑的软件进程或任务的模拟。它以最小的开销(不到商品FPGA的15%)实现了这一点。

Coyote特点:

1.对于一系列操作系统抽象,在其与其他操作系统交互的上下文中,对每个操作系统如何映射到FPGA进行关键评估;

2. Coyote中完整集成的一种实现,Coyote是一种用于混合计算服务器的可配置FPGA“OS”。

Coyote架构

Coyote的目标是混合系统,通过外围总线(如PCIe、CXL、CCIX或OpenCAPI)将传统CPU与FPGA结合起来,或者使用本机一致性协议(如Intel HARP或ETH Enzian)。Coyote现在运行在带有Xilinx VCU118、Alveo U250和Alveo U280卡的PC上。避免任何可能妨碍使用现代FPGA功能的设计决策,如多个区域的动态部分重新配置,或有用的“硬”片上功能。

这就自然而然地将任何设计划分为在FPGA上运行的“硬件”组件和在主机CPU上运行的作为OS和支持库一部分的软件组件。

此外,FPGA的动态重新配置将硬件组件进一步划分为在引导时配置的“静态区域”和包含子区域(vFPGA)的“动态区域”,每个子区域可以动态地配置。这种分解存在于所有FPGA数据中心部署中(通常以简化形式)。在区域内和区域之间,硬件组件通过标准互连(如AXI)进行交互。

(1)静态区域

FPGA静态区域包含重新配置动态区域和与CPU操作系统通信所需的功能。但是,它的内容不应该总是固定的。空间(芯片面积、逻辑块、连线等)仍然是FPGA上的稀缺资源,与CPU时间、虚拟内存等操作系统资源不同,很难通过虚拟化使其具有“弹性”。此外,不同型号的FPGA显示出非常不同的折衷。从中期来看,让一些静态区域组件(例如,TCP/IP堆栈)成为可选组件是很重要的,这样如果空间可以更好地用于用户逻辑,则就可以省略它们。

在Coyote中,静态区域总是包含功能逻辑,用于部分重新配置动态区域、与主机通信(xDMA复制引擎)以及将动态区域划分为一组虚拟FPGA(“vFPGA”),每个虚拟FPGA都具有映射到主机CPU的物理地址空间的接口。

静态区域还可以包含在vFPGA中运行的所有应用程序之间共享的可选逻辑,最基本的是内存控制器(用于直接连接到FPGA的RAM)和网络(目前是TCP和RDMA)。

(2)动态区域

动态区域是FPGA资源时分复用的基本机制。FPGA允许在任何时候独立地重新配置该区域的选择性部分。大多数部署的系统(例如F1和Intel的HARP)将此区域专用于单个应用程序,很少对其重新编程(例如,当主机上的关联虚拟机启动时)。

Coyote像其他最近的系统,提供灵活的空间和时间复用。将动态区域划分为独立的vFPGA。它们的编号被连接到静态区域,这允许多个应用程序同时运行,并且可以进行输入和输出切换。

Coyote的一个新特性是,每个vFPGA被进一步划分为用户逻辑和封装器Wrapper。前者是一个完全由Coyote用户合成并经过系统验证的比特流。这使得编程模型具有极大的灵活性:Coyote应用程序可以用HLS、Verilog、VHDL、OpenCL或这些语言或其他语言的组合来编写。

封装器Wrapper是Coyote的一部分,两个沙盒都包含用户逻辑,并为系统的其余部分提供标准接口(在FPGA中,分区引脚由重新配置工具插入,锁定网络结构中的所有边界接口信号)。这会带来芯片区域使用成本,但好处是Coyote将FPGA应用程序的“可移植层”提升到了框架级别:为Coyote编写的应用程序可以在给定足够资源的情况下综合,以便在任何Coyote FPGA上运行。相比之下,在目前的原生FPGA开发中,代码很少在设备模型之间可移植。

对比

在Coyote的结构和OS的微内核模型之间进行类比,它由内核(静态区域)、服务(可选静态组件)、系统库(动态包装器)和应用程序代码(用户逻辑)组成。然而,这也不是完全正确。例如,动态封装器Wrapper是可信计算基础(TCB)的一部分,而微内核中的系统库则不是。

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/360794858更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。