FPGACloud

原版见FPL 2019。

网络连接的FPGA如何调用,“System architecture for network attached FPGAs in the Cloud using partial reconfiguration”提出FPGA抽象技术FPGACloud。高山留存阅读点滴。

长期以来,计算基础设施增长一直受摩尔定律和以CPU为中心的同构平台的应用的推动,这些传统系统由于芯片上的极端功率密度而受到影响。因此,现代超级计算机和云数据中心采用了一种新的方法,开发高性能、低功耗的异构设备。现场可编程门阵列FPGA能耗效率和低延迟有可能极大地提高计算节点的能耗密度,同时实现更快地交付。因此,越来越多的FPGA正在进入DC,在DC中它们被用作加速器,以提高单个服务器节点的计算能力和整体能效。

两种云架构最近提出,通过使FPGA能够在DC规模上直接通信,将FPGA资源转变为独立的云计算机节点。

在微软Catapult中,FPGA被放置为服务器的网络接口控制器NIC和以太网交换机之间的主机网络侧“bump-in-wire”,而IBM的FPGACloud超规模基础设施更进一步,它将FPGA加速器从服务器中分离出来,并将FPGA转变为独立的计算资源。这种网络连接的FPGA可以大规模部署,并且独立于DC中CPU服务器的数量。网络连接允许它们彼此无缝连接,也可以与多个CPU无缝连接。由此产生的分散异构计算基础设施能够动态地适应任何工作负载的规模。

与此同时,从业务分析到科学模拟的大规模应用程序已经开始使用分布式框架(如Hadoop、Spark和Tensorflow)进行扩展,这些框架将消耗大量的FPGA,必须以高效灵活的方式提供和管理这些FPGA。

FPGACloud采用了一种在DC基础设施中大规模获取、分发、配置和操作独立网络连接的FPGA体系结构。通过研究DC提供者和FPGA用户所表达的约束,来定义构建这种可伸缩部署的主要需求列表。基于这些分析,提出了三层体系结构,涵盖了从实现用户应用程序的核心到DC管理的各个层次。

高级体系结构

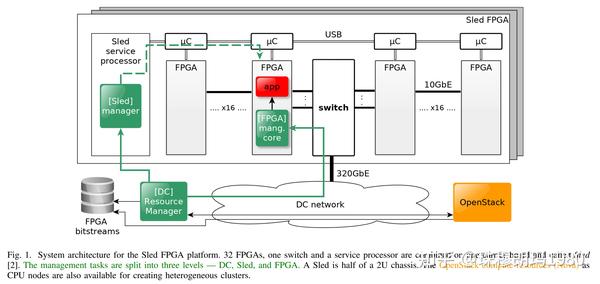

FPGACloud系统架构分为三个层次:数据中心资源管理器(DCRM)、基板管理器(SM)和FPGA管理器核心(FMC)。每个DC有一个资源管理器来控制多个基板,DCRM处理用户FPGA镜像并维护FPGA资源数据库。

每32个FPGA有一个基板管理器。SM在作为基板一部分的服务处理器上运行,它打开和关闭FPGA电源,监视FPGA的物理参数,并运行以太网交换机的软件管理堆栈。

每个FPGA有一个FMC。FMC包含一个简化的HTTP服务器,它为DCRM发出的RestAPI调用提供支持。最后,各个层次的组件协同工作,以快速、安全的方式提供所请求的FPGA资源。

关于DC级FPGA资源的必要信息是FPGA类型(例如XKU060)、FPGA所属的基板服务处理器的IP地址、基板上的插槽号(介于0和31之间)、模块上可用RAM的类型,以及此FPGA的当前状态(例如可用、使用或维护)。DCRM维护包含此类元数据的FPGA资源数据库。管理员可以添加、修改和删除资源。为了允许安全操作,DCRM服务还负责用户的授权和每个用户允许的使用配额。

用户可以上传镜像,存储在DCRM数据库中的FPGA比特流。每个用户都可以上传和删除自己的镜像。如果用户请求将一个特定镜像配置到FPGA,则该镜像将在FPGA上实例化,即配置,然后两者的组合成为一个实例。因此,该架构的基本公式是FPGA资源+image=instance。

DCRM通过将多个FPGA实例和CPU VM分配给同一个子网络,为每个实例提供唯一的节点ID,将必要的路由信息传播到所有设备,从而支持异构集群。DCRM数据库还包含当前实例化FPGA实例或集群的所有信息。

SM在DCRM控制下工作,根据DCRM的API调用,控制FPGA的电源状态,并将MAC和IP地址写入FPGA。

一个单一网络接口承载用户和管理业务,因此FPGA逻辑需要被分离为特权和非特权。否则,DC网络的完整性将面临风险,因为用户可以控制网络接口,以中断其指定的子网,启动拒绝服务攻击或以其他方式伤害提供程序网络。

FMC控制应用程序,是特权逻辑的一部分。使用PR将逻辑拆分为特权和非特权。要在运行时启用PR,需要提前定义PR区域的位置和接口。因此,PR为设计增加了更多的灵活性,同时也定义了静态逻辑和动态逻辑之间清晰的接口。此外,PR还具有加快部分位文件部署速度、保护用户知识产权的优点。特权逻辑在通电时静态配置,称为Shell。因此,通过使用PR,可以控制特权逻辑并定义硬件抽象。Shell还提供运行时信息,例如如果FPGA是集群的一部分,则提供节点id。FMC由DC资源管理器通过定义的RESTful HTTPAPI控制。最后,使用每次需要新PR时通过网络发送的部分比特文件动态配置未特权的应用程序逻辑(也称为角色)。

小结

独立网络连接的FPGA具有特定的管理需求,如网络设置、用户子网的创建、网络路由和配置位文件的分发。通过网络提供这些服务,并演示验证了它们如何无缝集成到OpenStack DC管理软件中。

强制使用部分重配置来物理地将系统管理功能与网络连接的FPGA内的用户逻辑隔离开来。部分重配置(PR)是动态修改FPGA逻辑块的能力,而剩余的逻辑继续运行而不中断。这种方法通过在特权用户逻辑函数和非特权用户逻辑函数之间建立分离来保护DC网络的完整性。

作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/361790107更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。