锲而不舍,金石可镂。

-- 荀况

前面的文章里,讲了一些SoC低功耗相关的设计方法,比如多电压域和电源开关等,《SoC设计之功耗 -- Power Gating》,《SoC设计之功耗 -- Multi Voltage》。基本上是以讲解概念为主,今天来讲一点具体实现的东西。

托EDA工具的福,在多电压和电源开关设计中,需要前端做的逻辑设计非常少,绝大部分工作是在综合和物理设计阶段完成的。这点也好理解,对于逻辑设计工程师来说,电源网络是透明,不可见的,所以跟电源相关的这些设计方法也是不需要关心的。但是必须有一种办法,可以把逻辑设计和物理设计衔接起来才行。这就需要UPF了。

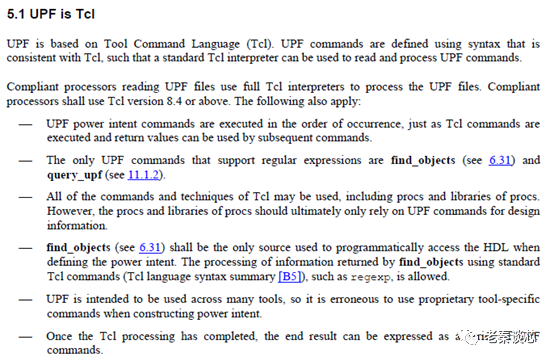

UPF的全称是Unified Power Format,其作用是把功耗设计意图(power intent)传递给EDA工具,从而帮助实现物理设计。这就类似于综合时的约束,是把跟时序相关的设计意图传达给EDA。说简单一些,UPF就是一些tcl命令,系统架构师通过这些命令的组合,把真实的低功耗设计意图传递给工具。下面是UPF的spec中的解释。

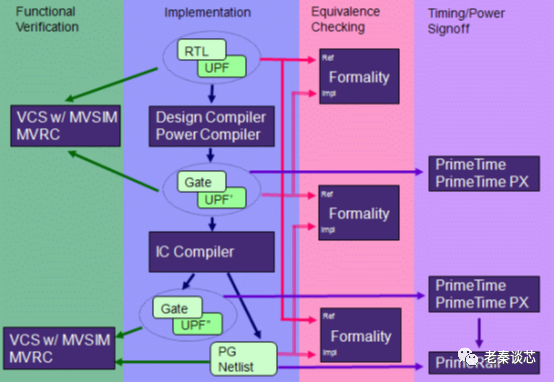

UPF发展到现在,已经成为IEEE的标准(IEEE Std 1801-2018),目前是3.0版本。主流的EDA工具都会支持UPF。下图是S家的低功耗设计流程图。像SDC文件一样,UPF文件要单独编写,在综合阶段作为输入文件送给Design Compiler。综合完成后,DC会生成一个UPF文件给ICC,在物理设计阶段就能看到了level shifter,isolation cell,retention cell和power gating cell了。同时,在验证阶段,也要做一些有关低功耗的仿真工作,这时也需要UPF文件。

图1 Synopsys低功耗设计流程

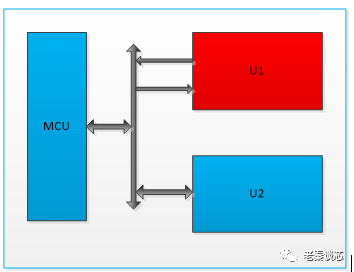

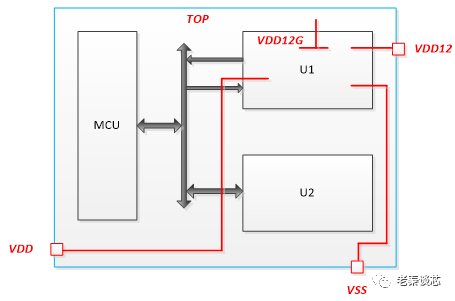

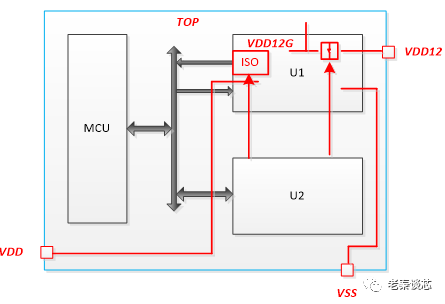

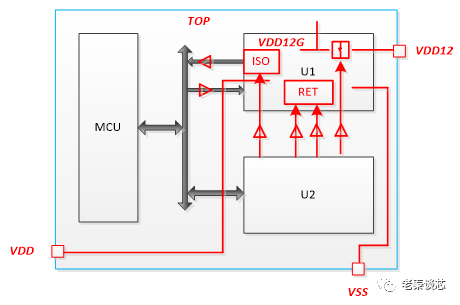

为了让大家有个更清晰的认识,编了一个小的demo。SoC构成非常简单,一个MCU作为控制器,一个功能模块U1,一个功耗控制器U2。假设,U1工作在高电压1.2V,MCU和U2工作在低电压1.0V。当系统处于空闲状态时,可以关闭U1的供电,以减少静态功耗,电源开关的控制信号由U2模块给出。为了简化描述,本demo中不支持DVFS,并省略功耗控制的逻辑设计部分。

有了上面的约定条件,我们可以知道,现在有了两个电源域,分别定义为VH(下图红色)和TOP(蓝色)。

图2 UPF demo

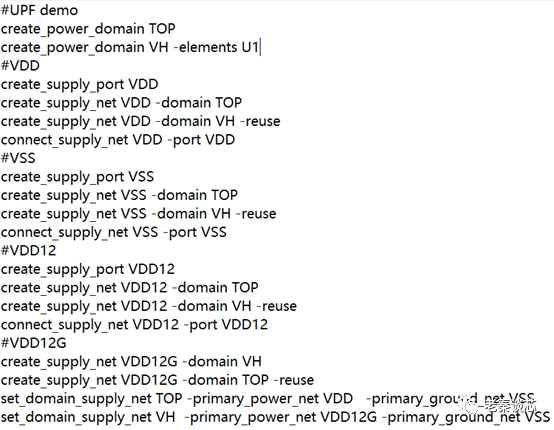

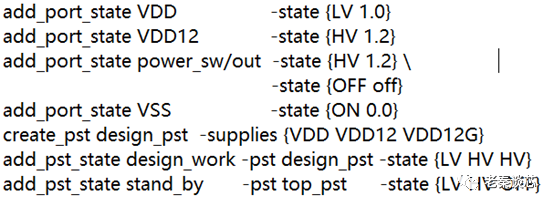

还记得前面提到的,在RTL里面可是看不到供电信息的,我们必须把这个信息告诉工具才行。所以,第一步就是描述电源信息。

图3 在UPF中描述电源信息

现在,EDA工具里的视图就是下面的样子。

图4 添加电源信息后的视图

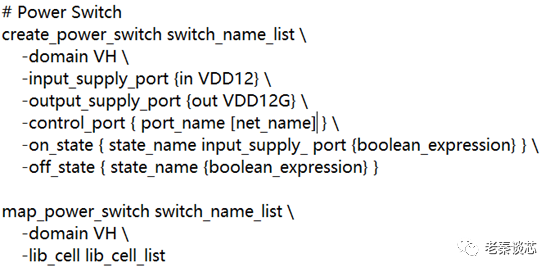

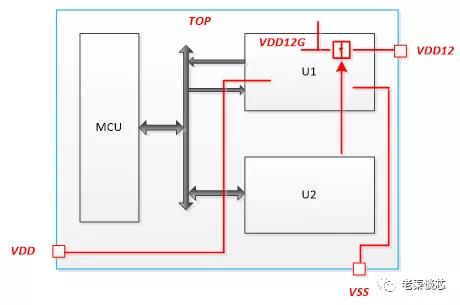

由于U1模块可以做电源关闭,所以要加上power gating,开关信号由功耗控制单元U2给出(忽略具体信号名)。

图5 在UPF中描述PG

图6 添加PG信息后的视图

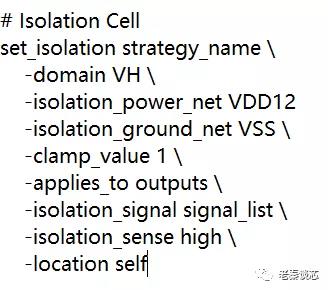

因为U1模块可以关电,所以至少要对其输出信号要做隔离,以保证U1下电后不会影响其它模块正常工作。

图7 在UPF中描述isolation信息

图8 添加isolation信息后的视图

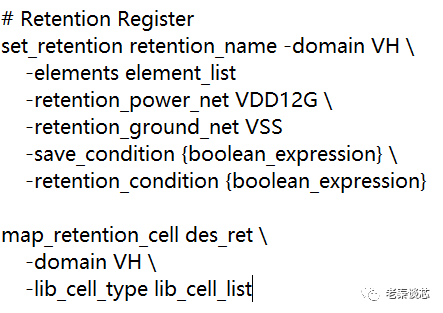

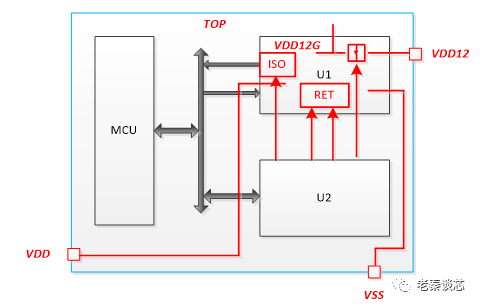

为了保存U1模块下电前的状态,以便U1再次上电后恢复状态,要添加一些retention cell。

图9 在UPF中描述retention

图10 添加retention信息后的视图

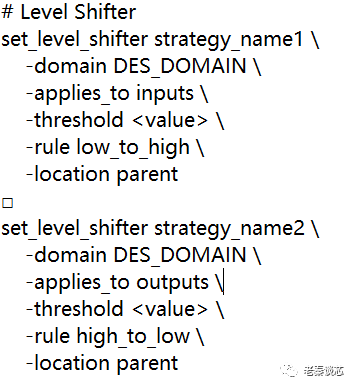

接下来,是对高低电压间的信号转换添加level shifter。

图11 在UPF中描述level shifter

图12 添加level shifter信息后的视图

到此,还差最关键的一步,需要建立一张power table。

图13 power table

以上仅仅是展示一个UPF的demo,里面的一些语法细节我并没有仔细推敲,大家还是以spec为准。实际的SoC低功耗设计肯定要比这个demo复杂得多。

最后提一句,对于设计来讲,isolation和retention还是会影响功能的。比如,假设这个demo中,isolation没做好,U1模块下电后,其输出值没有置到合理值,很可能会影响MCU的正常工作;或者是retention没做好,U1模块再次上电后,不能恢复下电前的状态,造成系统紊乱。综上,对于这部分的低功耗设计,必须要做相应的功能仿真。

作者:老秦谈芯

来源:https://mp.weixin.qq.com/s/l48mtq5rzPF1oXLU35GmiQ

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。