最近看到一个优秀的个人网站,来自宝岛,网站签名就霸气十足——繼續用 Machine-learning 解放半導體產業競爭力 (Cost-effectiveness, Competitiveness and Reliability) 用 AI 改寫所有 EDA Tool 吧!

网站上有系列『浅谈芯片设计』,高屋建瓴视野开阔,老驴以无良自媒体左右手神功,翻译至此,点文末左下角『阅读原文』可以跳转到原文。另,最近大家都收到公众号收费阅读的邀请,老驴会把这篇文章的69% 设为可读,剩余部分设为收费,感受一个新鲜,轻拍!

正文:

台湾很多智人「开公司」,是用作避/节税的(故我不说这是「创业」),因此为了防「君子」,打从你注册/申请成立公司的那一天起,政府就把你当成资方了(立即失去劳保资格),许多不便的设计反而对真正创业者卡卡。而草创期的你很可能还养不起第二个人(法规要五人以上方能成立投保单位),才好加入奇奇怪怪的鸡蛋运输工会,状态上你就开始失业了。而这是目前台湾的微创业环境。

半导体行业竞争激烈,产业瞬息万变(像是在演霹雳布袋戏),若想稳固所处的企业在国际间之竞争力,「你」扮演重要角色!(「IC设计」有没有办法变成「养」的产业?小额,大量,持续而稳定地收钱,且不因买卖商品/服务/技术中止?跟Maker 收月租费吗(B2O)?变成平台商/媒合商(O2O)?提供教育训练?让带WiFi 功能的Arduino 芯片变耗材/热插拔吗?Amazon 的Echo 是否会打破Google 搜寻的广告流量获利模式/金流呢?…闷)

回到假象敌(Competitor)设定

上一回提到「竞争力( Competitiveness )这个指标」,我们拟定了一个核心竞争力,并假设Foundry 愿意承担/妥协部分「风险」与「成本效益(cost-effective)」以共享「部份」经济成长果实,亦即最后加诸于我们竞争对手的「设计余量(Deign Margin)」是相对减轻非常多的,好比「时序验证配方(timing sign-off recipe)」可能是TT ± n * σ(n = 1〜3,取决于一级玩家的议价能力)。但幸运的是:还有许多环节不够科学!这是面对强敌依然有机会/缝隙翻转的契机(先卖关子)。

此外,我们也假设这个标竿还非常善于做「Branding」且熟「消费心理学」(像Apache 就非常善用人性的弱点:善用论文举证deterministic risks, 掀起恐慌(Availability Cascade?)并提供索费不赀的药方,但不保证有效,像是在卖抗癌药),他们总是有很多专利/论文,并试图主导技术规格。这一部份,我们比较使不上力,既使自己创业也一样。除非老板们支持,你须先自己走在前头并当传教师,形塑企业文化,透过内化让大家慢慢向前。(很多老板甚至会抗拒产学合作,然而这没有对错,端看企业的企图与scope)。

目标市场/策略

我们也讨论过:产业一旦转型了(企业能在多大产值中分杯羹也已决定),接下来最重要的应该是市场的选择,亦就是客户在哪?要卖什么?不过,除非自己创业,否则只能期待高层老板们能深思熟虑,而且对未来市场能有所帮助洞见了。

以「晶片设计市场」而言,相较于运动摄影机,行车纪录器,轻型无人机,挖矿机/机器学习(以矩阵运算为主)等领域,「手机晶片」技术堪称是竞争最「辛苦」且最惨烈的领域。其从软体至硬体含周边架构与介面,进化与淘汰速度之快,令人瞠目结舌。但总体现状却是:“万家烤肉,一家香的格局”。以2016年市调资料来看,苹果以仅12.9%之全球智慧手机市占率(三星约24%市占第一)却囊括了全球91%的盈利。换句话说:从顶层到底层每个环节只要稍有闪失,就很可能失去市场竞争力。反之,「从顶层到底层每个环节我们都得赢人家一点点」才有可能出类拔萃。

笔者:改做无人载具,机器人学习或AI芯片吧!

錨點效應(Anchoring Effect)

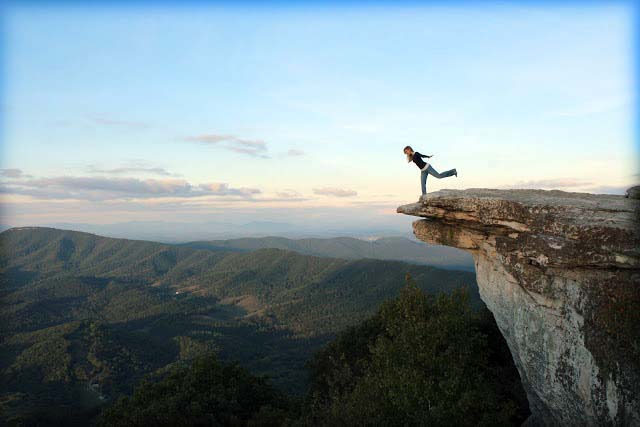

图片来源:Jelly Wong,注:网路上后制的版本非常多,我试着比较图片场景的涵盖率最后找出应该是原作者的连结。

发现上面这张图时(这家伙似乎离悬崖边更近了,惊),笔者正好积极的尝试推广将机器学习等相关技巧应用至芯片设计流程,包括各种晶片监测器设计/专利(需要花时间研究/避一避),后矽制程配方建议,自我评等与补偿( PVT /aging compensation )等系统开发,希望最终能为全球半导体三千多亿美金的产值再增加个5%,可以打造一座杜「拜亚特兰堤斯酒店」呢!(笔者承认这是「系统一的直觉」,但希望所有design houses 加总的晶片能再多卖个n% 不为过吧!?n 取决于对下文内容的检验/共鸣)。

上一回我们把晶片实体设计的竞赛比喻成:「看看谁能最靠近悬崖边,又可以很安全的不至于跌个粉身碎骨」,也就是「看看谁的设计余量(design margin)相对抓得少又安全」这张图,正好像是当时心情的写照:「你的竞争对手已如此强大,若想在同一个舞台分杯羹,我们必须尝试别人没做过的!」

有时候我们想要更大胆跟别人做不一样的尝试,却又迟迟不敢跨出那一步。这很正常,康纳曼将这现象解释为『锚点效应(Anchoring Effect)』之『调整不足』。「系统一」完全没任何经验资讯可供「系统二」提取/评估,因此在心智上移动的锚会提早结束:深怕跌入谷底。

经验丰富的「Free Climber」其心智运作就不一样,他的「锚」打从一开始就设在悬崖边上的。当然若你在这世界上是有如阿汤哥-神一般的存在(属于保育类的英雄),你几乎可以把所有的Margin 都丢光,根本让人望尘莫及!千万别学阿汤哥啊!(叔叔有练过)除非Foundry 是你家的(如三星,Intel),library 自己做/自己K 的,同时还能边调整/改善process, memory, standard cell 等,能够掌控一切事情。

但笔者想跟大家分享的是:我们必须利用「工具」,「安全的攀岩」,以弥补先天的劣势(慢慢再来讨论)。实际上,有时候有时计划性的探底并不是什么坏事( pilot chip ), 从此我们可以架起系统,让平凡如你我等都能从此安全无虑的抵达悬崖边,即使是更为严峻的冰天雪地——下一个专案。

有两种「心智捷径」运作历程笔者都经历过,一种是:你可以跟大家举手提议要做「TT±2σ」,但由于每个人的「锚」都尚还在『SS-3σ』附近,因此您得提出强而有力的证据/经验(可能的风险与解决方案)才可能让每个彼此都不Align 的心智移动,通常不会太远。(可能会说你吹牛)。

下次,若你的顶层老板直接给你下达一个要命的任务:『我们要TT signoff』!很好,老板有研究心理学,这是一个强迫Reset 你心智的「锚」!大家会开始动员起来,寻求『配套措施』,从顶层至底层全面性地思考各种手段,纵使康纳曼告诉我们:我们的心智移动在未达到目的地时就会提早结束,但至少最终每个人都会远离SS-3σ 区域。撑着啊!老兄!

用Google 檢視自己的「設計餘量吧(Design Margin) 」!

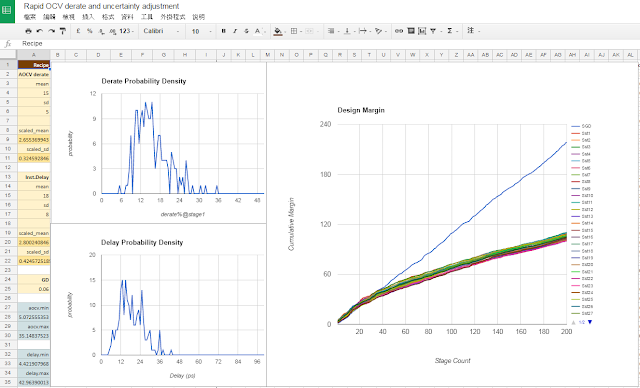

自己用来从事『芯片实体设计的配方(timing recipe for chip implementation) 』有竞争力吗?且让我们利用Google-Sheet 做的 『Rapid STA signoff recipe examination』很简单/快速地检视一下吧!为何用Google?因为要开源,且其容量可以比Excel大。请选择File / Download\_as / Excel 将表单先暂存到自己电脑本地,再用Google-Sheet把它开起来即可编辑。(因为是开源,请不要把那搞坏了或骇客我哪!感恩)。

笔者透过建立几个「机率统计」的模型,依大数法则将「正态分布」转换成比较贴近实际统计资料行为的「对数正态分布」,并利用Google 本身提供的工具随机丢了30 次骰子举证(读者可以自行扩大表格丢更多次骰子),以供大家检视现行的设计余量是否抓的多太过保守或不够科学?(若你的GPU 或CPU 跟其他SOC 模块是用相同的实体设计配方岂不怪哉?)。因为Foundry 根本无暇了解或『齐头式拉平』其所有客户(design house)的设计方法/品质与能力,仅能提供一个极粗略的「万用/免责」配方,而代价就是丧失竞争力。(但也有很多tier-1 company 比Foundry 强,所以Foundry 会反过来偷学其方法)。

因Google-Sheet 也有计算量限制的问题,可能的话烦请有兴趣的读者用C / C ++(或其他你熟悉的语言)将它改写,如此我们可以很快跑出100K parts 以上类似SPICE Monte 的结果。

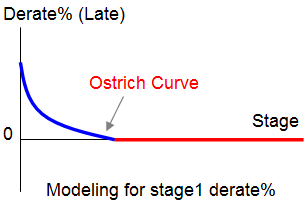

笔者认为基于LVF 的实作面(如SOCV)要普遍还需要再过一两年<驴注:本文成文于2017年>,虽然K-library 不是问题,但有能力验证其资料合理性与正确性的人并不多(包括Foundry自己的library team ),否则就不会看到鸵鸟图(Ostrich Curve)了。例如Timing path 在十几个stage 上(若使用launch + capture 的设定,这非常容易远远超过)之后derate为0,这非常鸵鸟!

为了避免不必要的恐慌,我们暂且不提当今『神棍级(非神盾级喔)芯片设计配方』的奇妙与乱象(虽然大家普遍仍然买单),而某些design house『不买单』的程度我会将它解读为该公司『提升竞争力的潜力』(总体还要有对策才行吧?!)。当然,你若已经发现/掌握Foundry 的许多“Bugs”(我们后续谈谈),恭喜,你可以先偷跑,因为它(基于LVF的flow)比较科学(slew/load dependent, cell-based constraint uncertainty, common point optimism reomval 等),也很补(缩小设计余量),只是验证(QA)要花功夫且要很小心。

这个表单我们仍以目前业界普遍的stage-based OCV 方法为例(或称AOCV),可以将其看成是在一张LVF 表格里,籍由控制/约束cell 在某个transition 与load 范围内,比较/选取一个较悲观的σ值,而derate 随着path stage 级数增加逐渐收敛(基于随机杂讯的Cancellation 效应)。针对这个部分,Foundry 宣称用真实的path 跑SPICE 模拟所得到的方法其实并不好!(看起来也作弊/造假,哪有clock/ data/ early/ late/ rising/ falling 会一样的这回事?)

第一阶(Stage-1)的值通常以类似跑SPICE Monte 得到,EDA 有较快的solution(但不是真的Monte),但其他值(Stage-2〜n)笔者建议套用statistical sum 的数学模型以避免鸵鸟,即derate 随着path stage 级数增加Converge 到(k *σ* n ^α)/ n,其中,n 为stage count,α在0.5〜0.65之间(有EDA 厂商/论文用0.5,但不一定适合某些Foundry 或套用至各种不同的工艺,Vt, Channel-length 等元件,这也是基于LVF 的设计流程还看不到相关控制/客制化选项的潜在问题), k 看你的心脏大小(承受风险),介于1〜3之间,通常透过SPICE 对STA Correlation 可以适当的把它调小(多虑是正常的,这是『锚点效应(Anchoring Effect)』之『调整不足』),实际上所谓的GD / OCV / AOCV / SBOCV 方法原本就很Heuristic,只是我们买单罢了!

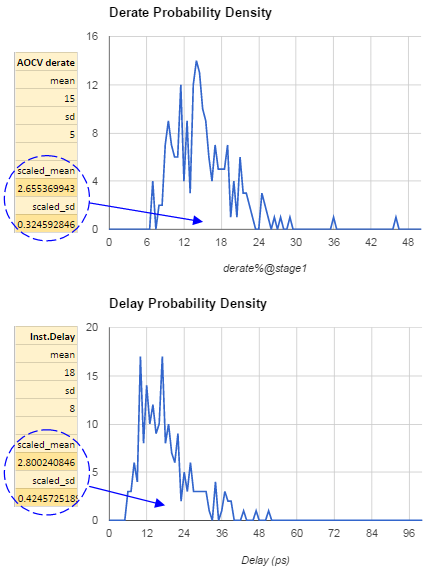

这个表单主要有两个机率密度函数:1)第一阶derate%,即我们加诸于实体设计(physical design)与时序验证(timing signoff)时的design margin,以及2)逻辑闸传输过程的时间延迟delay(ps)。

剩余付费内容请至原文阅读:https://mp.weixin.qq.com/s/u-6B-CuXtPiPfxIchgqsfw

作者:陌上风骑驴看IC

原文链接:https://mp.weixin.qq.com/s/u-6B-CuXtPiPfxIchgqsfw

微信公众号:

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。