PCI(Peripheral Component Interconnect)总线的诞生与PC(Personal Computer)的蓬勃发展密切相关。在处理器体系结构中,PCI总线属于局部总线(Local Bus)。局部总线作为系统总线的延伸,主要功能是为了连接外部设备。

处理器主频的不断提升,要求速度更快,带宽更高的局部总线。起初PC使用8位的XT总线作为局部总线,并很快升级到16位的ISA(Industry Standard Architecture)总线,逐步发展到32位的EISA(Extended Industry Standard Architecture)、VESA(Video Electronics Standards Association)和MCA(Micro Channel Architecture)总线。

PCI总线规范在上世纪九十年代提出。这条总线推出之后,很快得到了各大主流半导体厂商的认同,迅速统一了当时并存的各类局部总线。EISA、VESA等其他32位总线很快就被PCI总线淘汰了。从那时起,PCI总线一直在处理器体系结构中占有重要地位。

在此后相当长的一段时间里,PC处理器系统的大多数外部设备都是直接或者间接地与PCI总线相连。即使目前PCI Express总线逐步取代了PCI总线成为PC局部总线的主流,也不能掩盖PCI总线的光芒。从软件层面上看,PCI Express总线与PCI总线基本兼容;从硬件层面上看,PCI Express总线在很大程度上继承了PCI总线的设计思路。因此PCI总线依然是软硬件工程师在进行处理器系统的开发与设计时,必须要掌握的一条局部总线。

PCI总线V1.0规范仅针对在一个PCB(Printed Circuit Board)环境内的,器件之间的互连,而1993年4月30日发布的V2.0规范增加了对PCI插槽的支持。1995年6月1日,PCI V2.1总线规范发布,这个规范具有里程碑意义。正是这个规范使得PCI总线大规模普及,至此PCI总线完成了对(E)ISA和MCA总线的替换。

至1996年,VESA总线也逐渐离开了人们的视线,当然PCI总线并不能完全提供显卡所需要的带宽,真正替代VESA总线的是AGP总线。随后PCISIG(PCI Special Interest Group)陆续发布了PCI总线V2.2,V2.3规范,并最终将PCI总线规范定格在V3.0。

除了PCI总线规范外,PCISIG还定义了一些与PCI总线相关的规范,如PCMCIA(Personal Computer Memory Card International Association)规范和MiniPCI规范。其中PCMCIA规范主要针对Laptop应用,后来PCMCIA升级为PC Card(Cardbus)规范,而PC Card又升级为ExpressCard规范。

PC Card规范基于32位,33MHz的PCI总线;而ExpressCard规范基于PCI Express和USB 2.0。这两个规范都在Laptop领域中获得了成功。除了PCMCIA规范外,Mini PCI总线也非常流行,与标准PCI插槽相比,Mini PCI插槽占用面积较小,适用于一些对尺寸有要求的应用。

除了以上规范之外,PCISIG还推出了一系列和PCI总线直接相关的规范。如PCI-to-PCI桥规范、PCI电源管理规范、PCI热插拔规范和CompactPCI总线规范。其中PCI-to-PCI桥规范最为重要,理解PCI-to-PCI桥是理解PCI体系结构的基础;而CompactPCI总线规范多用于具有背板结构的大型系统,并支持热拔插。

PCISIG在PCI总线规范的基础上,进一步提出PCI-X规范。与PCI总线相比,PCI-X总线规范可以支持133MHz、266MHz和533MHz的总线频率,并在传送规则上做了一些改动。虽然PCI-X总线还没有得到大规模普及就被PCI Express总线替代,但是在PCI-X总线中提出的许多设计思想仍然被PCI Express总线继承。

PCI总线规范是Intel对PC领域做出的一个巨大贡献。Intel也在PCI总线规范留下了深深的印记,PCI总线规范的许多内容都与基于IA (Intel Architecture)架构的x86处理器密切相关。但是这并不妨碍其他处理器系统使用PCI总线,事实上PCI总线在非x86处理器系统上也取得了巨大的成功。目前绝大多数处理器系统都使用PCI/PCI Express总线连接外部设备,特别是一些通用外设。

随着时间的推移,PCI和PCI-X总线逐步遇到瓶颈。PCI和PCI-X总线使用单端并行信号进行数据传递,由于单端信号容易被外部系统干扰,其总线频率很难进一步提高。目前,为了获得更高的总线频率以提高总线带宽,高速串行总线逐步替代了并行总线。PCI Express总线也逐渐替代PCI总线成为主流。但是从系统软件的角度上看,PCI Express总线仍然基于PCI总线。理解PCI Express总线的一个基础是深入理解PCI总线,同时PCI Express总线也继承了PCI总线的许多概念。本篇将详细介绍与处理器体系结构相关的,一些必备的PCI总线知识。

为简化起见,本篇主要介绍PCI总线的32位地址模式。在实际应用中,使用64位地址模式的PCI设备非常少。而且在PCI Express总线逐渐取代PCI总线的大趋势之下,将来也很难会有更多的,使用64位地址的PCI设备。如果读者需要掌握PCI总线的64位地址模式,请自行阅读PCI总线的相关规范。实际上,如果读者真正掌握了PCI总线的32位地址模式之后,理解64位地址模式并不困难。

为节省篇幅,下文将PCI Express总线简称为PCIe总线,PCI-to-PCI桥简称为PCI桥,PCI Express-to-PCI桥简称为PCIe桥,Host-to-PCI主桥简称为HOST主桥。值得注意的是许多书籍将HOST主桥称为PCI主桥或者PCI总线控制器。

PCI总线的基本知识

PCI总线作为处理器系统的局部总线,主要目的是为了连接外部设备,而不是作为处理器的系统总线连接Cache和主存储器。但是PCI总线、系统总线和处理器体系结构之间依然存在着紧密的联系。

PCI总线作为系统总线的延伸,其设计考虑了许多与处理器相关的内容,如处理器的Cache共享一致性和数据完整性,以及如何与处理器进行数据交换等一系列内容。其中Cache共享一致性和数据完整性是现代处理器局部总线的设计的重点和难点,也是本书将重点讲述的主题之一。

独立地研究PCI总线并不可取,因为PCI总线仅是处理器系统的一个组成部分。深入理解PCI总线需要了解一些与处理器体系结构相关的知识。这些知识是本书所侧重描述的,同时也是PCI总线规范所忽略的内容。脱离实际的处理器系统,不容易也不可能深入理解PCI总线规范。

对于今天的读者来说,PCI总线提出的许多概念略显过时,也有许多不足之处。但是在当年,PCI总线与之前的存在其他并行局部总线如ISA、EISA和MCA总线相比,具有许多突出的优点,是一个全新的设计。

(1) PCI总线空间与处理器空间隔离

PCI设备具有独立的地址空间,即PCI总线地址空间,该空间与存储器地址空间通过HOST主桥隔离。处理器需要通过HOST主桥才能访问PCI设备,而PCI设备需要通过HOST主桥才能主存储器。在HOST主桥中含有许多缓冲,这些缓冲使得处理器总线与PCI总线工作在各自的时钟频率中,彼此互不干扰。HOST主桥的存在也使得PCI设备和处理器可以方便地共享主存储器资源。

处理器访问PCI设备时,必须通过HOST主桥进行地址转换;而PCI设备访问主存储器时,也需要通过HOST主桥进行地址转换。HOST主桥的一个重要作用就是将处理器访问的存储器地址转换为PCI总线地址。PCI设备使用的地址空间是属于PCI总线域的,而与存储器地址空间不同。

x86处理器对PCI总线域与存储器域的划分并不明晰,这也使得许多程序员并没有准确地区分PCI总线域地址空间与存储器域地址空间。而本书将反复强调存储器地址和PCI总线地址的区别,因为这是理解PCI体系结构的重要内容。

PCI规范并没有对HOST主桥的设计进行约束。每一个处理器厂商使用的HOST主桥,其设计都不尽相同。HOST主桥是联系PCI总线与处理器的核心部件,掌握HOST主桥的实现机制是深入理解PCI体系结构的前提。

本书将以Freescale的PowerPC处理器和Intel的x86处理器为例,说明各自HOST主桥的实现方式,值得注意的是本书涉及的PowerPC处理器仅针对Freescale的PowerPC处理器,而不包含IBM和AMCC的Power和PowerPC处理器。而且如果没有特别说明,本书中涉及的x86处理器特指Intel的处理器,而不是其他厂商的x86处理器。

(2) 可扩展性

PCI总线具有很强的扩展性。在PCI总线中,HOST主桥可以直接推出一条PCI总线,这条总线也是该HOST主桥的所管理的第一条PCI总线,该总线还可以通过PCI桥扩展出一系列PCI总线,并以HOST主桥为根节点,形成1颗PCI总线树。这些PCI总线都可以连接PCI设备,但是在1颗PCI总线树上,最多只能挂接256个PCI设备(包括PCI桥)。

在同一条PCI总线上的设备间可以直接通信,并不会影响其他PCI总线上设备间的数据通信。隶属于同一颗PCI总线树上的PCI设备,也可以直接通信,但是需要通过PCI桥进行数据转发。

PCI桥是PCI总线的一个重要组成部件,该部件的存在使得PCI总线极具扩展性。PCI桥也是有别于其他局部总线的一个重要部件。在“以HOST主桥为根节点”的PCI总线树中,每一个PCI桥下也可以连接一个PCI总线子树,PCI桥下的PCI总线仍然可以使用PCI桥继续进行总线扩展。

PCI桥可以管理这个PCI总线子树,PCI桥的配置空间含有一系列管理PCI总线子树的配置寄存器。在PCI桥的两端,分别连接了两条总线,分别是上游总线(Primary Bus)和下游总线(Secondary Bus)。其中与处理器距离较近的总线被称为上游总线,另一条被称为下游总线。这两条总线间的通信需要通过PCI桥进行。PCI桥中的许多概念被PCIe总线采纳,理解PCI桥也是理解PCIe体系结构的基础。

(3) 动态配置机制

PCI设备使用的地址可以根据需要由系统软件动态分配。PCI总线使用这种方式合理地解决了设备间的地址冲突,从而实现了“即插即用”功能。从而PCI总线不需要使用ISA或者EISA接口卡为解决地址冲突而使用的硬件跳线。

每一个PCI设备都有独立的配置空间,在配置空间中含有该设备在PCI总线中使用的基地址,系统软件可以动态配置这个基地址,从而保证每一个PCI设备使用的物理地址并不相同。PCI桥的配置空间中含有其下PCI子树所能使用的地址范围。

(4) 总线带宽

PCI总线与之前的局部总线相比,极大提高了数据传送带宽,32位/33MHz的PCI总线可以提供132MB/s的峰值带宽,而64位/66MHz的PCI总线可以提供的峰值带宽为532MB/s。虽然PCI总线所能提供的峰值带宽远不能和PCIe总线相比,但是与之前的局部总线ISA、EISA和MCA总线相比,仍然具有较大的优势。

ISA总线的最高主频为8MHz,位宽为16,其峰值带宽为16MB/s;EISA总线的最高主频为8.33MHz,位宽为32,其峰值带宽为33MB/s;而MCA总线的最高主频为10MHz,最高位宽为32,其峰值带宽为40MB/s。PCI总线提供的峰值带宽远高于这些总线。

(5) 共享总线机制

PCI设备通过仲裁获得PCI总线的使用权后,才能进行数据传送,在PCI总线上进行数据传送,并不需要处理器进行干预。

PCI总线仲裁器不在PCI总线规范定义的范围内,也不一定是HOST主桥和PCI桥的一部分。虽然绝大多数HOST主桥和PCI桥都包含PCI总线仲裁器,但是在某些处理器系统的设计中也可以使用独立的PCI总线仲裁器。如在PowerPC处理器的HOST主桥中含有PCI总线仲裁器,但是用户可以关闭这个总线仲裁器,而使用独立的PCI总线仲裁器。

PCI设备使用共享总线方式进行数据传递,在同一条总线上,所有PCI设备共享同一总线带宽,这将极大地影响PCI总线的利用率。这种机制显然不如PCIe总线采用的交换结构,但是在PCI总线盛行的年代,半导体的工艺、设计能力和制作成本决定了采用共享总线方式是当时的最优选择。

(6) 中断机制

PCI总线上的设备可以通过四根中断请求信号INTA~D#向处理器提交中断请求。与ISA总线上的设备不同,PCI总线上的设备可以共享这些中断请求信号,不同的PCI设备可以将这些中断请求信号“线与”后,与中断控制器的中断请求引脚连接。PCI设备的配置空间记录了该设备使用这四根中断请求信号的信息。

PCI总线进一步提出了MSI(Message Signal Interrupt)机制,该机制使用存储器写总线事务传递中断请求,并可以使用x86处理器FSB(Front Side Bus)总线提供的Interrupt Message总线事务,从而提高了PCI设备的中断请求效率。

虽然从现代总线技术的角度上看,PCI总线仍有许多不足之处,但也不能否认PCI总线已经获得了巨大的成功,不仅x86处理器将PCI总线作为标准的局部总线连接各类外部设备,PowerPC、MIPS和ARM[1]处理器也将PCI总线作为标准局部总线。除此之外,基于PCI总线的外部设备,如以太网控制器、声卡、硬盘控制器等,也已经成为主流。

[1] 在ARM处理器中,使用SoC平台总线,即AMBA总线,连接片内设备。但是某些ARM生产厂商,依然使用AMBA-to-PCI桥推出PCI总线,以连接PCI设备。

PCI总线的组成结构

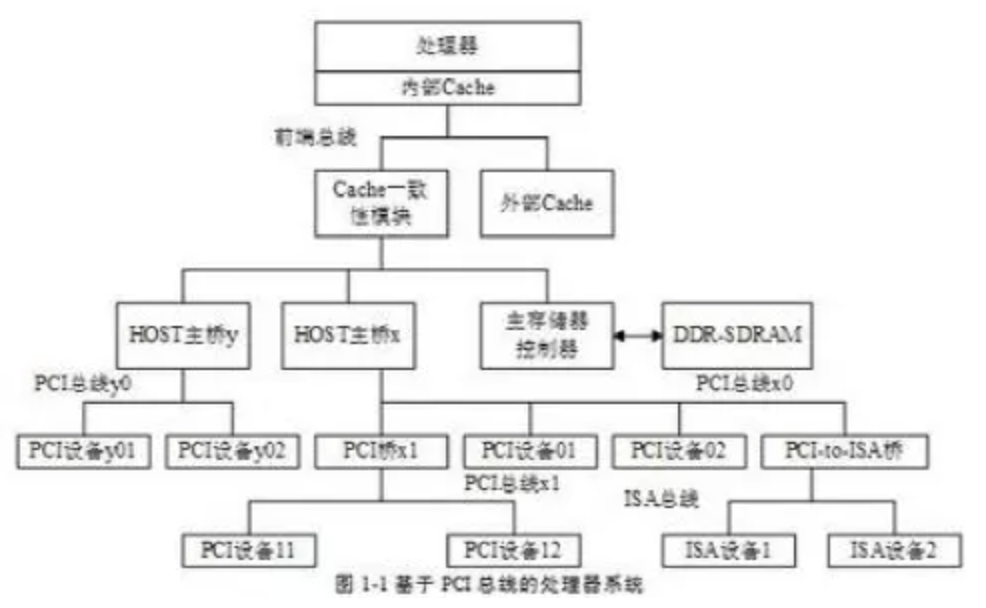

如上文所述,PCI总线作为处理器系统的局部总线,是处理器系统的一个组成部件,讲述PCI总线的组成结构不能离开处理器系统这个大环境。在一个处理器系统中,与PCI总线相关的模块如图1‑1所示。

如图1‑1所示在一个处理器系统中,与PCI总线相关的模块包括,HOST主桥、PCI总线、PCI桥和PCI设备。PCI总线由HOST主桥和PCI桥推出,HOST主桥与主存储器控制器在同一级总线上,PCI设备可以方便地通过HOST主桥访问主存储器,即进行DMA操作。

值得注意的是,PCI设备的DMA操作需要与处理器系统的Cache进行一致性操作,当PCI设备通过HOST主桥访问主存储器时,Cache一致性模块将进行地址监听,并根据监听的结果改变Cache的状态。

在一些简单的处理器系统中,可能不含有PCI桥,此时所有PCI设备都是连接在HOST主桥推出的PCI总线上,此外在一些处理器系统中可能含有多个HOST主桥,如在图1‑1所示的处理器系统中含有HOST主桥x和HOST主桥Y。

1.1.1 HOST主桥

HOST主桥是一个很特别的桥片,其主要功能是隔离处理器系统的存储器域与处理器系统的PCI总线域,管理PCI总线域,并完成处理器与PCI设备间的数据交换。处理器与PCI设备间的数据交换主要由“处理器访问PCI设备的地址空间”和“PCI设备使用DMA机制访问主存储器”这两部分组成。

为简便起见,下文将处理器系统的存储器域简称为存储器域,而将处理器系统的PCI总线域称为PCI总线域,存储器域和PCI总线域的详细介绍见第2.1节。值得注意的是,在一个处理器系统中,有几个HOST主桥,就有几个PCI总线域。

HOST主桥在处理器系统中的位置并不相同,如PowerPC处理器将HOST主桥与处理器集成在一个芯片中。而有些处理器不进行这种集成,如x86处理器使用南北桥结构,处理器内核在一个芯片中,而HOST主桥在北桥中。但是从处理器体系结构的角度上看,这些集成方式并不重要。

PCI设备通过HOST主桥访问主存储器时,需要与处理器的Cache进行一致性操作,因此在设计HOST主桥时需要重点考虑Cache一致性操作。在HOST主桥中,还含有许多数据缓冲,以支持PCI总线的预读机制。

HOST主桥是联系处理器与PCI设备的桥梁。在一个处理器系统中,每一个HOST主桥都管理了一颗PCI总线树,在同一颗PCI总线树上的所有PCI设备属于同一个PCI总线域。如图1‑1所示,HOST主桥x之下的PCI设备属于PCI总线x域,而HOST主桥y之下的PCI设备属于PCI总线y域。在这颗总线树上的所有PCI设备的配置空间都由HOST主桥通过配置读写总线周期访问。

如果HOST主桥支持PCI V3.0规范的Peer-to-Peer数据传送方式,那么分属不同PCI总线域的PCI设备可以直接进行数据交换。如图1‑1所示,如果HOST主桥y支持Peer-to-Peer数据传送方式,PCI设备y01可以直接访问PCI设备01或者PCI设备11,而不需要通过处理器的参与。但是这种跨越总线域的数据传送方式在PC架构中并不常用,在PC架构中,重点考虑的是PCI设备与主存储器之间的数据交换,而不是PCI设备之间的数据交换。此外在PC架构中,具有两个HOST主桥的处理器系统也并不多见。

在PowerPC处理器中,HOST主桥可以通过设置Inbound寄存器,使得分属于不同PCI总线域的设备可以直接通信。许多PowerPC处理器都具有多个HOST主桥,有关PowerPC处理器使用的HOST主桥详见第2.2节。

1.1.2 PCI总线

在处理器系统中,含有PCI总线和PCI总线树这两个概念。这两个概念并不相同,在一颗PCI总线树中可能具有多条PCI总线,而具有血缘关系的PCI总线组成一颗PCI总线树。如在图1‑1所示的处理器系统中,PCI总线x树具有两条PCI总线,分别为PCI总线x0和PCI总线x1。而PCI总线y树中仅有一条PCI总线。

PCI总线由HOST主桥或者PCI桥管理,用来连接各类设备,如声卡、网卡和IDE接口卡等。在一个处理器系统中,可以通过PCI桥扩展PCI总线,并形成具有血缘关系的多级PCI总线,从而形成PCI总线树型结构。在处理器系统中有几个HOST主桥,就有几颗这样的PCI总线树,而每一颗PCI总线树都与一个PCI总线域对应。

与HOST主桥直接连接的PCI总线通常被命名为PCI总线0。考虑到在一个处理器系统中可能有多个主桥,图1‑1将HOST主桥x推出的PCI总线命名为x0总线,而将PCI桥x1扩展出的PCI总线称之为x1总线;而将HOST主桥y推出的PCI总线称为y0~yn。分属不同PCI总线树的设备,其使用的PCI总线地址空间分属于不同的PCI总线域空间。

1.1.3 PCI设备

在PCI总线中有三类设备,PCI主设备、PCI从设备和桥设备。其中PCI从设备只能被动地接收来自HOST主桥,或者其他PCI设备的读写请求;而PCI主设备可以通过总线仲裁获得PCI总线的使用权,主动地向其他PCI设备或者主存储器发起存储器读写请求。而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。

一个PCI设备可以即是主设备也是从设备,但是在同一个时刻,这个PCI设备或者为主设备或者为从设备。PCI总线规范将PCI主从设备统称为PCI Agent设备。在处理器系统中常见的PCI网卡、显卡、声卡等设备都属于PCI Agent设备。

在PCI总线中,HOST主桥是一个特殊的PCI设备,该设备可以获取PCI总线的控制权访问PCI设备,也可以被PCI设备访问。但是HOST主桥并不是PCI设备。PCI规范也没有规定如何设计HOST主桥。

在PCI总线中,还有一类特殊的设备,即桥设备。桥设备包括PCI桥、PCI-to-(E)ISA桥和PCI-to-Cardbus桥。本篇重点介绍PCI桥,而不关心其他桥设备的实现原理。PCI桥的存在使PCI总线极具扩展性,处理器系统可以使用PCI桥进一步扩展PCI总线。

PCI桥的出现使得采用PCI总线进行大规模系统互连成为可能。但是在目前已经实现的大规模处理器系统中,并没有使用PCI总线进行处理器系统与处理器系统之间的大规模互连。因为PCI总线是一个以HOST主桥为根的树型结构,使用主从架构,因而不易实现多处理器系统间的对等互连。

即便如此PCI桥仍然是PCI总线规范的精华所在,掌握PCI桥是深入理解PCI体系结构的基础。PCI桥可以连接两条PCI总线,上游PCI总线和下游PCI总线,这两个PCI总线属于同一个PCI总线域,使用PCI桥扩展的所有PCI总线都同属于一个PCI总线域。

其中对PCI设备配置空间的访问可以从上游总线转发到下游总线,而数据传送可以双方向进行。在PCI总线中,还存在一种非透明PCI桥,该桥片不是PCI总线规范定义的标准桥片,但是适用于某些特殊应用,本篇将在第2.5节中详细介绍这种桥片。在本书中,如不特别强调,PCI桥是指透明桥,透明桥也是PCI总线规范定义的标准桥片。

PCI-to-(E)ISA桥和PCI-to-Cardbus桥的主要作用是通过PCI总线扩展(E)ISA和Cardbus总线。在PCI总线推出之后,(E)ISA总线并没有在处理器系统中立即消失,此时需要使用PCI-(E)ISA桥扩展(E)ISA总线,而使用PCI-to-Cardbus桥用来扩展Cardbus总线,本篇并不关心(E)ISA和Cardbus总线的设计与实现。

1.1.4 HOST处理器

PCI总线规定在同一时刻内,在一颗PCI总线树上有且只有一个HOST处理器。这个HOST处理器可以通过HOST主桥,发起PCI总线的配置请求总线事务,并对PCI总线上的设备和桥片进行配置。

在PCI总线中,HOST处理器是一个较为模糊的概念。在SMP(symmetric multiprocessing)处理器系统中,所有CPU都可以通过HOST主桥访问其下的PCI总线树,这些CPU都可以作为HOST处理器。但是值得注意的是,HOST主桥才是PCI总线树的实际管理者,而不是HOST处理器。

在HOST主桥中,设置了许多寄存器,HOST处理器通过操作这些寄存器管理这些PCI设备。如在x86处理器的HOST主桥中设置了0xCF8和0xCFC这两个I/O端口访问PCI设备的配置空间,而PowerPC处理器的HOST主桥设置了CFG\_ADDR和CFG\_DATA寄存器访问PCI设备的配置空间。值得注意的是,在PowerPC处理器中并没有I/O端口,因此使用存储器映像寻址方式访问外部设备的寄存器空间。

1.1.5 PCI总线的负载

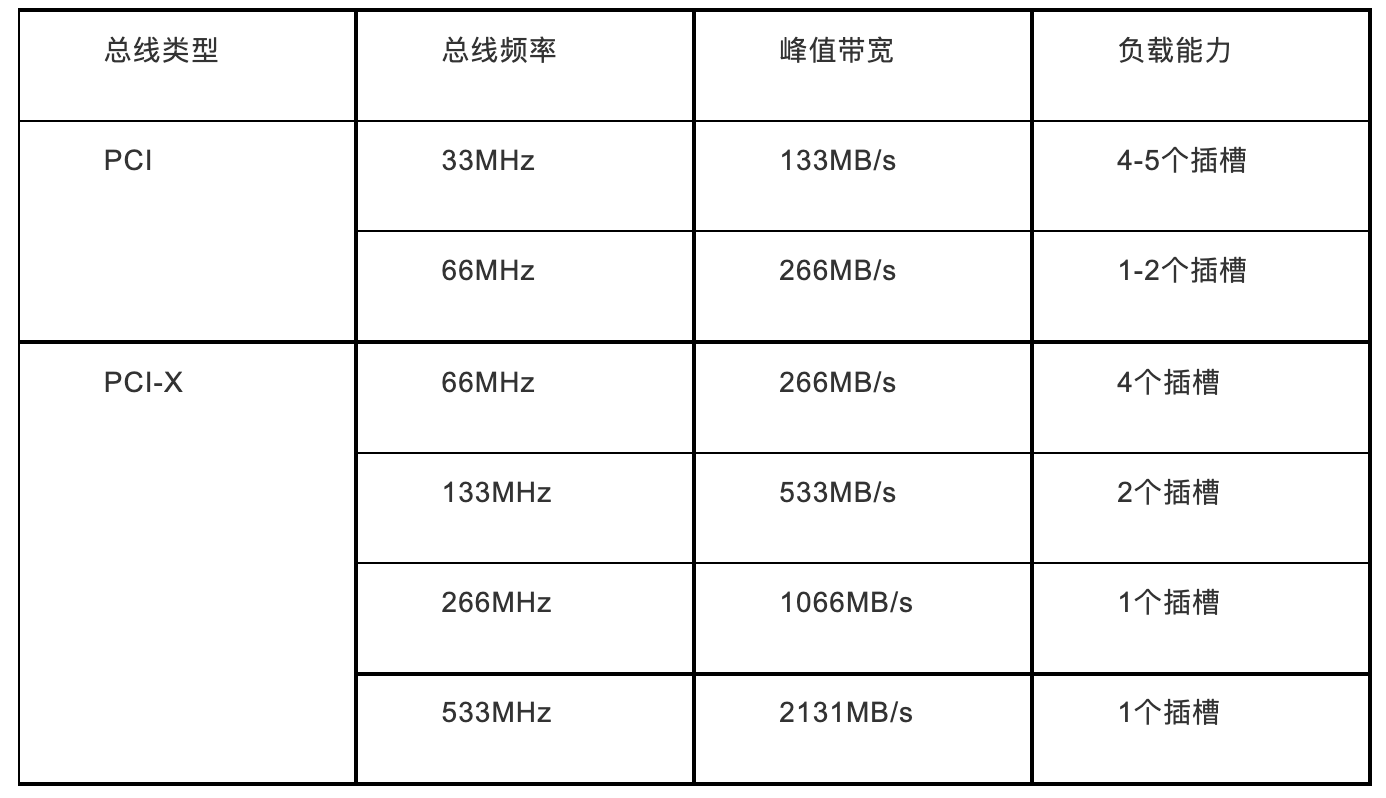

PCI总线的所能挂接的负载与总线频率相关,其中总线频率越高,所能挂接的负载越少。下文以 PCI总线和PCI-X总线为例说明总线频率、峰值带宽和负载能力之间的关系,如表1‑1所示。

表1‑1 PCI总线频率、带宽与负载之间的关系

由表1‑1所示,PCI总线频率越高,所能挂接的负载越少,但是整条总线所能提供的带宽越大。值得注意的是,PCI-X总线与PCI总线的传送协议略有不同,因此66MHz的PCI-X总线的负载数较大,PCI-X总线的详细说明见第1.5节。当PCI-X总线频率为266MHz和533MHz时,该总线只能挂接一个PCI-X插槽。在PCI总线中,一个插槽相当于两个负载,接插件和插卡各算为一个负载,在表1‑1中,33MHz的PCI总线可以挂接4~5个插槽,相当于直接挂接8~10个负载。

原出处:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA的逻辑技术专栏。