数字IC验证领域的IP指的是Intellectual Property(IP) core,VIP指的是verification Intellectual Property(IP) core.和日常听到的VIP不是一个东西,但是同样都very important。

半导体中的 Intellectual Property(IP) core是一种可重用的逻辑单元或布局设计,通常用作不同芯片设计中的积木。

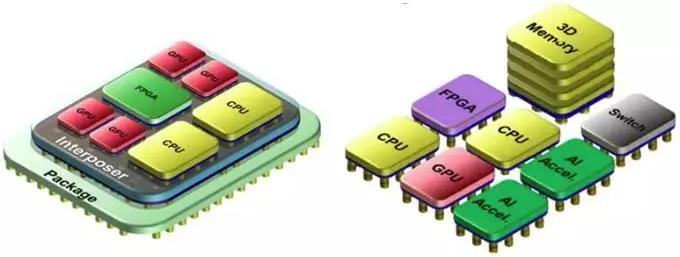

在当今的集成电路设计时代,越来越多的系统功能正在集成到单个芯片中(System on Chip/SOC)。在这些SOC设计中,这些预先设计好的IP核正变得越来越重要。这是因为大多数SOC设计都有一个标准的微处理器,许多系统功能都是标准化的。因此设计一次,可以在多个设计中重新使用。

很多组件都是标准化的协议和设计——例如ARM总线协议,Ethernet、SPI、USB、UART等。所有这些都可以独立设计为IP核,并被许可给多个不同的系统芯片设计。

IP核通常被授权为软IP核(SoftIPcores)或硬IP核(HardIPcores)。软IP核通常是可综合的RTL,例如Verilog、VHDL。有时综合后的门级网表也属于软IP核。软IP核心的优点是可以自定义布局布线。硬IP核提供的是布局布线后的格式。

一般来说,数字逻辑核被开发和授权为软IP核。serdes,PLLs, ADCorDAC, Phylayerlogicfor DDR,PCIE等模拟和混合信号逻辑通常作为硬IP核进行开发和授权。

随着基于IP的设计趋势的增加,也出现了对验证IP(VIPs)的需求。与设计IP类似,验证IP是预定义的功能块,可以插入到用于验证设计的测试平台中。

对大型SOC设计的验证通常需要占用整个项目生命周期的50%以上,并在多个验证层级完成——验证较小的逻辑块,在验证子系统,然后验证整个SOC芯片。VIP块可以作为实际设计IP的仿真模型,帮助进行所有这些级别的验证。

VIP块通常由bus functional models,stimulus generators,protocol monitors和functional coverage blocks组成。由于许多行业测试平台遵循不同的语言和方法(OVM、UVM),这些VIP通常是可配置的并易于集成到不同的验证环境中。

大多数复杂的SOC设计现在都遵循基于IP核心的设计流程和基于VIP核心的验证环境,以争取更短的上市时间。

作者:XinXinHu

原文链接:https://mp.weixin.qq.com/s/SmxrTB8oJATFprjNAVcaDw

微信公众号:

授权转自数字芯片实验室公众号,请勿二次转载。

推荐阅读

更多数字IC设计技术干货等请关注数字芯片实验室专栏。