只考虑两个“核”的场景,并且CPU中所有的初始值都是0。这里的“核”可以是不同的CPU,也可以是同一个CPU不同的进程。

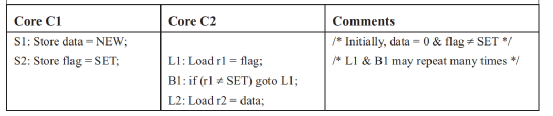

场景1(Store-store reordering):

大多数程序员都期望核心C2的寄存器r2应该得到新的值NEW。然而,在今天的某些计算机系统中,r2可以为0。实际执行顺序如下图所示:

硬件可以通过重新排序核心C1的stores S1和stores S2指令,使r2获得值0。如果我们只查看C1的执行,这种重新排序也是正确的,因为S1和S2访问的是不同的地址。

如果一个核具有非FIFO写缓冲(write buffer),发起两个store指令,如果第一个store指令在缓存中miss或者第二个store指令在缓存中hit就可能使得store指令的执行顺序重新排序。

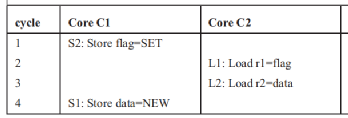

场景2(Load-load reordering.):

现代处理器的动态调度可能会使得核心C2乱序地执行loads L1和loads L2。只考虑到单核心C2线程,这种重新排序似乎是安全的,因为L1和L2是不同的地址。但是考虑到C1,如果内存操作按L2、S1、S2和L1顺序执行,则r2还是赋值为0。

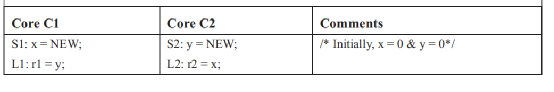

场景3(Load-store and store-load reordering):

和场景2类似,同一进程不同地址之间load指令和stores指令之间也可能会乱序.

对于上图的场景,如果发生load和store乱序,r1和r2都为0.

另外,由于S1、L1和S2、L2分属于不同的进程,还可能发生的情况有

这个问题开始变得很复杂,这不是程序员们所希望看到的。所以,具有一个明确的内存一致性模型去明确程序的行为以及可以采纳的优化手段就变得很有价值。

作者:XinXinHu

原文链接:https://mp.weixin.qq.com/s/XPlWuqhdIF7mQqO\_yvIJ\_w

微信公众号:

授权转自数字芯片实验室公众号,请勿二次转载。

推荐阅读

更多数字IC设计技术干货等请关注数字芯片实验室专栏。