本期我们基于DDR 测试方案提供商:Teledyne Lecroy 关于 DDR 调试与兼容性验证的系列讲座来学习 DDR 测试与调试相关的知识。

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

DDR 学习时间 - OpenIC SIG 开源数字IC技术分享

关于讲座

本系列基于 TL 提供的:《如何成为 DDR 物理层测试大师》系列讲座,讨论有关 DDR 调试、兼容性验证和测试等相关内容。本系列文章基于 TL 的 PPT做了一些翻译,并增加了一些笔者自己的见解。

本文所使用的文字和图片版权归 TL 所有,如有侵权,十分抱歉,还请联系我删减.

使用公司邮箱登记后既可观看视频和下载 PPT。

讲座分为四讲,分别是:

Part One: Fundamentals of DDR Memory Physical Layer Testing

Part Two: Beyond DDR Compliance Testing — Using Advanced Debug Tools

Part Three: Top Tips and Techniques for Better DDR Probing and Testing

Part Four: DDR Debug Scenarios and Virtual Probing

本期的内容来自第一讲的前半部分。

DDR 接口与测试基础知识

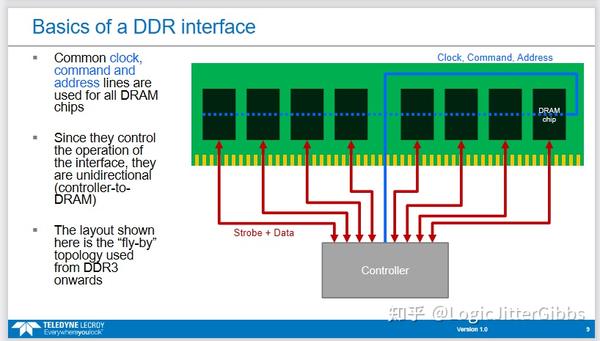

DRAM 总线由两部分组成,分别为数据/命令地址时钟总线

- DRAM 数据(DQ)总线是双向的

- DRAM 数据总线上有效的数据使用 Strobe 信号表示

- 每个 DRAM 芯片和控制器之间的信号连接是独享的

- DRAM 地址、命令和时钟总线(CA)是单向的

- 所有 DRAM 共享 CA 总线

- 从 DDR3 时代开始,引入了一种名为 fly-by 的多芯片 CA 连接方式(即依次进入并穿过多个芯片,如图中蓝线所示)

对于 DDR 测试来说,有三个关注的角度:

- 兼容,DRAM 颗粒发出/接收的信号是否符合 JEDEC 标准

- 功能验证,DRAM 颗粒和系统之间交互是否正确,即单次和连续读写是否正确

- 调试,很急,为什么我的系统和 DRAM 颗粒之间没有正常工作?

DDR 测试信号

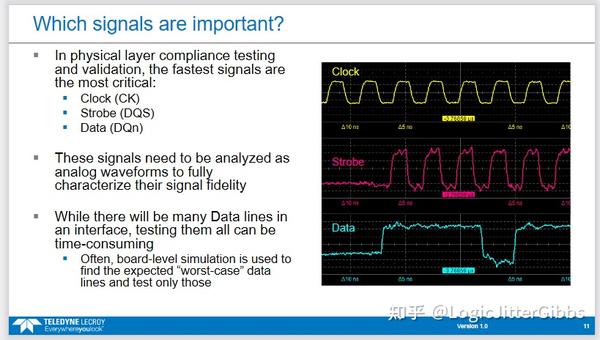

物理层测试中重要的信号,一般都是比较快速的信号,总共有三类

- 时钟信号 (CK)

- 数据有效信号(DQS)

- 数据(DQn)

这些信号都需要以模拟信号的方式进行分析,考量他们的信号质量

这些信号的数量比较多,一一分析需要花很多时间。而一般在板级仿真中,只会考察最 worst 的情况。

数据信号线可能是 16/32/64 根,那么 DQS 及和它差分的 DQS\_n 就是 4/8/16 根,每 8 根信号线 DQn 对应一对 DQS/DQS\_n。

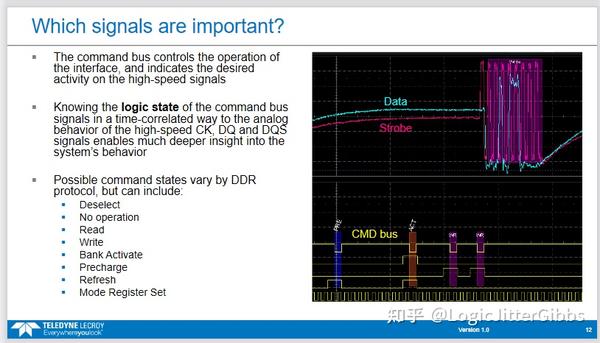

DRAM 的命令总线(如 WE\_n,CAS\_n,RAS\_n 等信号)控制了接口的行为,比如进行写或者读操作。

将命令总线和模拟信号对应起来观察对于调试是很重要,比如上图中,将一条写命令 WR 和跟随其后的写数据放在一起进行观察。

完整的 DDR 测试系统

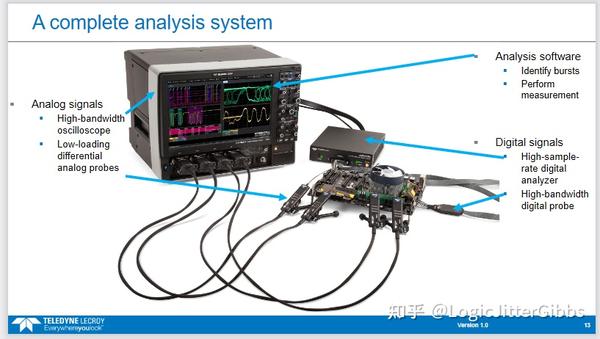

这里是厂商的广告时间,推荐了他们家的 DDR 测试系统,测试系统由几个部分组成。

(看上去好帅有没有)

- 模拟信号

- 高速示波器

- 低负载差分探头

- 模拟信号分析软件

- 识别 DRAM Burst

- 性能分析

- 数字信号

- 高速采样的信号分析仪

- 高速数字接口

这套设备看上去,各个部件都写着:Much US Dollar 啊!

DDR 测试中的挑战

接下来讨论 DRAM 测试中的两项主要挑战

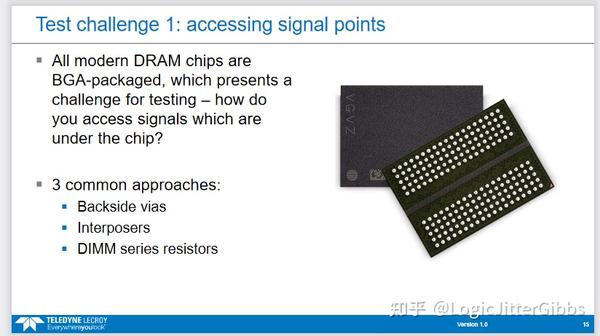

挑战 1 是如何将探头附着到 DRAM 芯片的引脚上去。

我们知道现在所有的 DRAM 采用的都是 BGA 封装,引脚都在芯片下方,焊接到 PCB 后我们是没有办法直接把探头连接到引脚上去的。

目前主要有三种测试的方法,分别是

- 背部过孔

- 转接板

- DIMM 串行电阻

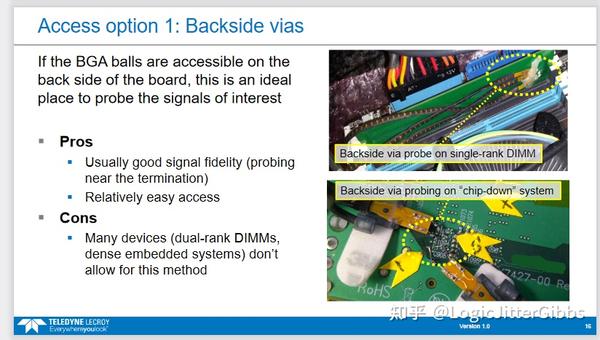

背部过孔是指在设计 PCB 时,在 DRAM 芯片背面预留过孔(via),将 DRAM 引脚的焊盘连接到 PCB 背面的过孔上。观测时,将探头连接到过孔上,从而连接到 DRAM 芯片引脚和焊盘上。

这种方式的好处是信号的质量比较好,因为观测点距离 DRAM 引脚的距离很短。另外,也方便连接探头。

缺点是有些 DRAM,比如双层的 DIMM 内存条,DRAM 芯片的背面还是 DRAM 芯片,没法用这种方式进行观察。

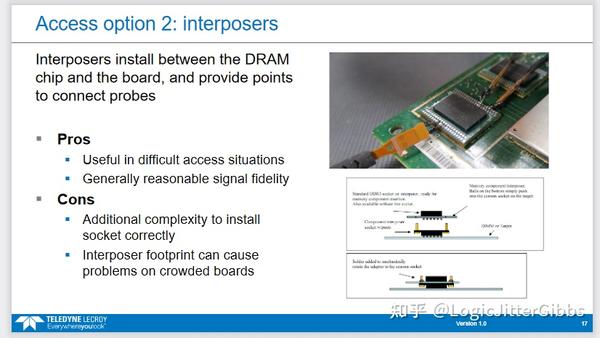

第二种方法是用一块小转接板,DRAM 先焊接到转接板上,再把转接板焊接到 PCB。通过转接板预留的触电,可以方便地进行观测。

这种方式地优点是适合大多数场景,并且通过使用良好 SI 设计的转接板,可以保证观测信号的质量。

缺点是使用转接板给系统增加了复杂度(比如,故障有没有可能是转接板导致的?),并且在一些布局非常密的 PCB 上,是连放下一个转接板的地方都没有的。

第三种方法是 DIMM 内存条专用的,可以将探头连接到金手指和 DRAM 芯片之间的串行电阻上。这种方法的缺点是探头与DRAM 的终结电阻的距离,可能导致比较大的信号反射。

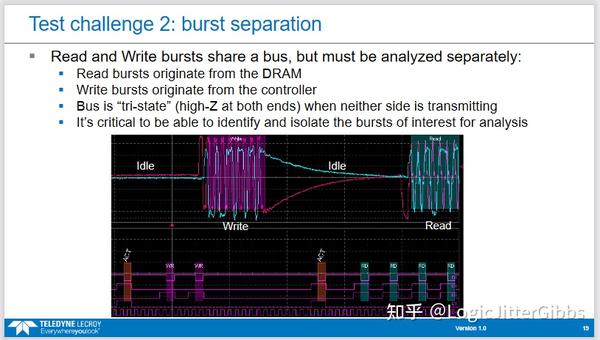

DDR 测试的第二项挑战是如何区分开不同的传输 Burst,以方便观测。

DDR 的数据总线是双向的,我们需要在观测时区分读和写的传输操作

- DDR 的写操作是由控制器驱动的

- DDR 的读操作是 DRAM 芯片驱动的

- 在两者都不驱动总线时,总线保持高阻状态

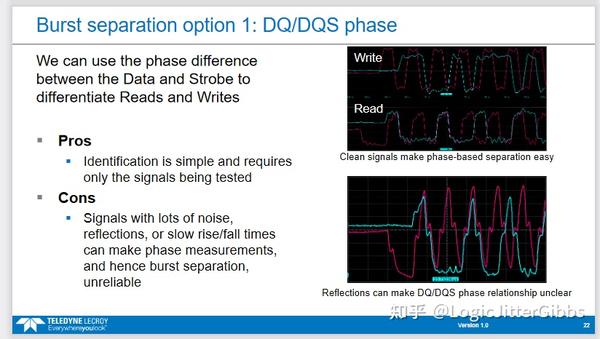

一种方式是通过观测 DQS 和 DQ 数据边沿的关系进行区分:

- 写操作时,DQS 由控制器发出,边沿对齐数据 DQ 两个边沿之间的中间位置

- 读操作时,DQS 由 DRAM 芯片发出,边沿和 DQ 的边沿对齐

但是在信号噪声和反射较大的情况下,DQS 和 DQ 的边沿关系将会变得不明确,仅通过这种方式较难区分出不同的读写 Burst。

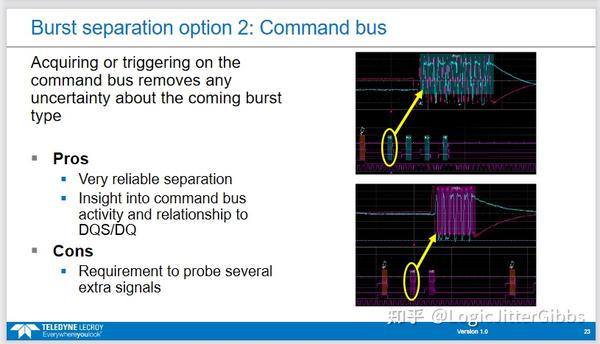

如果能将模拟信号和数据信号对应起来,那么做到这一点也就很简单了。

通过额外的数字信号设备采集 DRAM 的命令总线,根据命令的类型,就可以明确地区分当前 burst 的读写属性。

当然,这样的话你必须得花一些额外的小钱钱了。

结语

本期我们讨论了几个简单的知识点,

- DRAM 测试基础知识

- DRAM 测量信号

- DRAM 测试系统

- DRAM 测试中的两项挑战

后续文章我们会继续跟随讲座讨论以下内容:

- DRAM 测试准备项

- DRAM 兼容性测试

- Case study : DDR 验证与调试

转载自:知乎

作者:ljgibbs推荐阅读

更多招聘及面经请关注FPGA的逻辑。