一个验证平台至少需要完成两类激励模型:

1、主动驱动DUT,例如时钟和复位。复杂的DUT激励还会包含一些对于激励的开关控制以达到各种边界场景,这个组件称之为initiator (在UVM当中是active agent)。

2、被动响应DUT,对于DUT的输出返回一些必要的数据,这个组件可以称之为responder (在UVM当中是passive agent)。

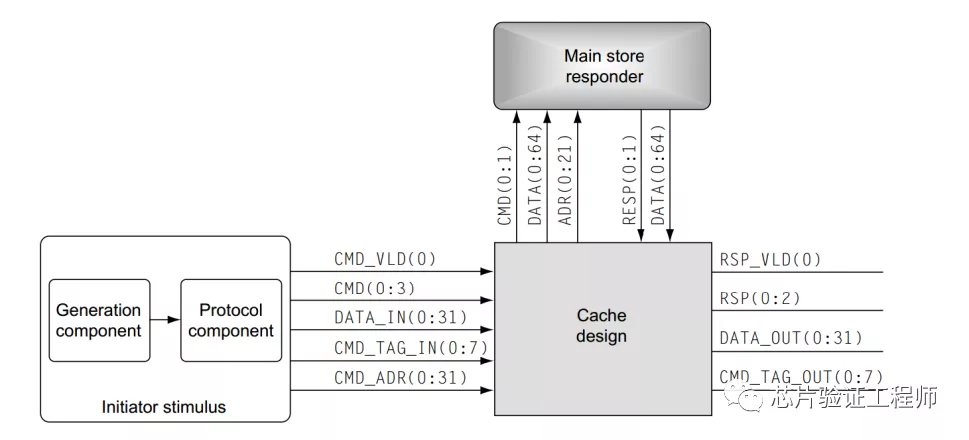

上图中cache design就是一个待测设计,其中左边组件发送激励,上边组件被动响应DUT的输出,在cache miss时从主存中读取数据。

Initiators

所有的验证环境都需要模拟最基本的接口协议信号,这需要验证工程师非常熟悉相应的接口协议。

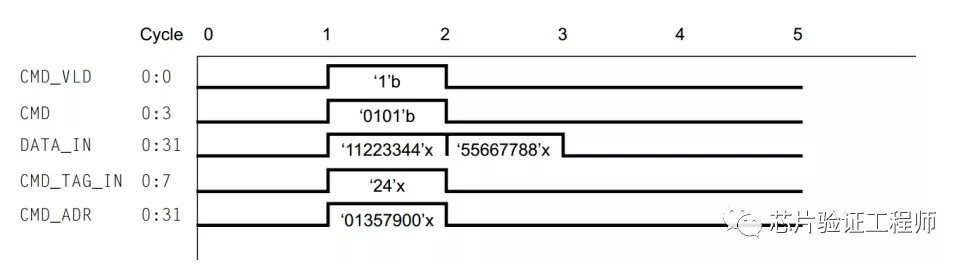

如上图所示,验证工程师建模的激励行为需要满足协议要求,但不能够过约(戴着脚镣跳舞)。除了接口协议之外,验证工程师在编写测试用例的时候还需要知道DUT实时的状态,这可以通过两种方式实现:

1. 验证工程师已知设计规格建模局部设计的行为。

2. 设计工程师向验证工程师提供一个信号,例如“active,busy”,可用于判断测试用例是否可以结束.

大多数DUT的激励都比较复杂,存在多个接口的并发或者具有更复杂的激励控制,所以需要实现接口协议(总线参考模型,BFM)和激励序列的解耦。这种功能的解耦是简化验证环境非常重要的基本思想,其有两大好处:

1、使得验证工程师更加关注功能的验证,而不是底层验证环境的搭建。当然,如果只会编写测试用例,验证工程师会觉得自己螺丝钉化。

2、方便组件在各模块之间以及项目之间复用。例如,某个接口从APB读写替换成AHB读写,测试用例序列不用更改,只修改底层信号级驱动即可。

这也是现在验证平台成为“基于事务的验证”的原因,验证的激励就是通过受限随机或者定向的方式发送所有类型的事务。

responder

第二种激励的类型是对DUT的被动响应,即对DUT的输出做出反应,并将激励反馈回DUT。

同样以上图中cache设计为例,其中的主存模型就是一个responder激励类型,只会被动地对设计的输出进行响应,而不能主动地发起任何行为。

END

作者:验证哥布林

原文链接:https://mp.weixin.qq.com/s/MWzlxmYgV29YukkDfxYcvw

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。