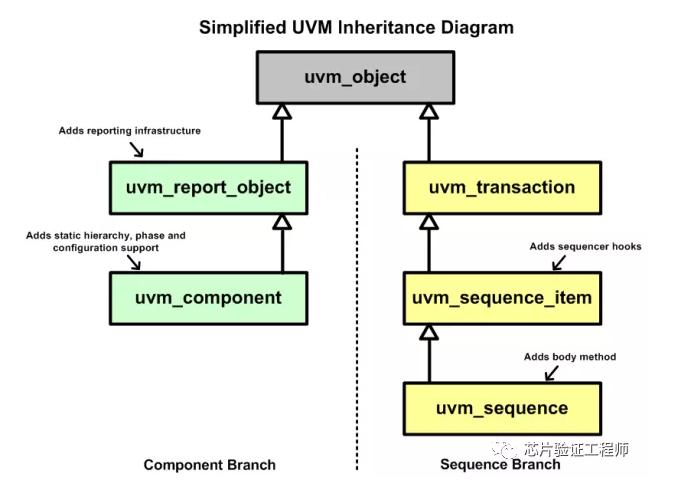

一个UVM testbench是由从uvm_component基类扩展出来的对象构建的。当创建一个uvm_component对象时,它将成为testbench 层次结构的一部分,并在仿真期间保持不变。

与此不同的是,uvm sequence 类层次结构分支中的对象是短暂的,即在仿真过程中它们会被创建,使用,然后内存回收。

uvm_component静态层次结构由一个链表表示,该链表在创建每个组件时构建,层次结构中的组件位置由传递给其create 方法的参数决定。

例如,在spi_env中创建一个apb_agent组件,那么到apb_agent的层次结构路径将是“uvm_test_top.m_env.m_apb_agent”。

class spi_env extends uvm_env;

apb_agent m_apb_agent;

function void build_phase(uvm_phase phase);

m_apb_agent = apb_agent::type_id::create("m_apb_agent", this);

endfunction: build_phase

endclass: spi_envuvm_component类继承自uvm_report_object,其中包含支持UVM消息传递所需的功能,可将组件的路径添加到report字符串信息中。

uvm_component基类针对每个UVM Phases都有一个虚拟方法,这些方法会根据需要重载,如果没有实现相应phase的虚拟方法,那么该组件就不参与该phase。

为了提供testbench 组件构建和配置的灵活性,可以将uvm_components注册到UVM factory中,其可以支持将该组件替换为派生类型。

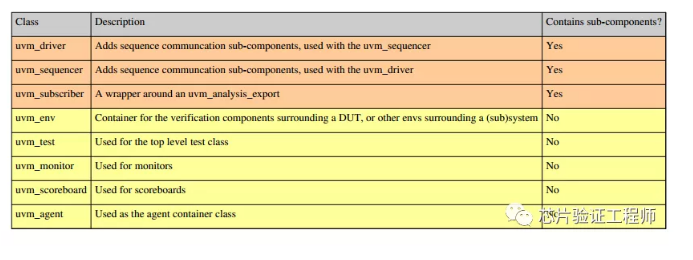

UVM package 包含了很多对uvm_component的扩展,但是这些扩展大多非常薄,可能仅仅只是代表不同的组件类型。下表总结了一些uvm_component派生类。

作者:验证哥布林

原文链接:https://mp.weixin.qq.com/s/AnF9oOsyNwWLQ0sZtcrBWQ

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏