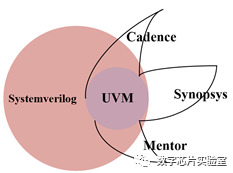

UVM提供了丰富的基类库和验证方法学,并且被主流的EDA工具、IP供应商和设计公司采用。现在,使用SystemVerilog基本上等同于使用UVM验证。

如果你要问我,SystemVerilog和UVM到底是啥关系,我觉得汉字和诗的比喻也许比较恰当。我自然不会说是code language和library的关系,太没有想象空间。

当天空下雪了,

SystemVerilog+UVM:忽如一夜春风来,千树万树梨花开。

Only UVM:thousands of pear flowers bloom as if spring wind just passed by

Only SystemVerilog:“风景美如画,吟诗赠天下。奈何没文化,卧槽雪好大”。

SystemVerilog是一种硬件设计和验证语言(hardware design and verification language,HDVL),Verilog HDL的升级版。

为了更好地支持验证环境,SystemVerilog提供了面向对象编程(OOP)的能力、受约束随机激励、断言和功能覆盖率等特性。

,由于工具,你可以专注在更重要的事情上。

在复杂验证环境搭建的过程中,仅仅使用SystemVerilog已经无法满足验证需求,这时候就需要基类库(base class libraries)、**工具包(toolkits)或者说方法学(methodology guidance)**的支持,提高验证平台搭建效率。

关于验证平台需要基于UVM的最主要的原因就是:复用(reuse)

1、 工具之间复用

SystemVerilog语言参考手册超过1300页,Cadence、Synopsys和Mentor等主流EDA工具在具体实现时存在差异,但在支持UVM时保持一致,也就是说基于UVM的验证环境可以在不同EDA工具之间移植。

2、 项目之间复用

基于UVM的验证环境很容易项目之间复用,同时工程师之间对于验证环境也容易达成共识。这是仅仅使用SystemVerilog语言无法做到的。

3、 验证IP的复用

在SoC设计中存在很多标准协议,AMBA、DDR和Ethernet等。UVM还能方便VIP的复用和维护。

4、解决方案的复用

验证和其他软件开发一样,存在几乎每个项目遇到的问题。UVM提供现成的解决方案实现。

下面介绍UVM中的一些关键概念:

1、Components&Data

UVM中的类主要分为两类:Components和Data。

Components继承自uvm\_component,Data继承自uvm\_sequence\_item。

uvm\_component和uvm\_sequence\_item都继承自uvm\_object。

Components在仿真开始消耗时间之前的0时刻(build\_phase)创建。用户在继承了Components之后,覆盖build\_phase方法即可。

build\_phase这种phase callback是top-down的。可以看出来UVM的Components是一个树形结构,根节点只有一个uvm\_root(singleton object)

Data在仿真过程产生的,像数据流一样流过各个Components。

2、factory机制

使用面向对象编程技术用户可以很容易地基于基类创建新的验证组件并且利用OOP的继承特性以通用方式操作用户定义的对象。例如,在基本的数据事物类的基础上进行错误注入。

为了充分利用这种OOP在验证平台中的灵活性,有必要利用factory机制这个设计模式在验证过程中实现类的替换。

class user_monitor extends uvm_monitor;

`uvm_component_utils(user_monitor)

...3、configure&resourcedatabase

configure可以看成是一个全局可以访问的,使用字符串名称进行检索的数据资源。可以根据数据值配置相应的验证平台。

4、TLM connection

对于组件,需要在build\_phase自上而下地完成实例化,对于组件之间的连接需要在connect\_phase自下而上地完成TLM连接,用于数据流的发送和接收。

Reference:

[1] IEEE Standard 1800-2012 for SystemVerilog Hardware Design and Verification Language

[2] SystemVerilog for Verification

[3] Design Patterns: elements of reusableobject-oriented software

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/5p4LbSV6j1bojzPdj_JW4Q

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏