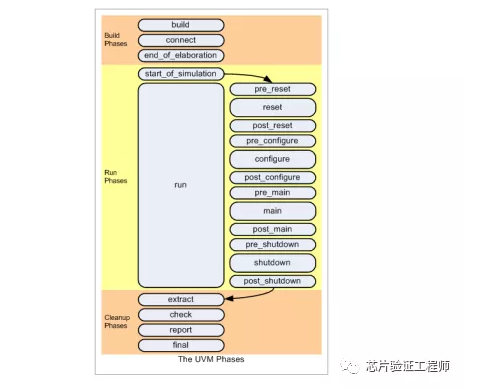

“phase”是UVM主要的特性之一,其目的是为了统一testbench执行流程。UVM中的phase主要分为3类,即按顺序执行build phase、run-time phase和clean up phase。

1.Build phases-构建和配置testbench;

2.Run-time phases-在testbench上运行test case(会消耗仿真时间);

3.Clean up phases-在该阶段报告test case的结果。

上述解释只是推荐的用法,我们可以在不同的phase做我们期望的任何事情,只要我们清楚它们的执行顺序即可,例如我们可以在Clean up phases执行一些testcase结束后的DUT状态检查。

uvm_component基类包含不同pahse的虚拟方法,这些方法由testbench创建者自行填充。在这里就体现了使用UVM的好处了,即各个验证组件独立开发并基于相同的共识相互配合。

要启动UVM testbench,必须在顶层initial语句块调用run_test()方法。调用run_test()会构造UVMtestbench根组件,然后启动UVMphase。run_test()方法可以传递一个字符串参数用作testbench层次结构的根节点。为了将testcase组件“my_test”指定为UVMtestbench根组件,Questa命令行将是:

vsim tb_top +UVM_TESTNAME=my_test下面将概述每个UVMphase的用途:

Build Phases

build phases在UVM testbench仿真开始时执行,其总体目的是构建、配置和连接测试台组件层次结构。所有的build phases方法都是functions ,在0仿真时间执行完成。一旦构建了UVMtestbench 根节点组件,build phase就开始执行。它从上到下地构建testbench 组件层次结构。

Connect Phases

connect phase用于在组件之间建立TLM连接,或向testbench 资源池分配对象句柄(例如virtual interface)。connect phase在build phases方法之后自底向上地执行。

end\_of\_elaboration Phases

end\_of\_elaboration phase 用于在仿真开始之前对testbench 的结构、配置或连接进行最终调整或者检查。

Run Time Phases

在start_of_simulation phase之后,UVM并行执行run phase和pre_reset phase到post_shutdown phase。run phase存在于OVM中,并被保存下来,以便OVM组件能够很容易地迁移到UVM中。其他的Run Time Phases被添加到UVM中以提供更细粒度的运行控制。

start_of_simulation Phases

start_of_simulation phase 是在testbench 的耗时部分开始之前发生的一个function 。它旨在用于自下而上地显示信息(例如testbench拓扑结构、组件配置信息等 )。

run Phases

run phase发生在start_of_simulation阶段之后,用于激励的产生和testbench的监测和检查。run phase作为一个task实现,所有uvm_component的run phase都并行执行。drivers 和monitors 总是会使用这一phase。

pre_reset phase

reset phase

post_reset phase

pre_configure

configure

post_configure

pre_main

main

post_main

pre_shutdown

shutdown

post_shutdown中的任何动作都可以在run phase或者其他任何一个消耗仿真时间的run time phases中执行

Clean Up Phases

clean up phases 用于从scoreboards 和functional coverage monitors中提取信息,以确定testcase是否达到其覆盖目标。clean up phases是functions ,所以也不会消耗仿真时间。同理,extract phase、 check phase、 report phase和 final phase都可以在同一个function phase中完成。

嗨,有时候划分的粒度太细也不好,作为一个UVM用户,我们需要理解自己的本质需求,然后对标准的UVM testbench进行裁剪。

作者:验证哥布林

原文链接:https://mp.weixin.qq.com/s/MNJ8f1g1C52TFJ2j68Lpsg

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏