优秀的 Verilog/FPGA开源项目介绍(三)- 大厂的项目

谷歌开源芯片项目OpenTitan

OpenTitan 是 Google 开发的项目,旨在鼓励厂家为数据中心和消费级设备开发所谓的信任根(root-of-trust)技术。

如果一个系统被称为拥有信任根,这意味着它有专门的芯片或模块负责阻击黑客攻击。比如说,在谷歌的最新Pixel 4手机中,Titan M微控制器扮演这个角色。这是一个微型处理器(如图所示),每当用户打开手机,它就会验证固件的完整性。

与此同时,在数据中心中,信任根常常是所谓的硬件安全模块,这种专用设备可以“妥善保管”服务器用于加密敏感数据的加密密钥。硬件安全模块与网络的其余部分隔离开来, 常常放在防篡改的地方。实际上,所有超大规模云提供商以及思科和HPE等知名数据中心基础设施供应商都有各自的信任根技术,不过据谷歌及合作伙伴声称,问题恰恰出在这里。

谷歌云OpenTitan负责人Dominic Rizzo说,硅片信任根是“一个高度专有化的领域。因此,我们所做的就是开放一切,那样你就可以在硬件的最低层确保安全,而不用盲目信任专有设计……我们认为,透明性是安全的立足之本。”

OpenTitan信任根技术可以用于众多硬件,包括主板、网卡、路由器、物联网设备、移动及消费级设备、机器学习系统及其他设备。

谷歌称,OpenTitan基于三个关键原则:任何人都能够检查硅片信任根,并为之贡献代码;通过提供一种不受供应商锁定影响的逻辑上安全的开放设计,提高灵活性;以及高质量,不仅设计本身确保了质量,还通过参考固件和文档确保了质量。

谷歌希望借助OpenTitan,可以为业界提供用于开发信任根产品的通用技术基础模块。这家搜索巨头目前正在为使用流行的RISC-V架构的这个项目开发专用芯片设计。其他许多组件或部件也正在开发中,包括固件、经过优化以处理加密任务的协处理器以及用于创建加密密钥的物理随机数生成器。

官网链接:www.opentitan.org

文档链接:https://docs.opentitan.org/

https://github.com/lowRISC/opentitan

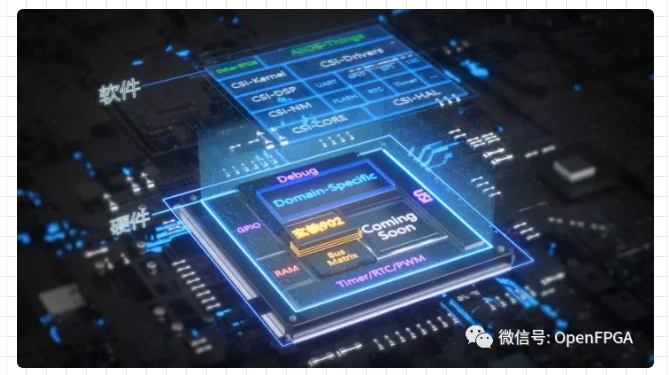

阿里(平头哥)的 AloT 芯片平台无剑100

平头哥无剑100

文档目录如下:

|--Project //open source project work directory

|--riscv_toolchain //tool chain install directory download from t-head.cn

|--wujian100_open //wujian100_open project get from github

|--case //test case example for simulation

|--doc //wujian100_open user guide

|--fpga //FPGA script

|--lib //compile script for simulation

|--regress //regression result

|--sdk //software design kit

|--soc //Soc RTL source code

|--tb //test bench

|--tools //simulation script and setup file

|--workdir //simulation directory

|--LICENSE

|--README.mdhttps://github.com/T-head-Semi/wujian100\_open

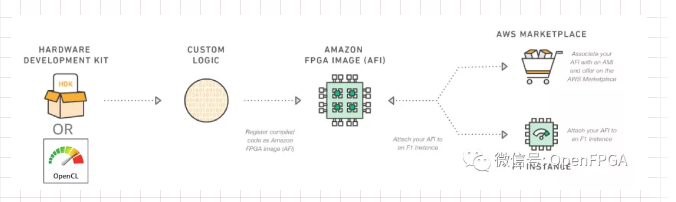

亚马逊aws-fpga

AWS EC2 FPGA 开发套件是一套开发和运行时工具,用于在Amazon EC2 F1 实例上开发、模拟、调试、编译和运行硬件加速应用程序。它分布在此 github 存储库和AWS 提供的FPGA Developer AMI - Centos / AL2 之间,无需任何开发工具成本。

⚠️ 注意:开发工具包仅支持 Linux 操作系统。

开发流程

创建 FPGA 设计(also called CL - Custom logic)后,开发人员可以创建 Amazon FPGA 映像 (AFI) 并将其轻松部署到 F1 实例。AFI 是可重用、可共享的,并且可以以可扩展和安全的方式进行部署。

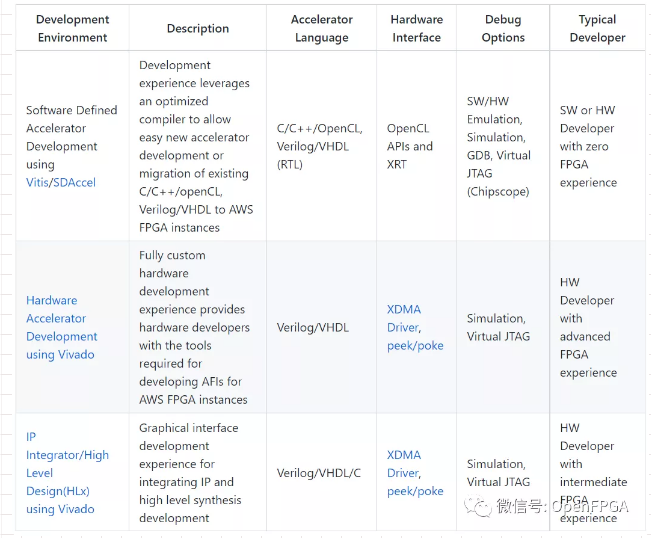

开发环境

https://github.com/aws/aws-fpga

NVIDIA Deep Learning Accelerator

https://github.com/nvdla/hw

https://github.com/openDLA

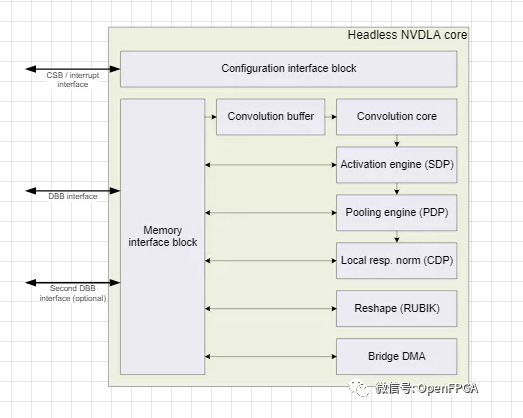

深度学习开源项目。NVIDIA深度学习加速器(NVDLA)是一种自由开放的体系结构,它促进了设计深度学习推理加速器的标准方法。凭借其模块化架构,NVDLA具有可扩展性,高度可配置性,并旨在简化集成和可移植性。

架构如下:

目录结构

该项目包含与 NVDLA 硬件版本相关的 RTL、C 模型和测试平台代码。在此存储库中,您将找到:

vmod/ -- RTL 模型,包括:

vmod/nvdla/ -- NVDLA 的 Verilog 实现

vmod/vlibs/ -- 库和单元模型

vmod/rams/ -- NVDLA 使用的 RAM 行为模型

syn/ -- NVDLA 合成脚本示例

perf/ -- NVDLA 的性能估算器电子表格

verif/ -- 用于基本健全性验证的跟踪播放器测试平台

verif/traces/ -- 与各种网络相关的样本跟踪

tool——用于构建 RTL 和运行模拟/综合等的工具。

spec -- RTL 配置选项设置。目前我了解的就是上面这些项目,总体来说,在完整性、实用性及先进性(各个先进领域)等各方面都处于比较领先的地位,但是有些项目可能过于复杂,不太适合新手直接入门,需要在一定领域内有深入了解后才能理解。但是这些大厂的开源项目,代码部分可以学习借鉴,尤其一些代码规范。

百度Paddle Lite

Paddle Lite是一个高性能、轻量级、灵活性强且易于扩展的深度学习推理框架,定位于支持包括移动端、嵌入式以及服务器端在内的多硬件平台。

当前Paddle Lite不仅在百度内部业务中得到全面应用,也成功支持了众多外部用户和企业的生产任务。

Paddle Lite支持基于arm的FPGA zu3/zu5/zu9的模型预测,提供armv8的交叉编译

PaddleLite通过调用底层驱动实现对FPGA硬件的调度,目前只支持百度Edgeboard开发板

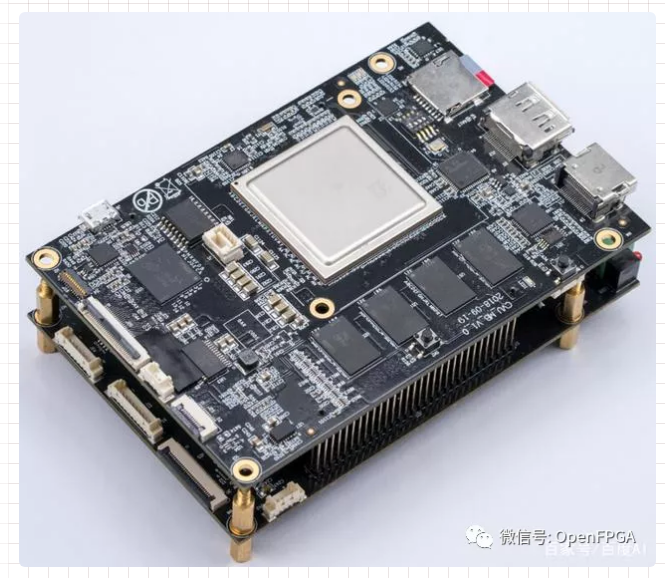

米尔科技

米尔科技

黑金

https://paddlelite-data.bj.bcebos.com/doc\_images/FPGA\_demo/soft\_arch.png

Lite实现FPGA简介

Lite支持FPGA作为后端硬件进行模型推理,其主要特性如下:

PaddleLite FPGA版本支持原生 fluid 模型,无须使用opt工具进行格式转化。

Lite中FPGA的kernel(feed、fetch除外)均以FP16、NHWC的格式作为输入输出格式,所有的weights和bias仍为FP32、NCHW的格式,feed的输入和fetch的输出均为FP32、NCHW格式的数据,在提升计算速度的同时能做到用户对数据格式无感知

对于FPGA暂不支持的kernel,均会切回arm端运行,实现arm+FPGA混合布署运行

目前FPGA成本功耗都较低,Lite基于FPGA的模型性能远远好于arm端,可作为边缘设备首选硬件

已验证Paddle模型

分类网络:

MobileNet 系列

MobileNetV1

MobileNetV2

ResNet 系列

ResNet18 ResNet34 ResNet50 ResNet101 ResNet152 Res2Net50

SE-ResNet

ResNext 系列

ResNext50 ResNext101

SE-ResNext

Inception 系列

InceptionV3

InceptionV4

检测网络:

SSD系列主干

Mobilenet-SSD

VGG-SSD

ResNet-SSD

YOLO-V3 系列主干

Darknet50

MobileNet-V1

ResNet

tiny_yolo

https://github.com/PaddlePaddle/Paddle-Lite

原文:FPGA 的逻辑

作者:碎碎思

相关文章推荐