最近听到粉丝说没有项目可以实践。作为处芯积律公众号的粉丝怎么能没有项目呢?今天我和大家分享一个之前谈过的开源项目,能不能吃得下来看你自己了。

Efabless这是一家芯片设计服务公司,这家公司比较有意思的是在google的赞助下发起了一个叫Open MPW Shuttle Program的项目,这个项目是为一些完全开源的芯片设计提供流片的机会。这对一些想学习芯片设计验证知识相关的人来讲吸引力还是蛮大的,有点像我们国内的一生一芯计划。

当然也不是任何人都能参加这个项目,要想搭上流片的便车还需要满足一些条件,比如必须采用SkyWater 的Open PDK(130nm),项目必须在GitHub上公开等。对于其他的一些条件感兴趣的朋友可以在他们网站搜索。

我们今天主要看看他的一些开源项目。

前面我有篇文章提到的Raven项目就是他们的作品之一。

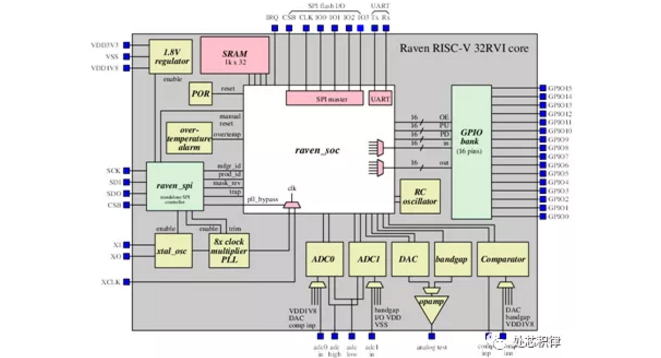

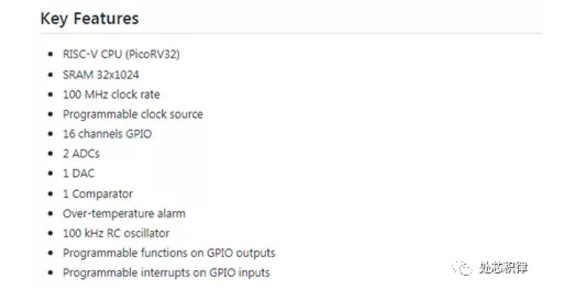

Raven这是一款开源的SOC芯片,这款芯片的主要功能见下图。

这个开源半导体项目使用基于开源工具的Efabless设计流程,在不到三个月的时间里就实现了从设计开始到完成。

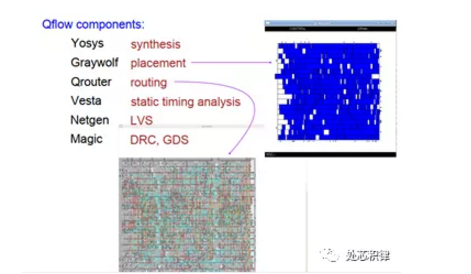

Raven完全由开源EDA进行开发然后实行流片。这里的仿真,综合,布局布线,静态时序分析等等都是由开源软件完成。

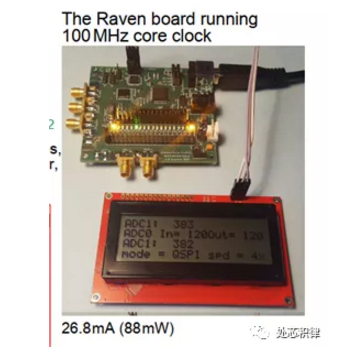

Efabless已经成功地在100MHz下对Raven进行了测试,该设计理论上应该能够在高达150MHz的频率下运行。

如果作为学习的话,Raven这是一款非常好的项目。

该项目的GitHub链接为:

https://github.com/efabless/raven-picorv32

除了这个项目,我也稍微看了下efabless上其他的项目,数了数居然有100多个,项目涉及RISCV,FPU,AES,以及诸多的模拟项目。

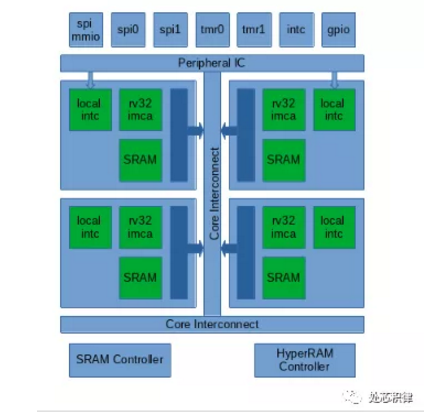

如果你对多核感兴趣,那么下面这个clusterv-soc一定适合你。不过我看了一下他的git库,只有verilog源代码,对于仿真环境目前还没加进去。

该项目的Github 链接:

https://github.com/mballance/clusterv-soc

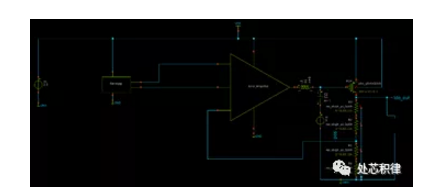

如果你对模拟芯片项目感兴趣,那么LDO应该能满足你的要求。这个项目的资料比较全。

该项目的GitHub链接为:

https://github.com/mabrains/caravel_user_project_ldo

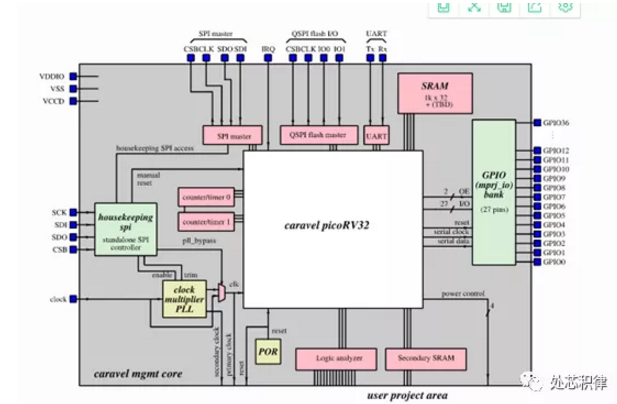

如果你嫌弃raven还不够复杂的话,那么caravel一定能满足你对复杂性的要求。caravel相较于Raven外设更多,核也替换掉了。

下面网址是对这个项目的介绍:

https://caravel-harness.readthedocs.io/en/latest/description.html#

这个项目的github链接为:

https://github.com/efabless/caravel/tree/master

其他更多项目大家可以在下面网址进行查看。

https://efabless.com/projects/shuttle_name/2106Q

以上是本期文章的所有内容。文章最后送给大家一份福利,回复“Raven”将获得一份介绍Raven 如何用开源软件跑flow的资料,感谢大家关注处芯积律。后续我继续分享介绍那些有意思的开源项目。

作者:IC bug 猎人

原文链接:https://mp.weixin.qq.com/s/J42b7cDyxdYocxZiZktPKA

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。