优秀的 Verilog/FPGA开源项目介绍(五)- USB通信

USB是我们生活中非常非常常见的接口,鼠标、键盘以及常见的U 盘等,可以说现在的USB设备已经渗透到生活中的方方面面,下面就介绍几个开源的USB IP,供大家学习。

0-官方网站

https://www.usb.org/

很多人花各种XX币下载各种标准,其实太浪费时间和精力了,这里介绍一个网站--usb.org。

USB Implementers Forum, Inc. 是一家非营利性公司,由开发通用串行总线规范的公司集团创立。USB-IF 的成立是为了为通用串行总线技术的进步和采用提供支持组织和论坛。该论坛促进了高质量兼容 USB 外围设备(设备)的开发,并促进了 USB 的优势和通过一致性测试的产品质量。

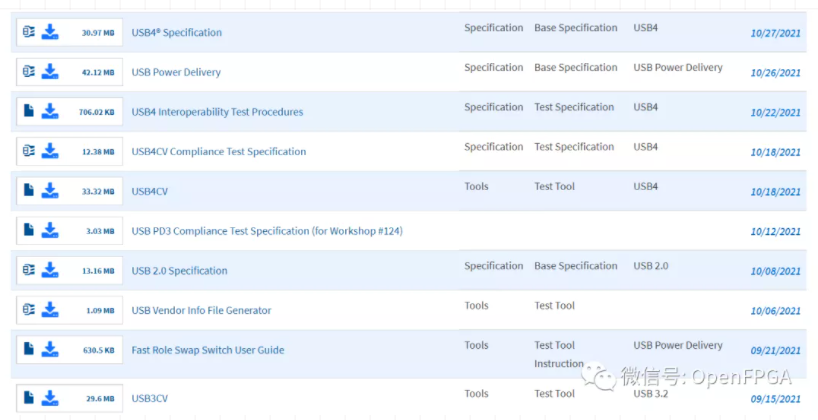

网站上的文档:

1-usbcorev

项目地址

https://github.com/avakar/usbcorev

项目简介

该IP可以将全速 (12Mbps) USB 2.0 设备内核嵌入到 FPGA 设计中。

接口部分

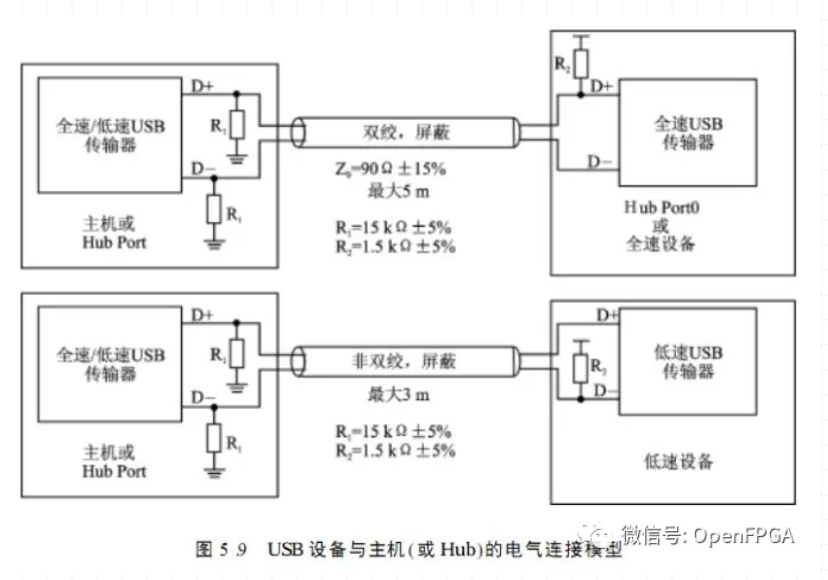

我们知道USB接口使用了差分结构,所以接口部分还是很复杂的。

由于 USB 在其半双工差分线上使用了一些奇怪的信号,因此需要做一些工作才能将其连接到核心。以下五个信号连接到USB 信号的 D+ 和 D- 。

- input rx_j -- D+/D-线上的微分值

- input rx_se0 -- 单端零检测:应在 D+ 和 D- 线均为零时设置

- output tx_se0-- 在两条 USB 线上传输零;优先于tx_j

- output tx_j-- 传输tx_j到 D+ 和~tx_jD-

- output tx_en -- 启用发射器

如果使用的 FPGA 没有差分接收器,那么可以简单地使用两个引脚并按如下方式连接它们。但是,如果没有差分接收器,这将超出 USB 规范。

inout usb_dp;

inout usb_dn;

// ...

wire usb_tx_se0, usb_tx_j, usb_tx_en;

usb usb0(

.rx_j(usb_dp),

.rx_se0(!usb_dp && !usb_dn),

.tx_se0(usb_tx_se0),

.tx_j(usb_tx_j),

.tx_en(usb_tx_en));

assign usb_dp = usb_tx_en? (usb_tx_se0? 1'b0: usb_tx_j): 1'bz;

assign usb_dn = usb_tx_en? (usb_tx_se0? 1'b0: !usb_tx_j): 1'bz;对于 Xilinx Spartan 6 系列,使用四个物理引脚如下。

// These pins are configured as differential inputs. Unfortunately,

// you can't use single-ended receivers nor transmitters on these pins.

input usb_sp;

input usb_sn;

// These pins are single-ended inouts.

inout usb_dp;

inout usb_dn'

// ...

IBUFDS usb_j_buf(.I(usb_sp), .IB(usb_sn), .O(usb_rx_j_presync));

synch usb_j_synch(clk_48, usb_rx_j_presync, usb_rx_j);

synch usb_se0_synch(clk_48, !usb_dp && !usb_dn, usb_rx_se0);

wire usb_tx_se0, usb_tx_j, usb_tx_en;

usb usb0(

.rx_j(usb_rx_j),

.rx_se0(usb_rx_se0),

.tx_se0(usb_tx_se0),

.tx_j(usb_tx_j),

.tx_en(usb_tx_en));

assign usb_dp = usb_tx_en? (usb_tx_se0? 1'b0: usb_tx_j): 1'bz;

assign usb_dn = usb_tx_en? (usb_tx_se0? 1'b0: !usb_tx_j): 1'bz;注意接收器之后的同步。

无论在哪个引脚上传输,都需要在线路上增加串阻,通常大约 27 欧姆就可以了。

还需要将 D+ 线增加1.5K的 3.3V 上拉。如果您想动态连接/分离到总线,可以直接或通过 FPGA 上的引脚拉动它。确保永远不要下拉线路,上拉引脚的唯一有效输出是1'b1和1'bz。

2-no2usb

https://github.com/no2fpga/no2usb

该项目是Lattice众多拥簇的一员的项目,平台也是运行在ice40中,之前我也做了一个开发板(),奈何国内对这个感兴趣的不过,也就没怎么推广。

下面简单介绍一下这个项目。

概述

该 fpga 内核仅使用普通 FPGA CMOS IO 实现 USB 全速 SIU(Server Interface Unit)。

- 小巧高效(最初针对 ice40)

- 灵活,动态 EP 配置

- 单时钟域

该项目目前只运行在ice40芯片(Apple曾使用的)上,目前在适配ecp5(lattice)。

说明

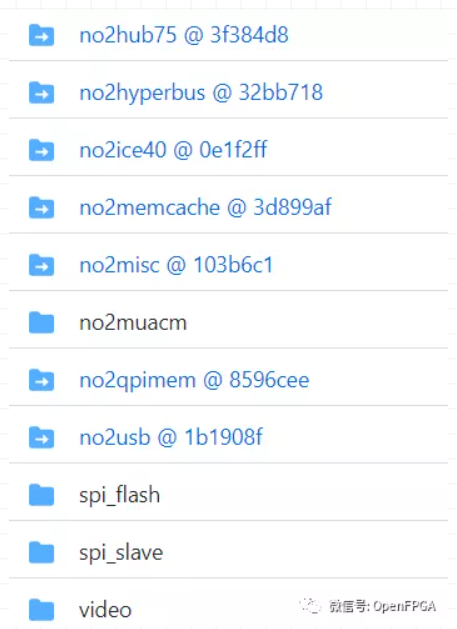

https://github.com/smunaut/ice40-playground/tree/master/cores

该项目里有很多可以参考的实例:

3-tinyfpga_bx_usbserial(USB转串口 SPI)

https://github.com/davidthings/tinyfpga_bx_usbserial

这个项目的起源也很有意思,ice40系列FPGA是使用SPI接口烧写程序的(类似JTAG),使用时需要一个USB转SPI芯片作为“JTAG”,常用的就是FT232/FT2232等,但是FTDI的芯片价格普遍比较贵(差不多和ICE40一样价格甚至更贵),本项目的起源就是为了节省这一芯片,使用FPGA本身实现USB-SPI。

项目起源地址

https://github.com/tinyfpga/TinyFPGA-Bootloader

简介

Lawrie Griffiths 深入研究了这段代码的"暗盒",并做了大量工作将其更改为 USB - SERIAL 桥接器,将用户视为串行端口,而不是 SPI 主机。他还创造了一些很好的例子,他的工作在这里:

https://github.com/lawrie/tiny_usb_examples

本项目针对以上两个项目做了一些改善。并且做了很多改善,不仅使用ICE40系列FPGA还适配了XIlinx A7 FPGA,同时ECP5(Lattice)也可以使用。

项目资源使用如下:

Info: Device utilisation:

Info: ICESTORM_LC: 1093/ 7680 14%

Info: ICESTORM_RAM: 2/ 32 6%

Info: SB_IO: 9/ 256 3%

Info: SB_GB: 8/ 8 100%

Info: ICESTORM_PLL: 1/ 2 50%

Info: SB_WARMBOOT: 0/ 1 0%项目的README中有详细的介绍及使用教程,这里就介绍的这里,毕竟不是完整的USB通信。

4-众多IP核

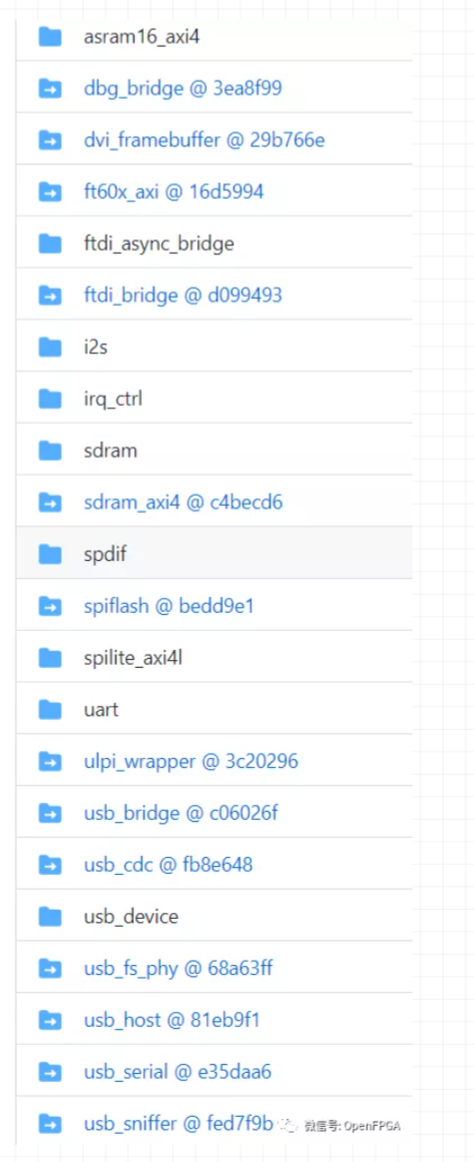

https://github.com/ultraembedded/cores

这个项目不仅不包括了USB(主要是USB1.1),还包括很多常见的低速接口-SPI UART I2S等等

每个IP都有完整的说明,自己去看吧,非常适合新手调试接口。

5-usb_cdc(设备类)

https://github.com/ultraembedded/core_usb_cdc

USB的CDC类是USB通信设备类 (Communication Device Class)的简称。CDC类是USB组织定义的一类专门给各种通信设备(电信通信设备和中速网络通信设备)使用的USB子类。

简介

该项目是一个简单的 USB 外设接口(设备)实现,可枚举为高速 (480Mbit/s) 或全速 (12Mbit/s) CDC-ACM 设备。

该 IP 具有用于输入和输出数据的简单 FIFO 接口(有效、数据、接受),以及用于连接到 USB PHY 的 UTMI 接口。

特征

- 高速或全速 USB CDC 设备。

- 硬件枚举 - 无需软件干预。

- UTMI PHY 接口

- 具有握手功能的简单 8 位数据输入/输出接口(符合 8 位宽 AXI4-Stream 接口)。

- 配置/要求(全速(12Mbit/s))

文件说明

Configuration / Requirements (Full Speed (12Mbit/s))

Top: usb_cdc_core

Clock: clk_i - 48MHz or 60MHz

Reset: rst_i - Asynchronous, active high

VID/PID can be changed in usb_desc_rom.v

Param: USB_SPEED_HS = "False"Configuration / Requirements (High Speed (480Mbit/s))

Top: usb_cdc_core

Clock: clk_i - 60MHz

Reset: rst_i - Asynchronous, active high

VID/PID can be changed in usb_desc_rom.v

Param: USB_SPEED_HS = "True"该项目在仿真下验证,在 FPGA 上针对 Linux、Windows 和 MAC OS-X 进行了测试。

6-www-asics-ws的项目

https://github.com/www-asics-ws

www-asics-ws项目中包含了USB1.1和USB2.0设备类USB IP。

usb1_device

- USB 1.1 兼容功能

- 支持硬件枚举

- 无需微控制器/CPU

- 基于 FIFO 的接口

- 用 Verilog 编写

- 完全可合成

- 仿真及硬件测试

usb2_dev

这是一个符合 USB 2.0 标准的内核。由于接口速度高,此内核需要外部 PHY。已开发出用于 USB 的行业标准 PHY 接口。该接口称为USB Transceiver Macrocell Interface或简称UTMI。USB 内核的主机接口符合 WISHBONE SoC 标准。有关 USB 标准和完整规范的更多信息,请访问www.usb.org。有关 WISHBONE SoC 的更多信息和完整规范,请访问www.opencores.org。UTMI 规范(以及其他各种有用的 USB 文件)可以从这里下载:https : //www.intel.com/content/www/us/en/io/universal-serial-bus/universal-serial-bus-specifications .html

参考意义不大,不能直接在FPGA中使用,需要搭配PHY使用。

7-usbhostslave

https://github.com/freecores/usbhostslave

该项目已使用 Quartus 6.0 成功编译并且USBHostSlave 已经在 SystemC 和 Altera Nios 开发套件 Cyclone 版中进行了测试。

整个项目文档说明很少,但是看提交记录该项目完成度很高,还是适合入坑。

优秀的 Verilog/FPGA开源项目介绍(四)- Ethernet

8-core_usb_sniffer

https://github.com/ultraembedded/core_usb_sniffer

这个内核是一个 HS/FS USB2.0 分析器(USB 总线嗅探器)。

内核监控 UTMI 接口,并通过 AXI-4 总线主接口将看到的流量记录到内存缓冲区。

可以连续提取日志格式(连续捕获模式),也可以在内存缓冲区已满时内核停止捕获(一次性模式)。

IP 的配置是使用 AXI4-Lite 从接口执行的。

该内核已用于生产USB 2.0 捕获设备(https://github.com/ultraembedded/usb2sniffer)这是实现的案例。

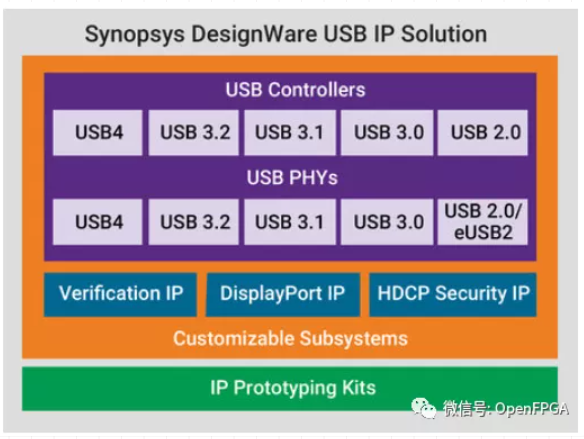

9-商业IP

https://www.synopsys.com/designware-ip/interface-ip/usb.html

商业IP肯定首推来自老牌大厂新思,新思科技在2018年推出基于HAPS-80 FPGA的硬件原型验证平台上部署了USB 3.2设备IP和主机IP。这些FPGA硬件原型验证平台在FinFET工艺节点的FPGA中使用了USB PHY。解决方案如下:

有需要的可以去上面的网站了解,需要money的IP,所以我就不过多介绍了,个人也不会选用,大公司自然有销售对接。

以上就是今天推荐的项目,这里建议第一个和第五个项目可以入坑,其他看自己需求。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐